Fターム[5F033QQ98]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 空気、大気に晒さない連続処理 (330)

Fターム[5F033QQ98]に分類される特許

21 - 40 / 330

処理方法および記憶媒体

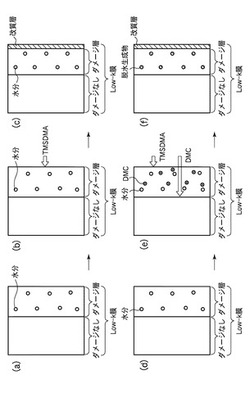

【課題】低誘電率膜のダメージ回復処理を行う際に、比誘電率やリーク電流値を低く維持しつつ内部の水分を除去することができる処理方法を提供すること。

【解決手段】被処理基板に形成された、表面部分にダメージ層を有する低誘電率膜に回復処理を施すにあたり、その分子が、低誘電率膜のダメージ層の内部に浸透できる程度に小さく、ダメージ層内の水分を除去することが可能な第1処理ガスと、ダメージ層の表面に疎水性で緻密な改質層を形成する第2処理ガスとを低誘電率膜のダメージ層に作用させる。

(もっと読む)

成膜方法およびCu配線の形成方法

【課題】被処理基板を加熱してトレンチやホールの間口部のオーバーハングを抑制しつつ金属膜を成膜するとともに、成膜後に速やかに被処理基板の温度を低下させることができる成膜方法を提供すること。

【解決手段】載置台を低温に保持して、載置台上に被処理基板を吸着させずに載置する工程と、プラズマ生成ガスのプラズマを生成し、載置台に高周波バイアスを印加した状態で、被処理基板にプラズマ生成ガスのイオンを引きこんで被処理基板を予備加熱する工程と、ターゲットに電圧を印加して金属粒子を放出させ、プラズマ生成ガスのイオンとともにイオン化した金属イオンを被処理基板に引きこんで金属膜を形成する工程と、被処理基板を低温に保持された載置台に吸着させ、載置台と被処理基板との間に伝熱ガスを供給して被処理基板を冷却する工程とを有する。

(もっと読む)

銅結線のシード層の処理方法および処理装置

【課題】ダマシンプロセスによる銅の充填において、銅シード層の完全性を失わないように行う。

【解決手段】誘電体層に半導体結線形状を形成するための方法は、誘電体層上に形成された形成されたバリア層上、および誘電体層のエッチング形状内に、銅シード層を蒸着する工程を含む。次いで、銅シード層は、酸化された層を銅シード層から除去するために処理を施される。次いで、その方法は、処理された銅シード層上に銅充填層を電気メッキする工程に進む。銅充填層は、誘電体層のエッチング形状を満たすよう構成されている。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

成膜方法及び半導体装置の製造方法

【課題】ポリイミド膜に対して高い密着性を有するコバルト膜を成膜する方法を提供する。

【解決手段】成膜装置100の処理容器1内で、処理容器1内にCOガスを導入しながら、ポリイミド膜81が形成されたウエハWを110℃以上400℃以下の温度で加熱し、ポリイミド膜81を熱処理する。熱処理によって、ポリイミド膜81中の分子が熱分解し、膜密度が減少するとともに、表面粗度が大きくなる。その後、処理容器1内に成膜原料であるCo2(CO)8を導入してCVD法によりポリイミド膜81上にコバルト膜83を堆積させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孤立パターンに銅の化合物が析出するのを抑制する半導体装置の製造方法と、半導体装置とを提供する。

【解決手段】半導体装置では、素子・基板層ESLの低誘電率膜LOW1、ファイン層FLの極低誘電率膜ELK1等およびセミグローバル層SGLの低誘電率膜LOW2等のそれぞれの開口部に形成されるアライメントマークAMおよび重ね合わせ検査マークKMが、半導体基板SUBに形成された所定の導電型の不純物領域IRに電気的に接続されて、アライメントマークAMおよび重ね合わせ検査マークKMが接地電位に固定されている。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっ

ても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コン

タクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹

脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、

パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

半導体装置、液晶モジュール、電子機器及び配線

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

ラジカルクリーニング方法及びラジカルクリーニング装置

【課題】Si基板上に形成されたSiO2膜を除去するラジカルクリーニング方法であって、ラジカルクリーニングを行う際に生成する残留生成物も除去することができるラジカルクリーニング方法を提供する。

【解決手段】プラズマによりHラジカル生成用ガスを分解してHラジカルを生成させ、このHラジカルとNF3ガスを反応させてN、F及びHからなるラジカルを生成するNFHラジカル生成工程と、真空槽内で、Si基板上に形成されたSiO2膜に前記N、F及びHからなるラジカルを照射することにより前記SiO2膜を除去するエッチング工程と、真空槽内で、前記エッチング工程で前記Si基板上に生成した残留生成物にマイクロ波を照射することにより、前記残留生成物を加熱して蒸発させて除去する残留生成物除去工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】パターン疎密差の影響を受けないハードマスク形成法を提供する。

【解決手段】基板101上に、第1から第3の膜111,112,113およびレジスト層114を形成した後、疎部R1と密部R2が存在するパターンを前記レジスト層に形成して前記第3の膜をエッチングする。次に、前記第3の膜及び前記レジスト層をマスクとして、密部R2内では前記第2の膜が残存するが、疎部R1内では前記第1の膜が露出するまで、前記第2の膜を除去する。その後CXFYHZガスを使用して、第5の膜115を、疎部R1内に露出した前記第1の膜上に第1の膜厚T1で形成し、密部R2内に残存する前記第2の膜上には膜厚T1よりも薄い第2の膜厚T2で形成する。膜厚T1の前記第5の膜で疎部R1内に露出した前記第1の膜を保護しながら密部R2内に残存する前記第2の膜を除去し、最後に、前記第3から第5の膜を除去して前記第2の膜をハードマスクとする。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

配線形成方法

【課題】下層配線層と配線シード層との密着性を低下させないで高く維持することが可能な配線形成方法を提供する。

【解決手段】下層配線層4と絶縁性バリヤ層6と層間絶縁膜8と上層配線層が順次積層された被処理体に対して上層配線層と、連通配線層16とを形成する配線形成方法において、絶縁性バリヤ層を残した状態で連通ホール9Bを形成し、連通ホール内に犠牲膜を埋め込み、トレンチ9Aを形成するパターンマスク62を形成する前処理工程と、トレンチを形成するトレンチ形成工程と、犠牲膜60とパターンマスクとをアッシングするアッシング工程と、トレンチ内と連通ホール内に熱処理によりバリヤ層10を形成するバリヤ層形成工程と、異方性エッチングにより連通ホールの底部のバリヤ層と絶縁性バリヤ層とを除去する異方性エッチング工程と、配線シード層12を形成する配線シード層形成工程とを有する。

(もっと読む)

21 - 40 / 330

[ Back to top ]