Fターム[5F033QQ98]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 空気、大気に晒さない連続処理 (330)

Fターム[5F033QQ98]に分類される特許

61 - 80 / 330

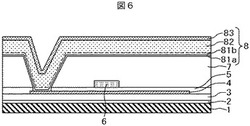

表示装置

【課題】TFTと接続するソース電極あるいはドレイン電極のスルーホールにおけるコンタクト抵抗を減少させ、表示装置の動作効率を向上させる。

【解決手段】スルーホールにおいて、TFTのソース部とソース電極8が接続している。ソース電極8は、バリヤメタル、Al合金82、キャップメタル83の3層から形成されている。バリヤメタルは半導体層と接触する下層81aとAl合金と接触する上層81bとに分かれている。バリヤメタルの下層81aをスパッタリングして形成した後、熱処理し、その後、ベースメタルの上層81b、Al合金82、キャップメタル83を連続してスパッタリングによって形成する。Al合金82と接触するバリヤメタルの上層81bは酸化されていないので、スルーホールにおけるコンタクト抵抗の上昇を防止することが出来る。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

半導体装置の製造方法

【課題】配線密度の高い領域に発生するエロージョンを抑えることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、配線8aおよび配線8aよりもパターンの密度が低い配線8bを、第1の絶縁膜3中の高密度領域4aおよび低密度領域4bにそれぞれ形成する工程と、第1の絶縁膜3の高さを下げて配線8a、8bの上部10a、10bを露出させる工程と、低密度領域4bにおける上面の最低高さが配線8a、8bの上面の高さよりも低くなるように、第1の絶縁膜3の上面、および上部10a、10bの表面を覆う第2の絶縁膜11を形成する工程と、第2の絶縁膜11上に第3の絶縁膜12を形成する工程と、配線8a、8b、および第3の絶縁膜12の研磨レートが第2の絶縁膜11の研磨レートよりも高い条件の下で第3の絶縁膜12、第2の絶縁膜11、配線8a、8bを研磨して平坦化させる工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

半導体装置の製造方法

【課題】金属配線に用いられるAlにCuを添加した合金導電膜の膜質を改善して、ストレスマイグレーション耐性を向上させること。

【解決手段】本発明の実施形態に係る半導体装置の製造方法は、Al−Cu膜の成膜後に予め決められた温度変化で冷却する工程が存在する。これにより、Al−Cu膜は、結晶粒と粗密差が生じる領域が従来例よりも狭くなってヒロックの発生が抑制される膜質に改善される。その後に続く製造工程における熱履歴によってヒロックの発生が抑制され、その結果、このAl−Cu膜を有する配線層から形成された配線のストレスマイグレーション耐性が向上する。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 層間絶縁膜内の水分などによるバリアメタルの腐食を防止し、銅配線の信頼性の低下及び抵抗値の上昇を抑制し得る半導体装置、及びその製造方法を提供する。

【解決手段】 メチル基を含有する層間絶縁膜32内に配線溝37を形成する。配線溝37が形成された絶縁膜32に紫外線又は電子線を照射した後に、メチル基を有するガスを用いて絶縁膜の露出面を疎水化する。配線溝37の疎水化された内面に沿ってバリアメタル層41を形成し、該バリアメタル層41を介して配線溝37を銅配線43で充填する。一実施形態において、配線溝37はメタルハードマスク47を用いて絶縁膜32をエッチングすることにより形成され、絶縁膜32への紫外線又は電子線の照射は、メタルハードマスク47を残存させた状態で行われる。

(もっと読む)

半導体装置の製造方法

【課題】銅配線を有する半導体装置において、銅配線の配線抵抗やコンタクトと抵抗を増加することなく信頼性を向上しうる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に形成された開口部内に、銅に対して拡散防止作用を有する第1金属材料を含む第1の膜と、酸素を含有する銅膜を含む第2の膜と、銅と、酸素と結合することにより銅に対して拡散防止作用を有する第2金属材料とを含む第3の膜と、銅を主材料とする第4の膜とを含む配線層を形成した後、熱処理により、絶縁膜と第4の膜との間に、第1金属材料、第2金属材料及び酸素を含むバリア層を形成する。

(もっと読む)

半導体装置の製造方法

【目的】Cu配線寿命の劣化と絶縁膜の絶縁性劣化を共に低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、チャンバ内面にシリコン(Si)膜を表面層とする多層膜を形成する工程(S102)と、前記多層膜が内面に形成されたチャンバ内に、表面に銅(Cu)配線と絶縁膜とが形成された基板を配置して、希ガスプラズマ処理を行なう工程(S106)と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】信頼性の高い半導体集積回路装置の製造プロセスを提供する。

【解決手段】銅ダマシン配線プロセスのバリアメタル膜のタンタル系積層膜に関し、スパッタリング成膜チャンバ内のシールド内面に、比較的薄い窒化タンタル膜およびタンタル膜が交互に成膜されるが、この連続成膜プロセスを断続的に繰り返すと、膜の内部応力により剥がれて、異物やパーティクルの原因となる。この異物やパーティクルの防止のため、繰り返し、成膜するに際して、所定の間隔を置いて、厚い膜厚を有する異物防止用タンタル膜をチャンバの実質的な内壁に成膜する工程を設ける。

(もっと読む)

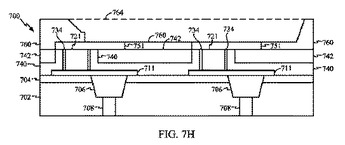

磁気トンネル接合を含む上部および下部電極を有するデバイスの製造および統合

電子デバイス製造プロセスは、下部電極層を堆積する段階を含む。次いで、電子デバイスが下部電極層上に製造される。下部電極層をパターニングする段階は電子デバイスを製造する段階後に、上部電極をパターニングする段階とは個別のプロセスで実施される。第1誘電体層は次いで、電子デバイスおよび下部電極層上に堆積され、上部電極層がそれに続く。上部電極は次いで、下部電極とは別のプロセスでパターン化される。上部および下部電極の別々のパターニングにより、電子デバイス間の誘電体材料におけるボイドが減少することによって収率が向上する。その製造プロセスが適切な1つの電子デバイスが、磁気トンネル接合(MTJ)である。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

半導体装置の製造装置および配線パターンの形成方法

【課題】大量生産上、大型の基板に適している液滴吐出法を用いたパターン形成装置を

備えた半導体装置の製造装置を提供する。

【解決手段】本発明では、液滴吐出法を用いたパターン形成装置と、加熱処理室をそれぞ

れ複数設置し、それぞれを一つの搬送室と連結させたマルチチャンバー方式とし、吐出と

焼成とを効率よく行って生産性を向上させる。パターン形成装置にブロー手段を設け、着

弾直後にガスの吹きつけを基板の走査方向(或いは吐出ヘッドの走査方向)と同じ方向に

行い、ガス流路中に加熱ヒータを設けて局所的に焼成を行う。

(もっと読む)

半導体集積回路装置の製造方法

【課題】主にアルミニウム系通常配線を有するLSIの製造工程BEOLプロセスでは、配線の信頼性に関して、EM耐性およびSM耐性の向上が特に重要である。アルミニウム系配線に関する不良の中でも、配線メタル膜の膨張や欠けの発生は、EM耐性およびSM耐性を大きく劣化させる要因となる。

【解決手段】本願発明は、層間絶縁膜を成膜するプラズマCVDチャンバのウエハ・ステージ上に於いて、アルミニウム系配線メタル膜のパターニングの後であって層間絶縁膜の成膜前に、ウエハのデバイス面に対して、不活性ガスを主要な成分の一つとして含む雰囲気下、アルミニウム系配線メタル膜および層間絶縁膜の成膜温度よりも高いウエハ温度において、プラズマ・アニール処理を実行することにより、配線メタル層の側壁部の付着物が完全に除去され、膨張不良の原因が取り除かれ、更に、不動態化の進行、ストレス開放等により、欠け不良を抑制するものである。

(もっと読む)

高アスペクト比のフィーチャーへのタングステン堆積方法

【課題】高アスペクト比のフィーチャーをタングステン含有材料で充填する。

【解決手段】部分的に製造された半導体基板上の高アスペクト比のフィーチャーをタングステン含有材料で充填する方法が提供される。ある実施形態においては、当該方法は高アスペクト比のフィーチャーにタングステン含有材料を部分的に充填する工程とフィーチャー空洞から部分的に充填された材料を選択的に除去する工程とを有する。これらの方法を用いて処理された基板においては、高アスペクト比のフィーチャーに充填されたタングステン含有材料のステップカバレッジが改善され、シームの大きさが低減する。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

成膜方法

【課題】 キャップ膜、もしくはバリア膜として使用することが可能な膜を、形成するか形成しないかを選択することが可能となる成膜方法を提供すること。

【解決手段】 銅を使用している配線と絶縁膜とが表面に露出している基板に対してマンガン含有膜を成膜する成膜方法であって、銅を使用している配線上に、マンガン化合物を用いたCVD法を用いてマンガン含有膜を形成する工程(ステップ2)を備える。

(もっと読む)

61 - 80 / 330

[ Back to top ]