Fターム[5F033RR12]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 不純物を含むもの (1,419)

Fターム[5F033RR12]の下位に属するFターム

Fターム[5F033RR12]に分類される特許

61 - 80 / 141

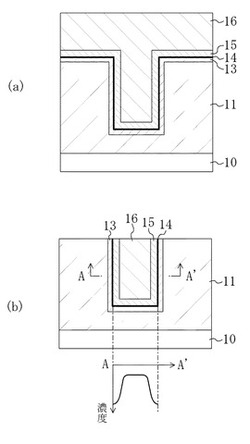

埋め込み配線の形成方法

【課題】配線抵抗が低く、EM耐性及び信頼性に優れた埋め込み配線の形成方法を提供することにある。

【解決手段】半導体基板10上に形成された絶縁層11内に溝12を形成した後、溝12の側面及び底面を覆うように、絶縁層11上にALD法でバリアメタル層13を形成し、その表面に、イオン注入法またはALD法により不純物層14、17を形成する。その後、バリアメタル層13と不純物層14、17とを合金化した後、溝12内にCuシード層15及びCuメッキ層16からなる埋め込み配線層を形成し、然る後、合金化されたバリアメタル層13内の不純物元素を埋め込み配線層内に熱拡散させる。

(もっと読む)

紫外線による材料キュアのための半導体処理装置及び方法

【課題】紫外線キュアの効率を向上させ、キュア済みの低誘電率膜の膜特性を改善する。

【解決手段】低誘電率材料を半導体処理中に処理チャンバ内でキュアする方法が与えられる。該低誘電率材料は紫外線が照射されてキュアされる。処理チャンバ内の雰囲気は、紫外線の照射中、25から10000ppmの酸素濃度を有する。酸素は、低誘電率材料中の-Si-H基及び-Si-OH基の形成を制限し、それにより、低誘電率材料中の吸湿及び酸化が減少する。

(もっと読む)

半導体集積回路装置

【課題】

ビルディングブロック方式では、電源ライン及びグランドラインの配置によって、半導体集積回路装置の微細化が困難であった。

【解決手段】

アナログ信号処理機能を担う電子回路ブロックが集積化された半導体集積回路装置であって、電源ラインは、電子回路ブロックを構成する半導体素子上の領域を含んで配置され、グランドラインは、電子回路ブロック間に位置する分離領域上に形成され、グランドラインは、コンタクト孔において分離領域とコンタクトされる。

(もっと読む)

半導体装置の製造方法

【課題】耐熱性や絶縁性の劣化などの不良の発生が抑えられた絶縁膜と、金属配線とを備えた半導体装置の製造方法を提供する。

【解決手段】基板上に吸湿性を有する絶縁膜102を形成し、絶縁膜にダミーコンタクトホールとコンタクトホールとを形成する。基板を熱処理して絶縁膜に含まれる水分を脱離させた後、金属膜で構成されるコンタクト103およびダミーコンタクト110をそれぞれ形成する。熱処理により、コンタクトホールおよびダミーコンタクトホールを通して絶縁膜中の水分を脱離させることができる。

(もっと読む)

半導体装置の多層配線構造及び多層配線を有する半導体装置の水分検出方法

【課題】 多層配線を有する半導体装置において配線層内の水分の有無を直接評価することができる配線構造及び多層配線を有する半導体装置の水分検出方法を実現する。

【解決手段】 半導体装置1の多層配線構造において、第3配線層33より腐食されやすい材料により形成された薄膜抵抗体20a、20bが第3配線層33に配置され、薄膜抵抗体20a、20bの抵抗値を測定可能に構成されているため、水分の侵入などにより第3配線層33内に水分が存在する場合には、水分が第3配線層33内を移動して薄膜抵抗体20a、20bに到達し、薄膜抵抗体20a、20bが腐食されて抵抗が急増するので、薄膜抵抗体20a、20bの抵抗値を測定することにより第3配線層33内の水分の有無を直接検出することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に貫通配線層を形成する際の貫通孔底部での壁状付着物や有機マスク残渣の発生を防ぐことにより、貫通接続部の接続不良や機械的信頼性が改善された半導体装置を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3よりも小径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が開口4aを覆い形成されている。また、貫通孔3内および半導体基板2の裏面に第2の絶縁層6が被覆され、その上には拡散防止機能を有する高抵抗金属からなる金属マスク層7が形成されている。第2の絶縁層6および金属マスク層7は、第1の絶縁層4の開口4aと同径の開口6a、7aを有している。さらに、貫通孔3内に第2の配線層8が充填・形成され、この第2の配線層8は第1の絶縁層4および第2の絶縁層6の開口4a、6aを介して第1の配線層5に内接している。

(もっと読む)

銅膜作製方法

【課題】下地層との密着性に優れた銅膜を製造する方法の提供。

【解決手段】成膜対象物上に下地層を形成した後、この下地層を水素ガス雰囲気中で熱処理し、次いでその上に銅膜を作製する。このように銅膜を作製した後、さらに水素ガス雰囲気中で熱処理を行なう。

(もっと読む)

半導体デバイスの製造方法

【課題】低誘電率材料からなる層間絶縁膜の特性を回復することにより、層間絶縁膜中に形成される配線の信号伝達速度の遅延特性やリーク電流特性を向上させる半導体素子の製造方法を提供する。

【解決手段】半導体基板上に低誘電率材料からなる絶縁膜17を堆積し、RIEにより配線溝を形成する。この絶縁膜に真空中でUV照射を行い、エッチングにより生じたダメージ層を回復し、誘電率と屈折率を下げる。この溝に拡散防止膜19aとCuを埋め込み、配線とする。

(もっと読む)

半導体装置、およびその製造方法

【課題】ビアの径を調節するスペーサ膜と、ビア間絶縁膜上に形成されたエッチングストッパ膜を有し、スペーサ膜とエッチングストッパ膜の界面におけるリーク電流の発生を抑えた半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、表面に半導体素子を有する半導体基板と、前記半導体基板上に形成された配線と、前記配線の下側に接続されるビアと、前記ビアと同じ層に形成された第1の絶縁膜と、前記第1の絶縁膜と前記配線との間、および前記第1の絶縁膜と前記ビアとの間に一体に形成された第2の絶縁膜と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ダマシンゲートプロセスにおいて、ゲート電極用溝形成時に層間絶縁膜が後退せず、短絡の原因となる導電層の残渣が発生しない半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10にダミーゲート絶縁膜12とダミーゲート電極13を形成し、ダミーゲート電極をマスクとして基板にソース・ドレイン領域19を形成し、酸化シリコンよりフッ酸耐性を有する絶縁性材料によりダミーゲート電極より厚い膜厚でダミーゲート電極を被覆して第1絶縁膜21を形成し、その上に第1絶縁膜と異なる絶縁性材料で第2絶縁膜22を形成し、第2絶縁膜の上面から第1絶縁膜の頂部、さらにダミーゲート電極が露出するまで第1絶縁膜と第2絶縁膜とを平坦化除去し、ダミーゲート電極及びダミーゲート絶縁膜を除去し、得られるゲート電極用溝の底部にゲート絶縁膜を形成し、その上にゲート電極を形成し、電界効果トランジスタとする。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの下の層間絶縁膜にクラックが入るのを防ぎ、ボンディングパッドと同層に形成された上層配線を微細化することができる半導体装置及びその製造方法を提供する。

【解決手段】層間絶縁膜17上に第1金属膜20を形成する。第1レジストをマスクとして第1金属膜20を異方性エッチングする。残された第1金属膜20を覆うように層間絶縁膜17上に、第1金属膜20よりもヤング率が低い第2金属膜24を形成する。層間絶縁膜17上に第1金属膜20が存在する領域及び第1金属膜20が存在しない領域の一部において第2金属膜24上に第2レジストを形成する。第2レジスト33をマスクとして第2金属膜24を異方性エッチングして、第1金属膜20と第2金属膜24とを有するボンディングパッドと、第2金属膜24を有するが第1金属膜20を有しない上層配線22とを形成する。

(もっと読む)

半導体装置

【目的】多層配線において配線層間の剥がれ耐性を向上させた装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、基板200上に多層配線構造で形成され、最上層に電極パッド30を有する実効配線10と、多層配線構造内で実効配線10の周囲を取り囲むように形成されたビアリング20と、多層配線構造の最終表面を保護する積層保護膜PFと、積層保護膜PFと接する位置であって実効配線10が形成される領域とチップ領域端との間に形成された、電極パッド30を構成する導体とビアリング20を構成する導体とのいずれよりもヤング率が大きい膜パターンで構成されるクラックストッパ膜40と、を備えたことを特徴とする。

(もっと読む)

成膜方法及び成膜装置

【課題】Mn含有膜やCuMn含有合金膜等を、CVD等の熱処理によって形成することにより、微細な凹部でも、高いステップカバレッジで埋め込むことができ、しかも、同一の処理装置で連続的な処理を行うようにして装置コストを大幅に低減化することができる成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器14内で、遷移金属を含む遷移金属含有原料ガスと酸素含有ガスとにより被処理体Wの表面に、熱処理により薄膜を形成する。これにより、例えばMn含有膜やCuMn含有合金膜等を、CVD等の熱処理によって形成する際に、微細な凹部でも、高いステップカバレッジで埋め込むことが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスク除去プロセスにおいて、低誘電率絶縁膜の誘電率の上昇を伴うダメージを低減させると共に加工形状を安定させることを目的とする。

【解決手段】ハードマスクを用いて配線溝を形成するプロセスからなる半導体装置の製造方法において、メタルハードマスク107を用いて配線溝111の形成を行うことで配線溝111の形状を安定化させることができると共に、配線溝111にTaNやCuを形成する前にあらかじめメタルハードマスク107の一部または全てを除去することで低誘電率膜表面の誘電率の上昇を伴う損傷が低減されて配線間のリーク電流を低減させることができ、信頼性の高い半導体装置を実現できる。

(もっと読む)

低誘電率の誘電材料の損傷を低減したマスキング材料の除去方法

【課題】低誘電率の材料の露出表面への損傷を最小化しながら、露出した低誘電率の材料を有する基板からマスキング材料を取り除く方法が提供される。

【解決手段】一実施形態において、基板からマスキング材料を取り除くための方法は、露出した低誘電率の材料及びマスキング材料を有する基板を提供し、第1の期間、還元化学反応物質から形成された第1のプラズマに前記マスキング材料を曝し、第2の期間、酸化化学反応物質から形成される第2のプラズマにマスキング材料を曝すことを含む。これらのステップは必要なだけ繰り返され、また、反対の順序に行われるかもしれない。選択的に、少なくとも1つの希釈ガスが酸化化学反応物質に追加されるかもしれない。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板に貫通配線層を形成する際の貫通孔底部での配線層の薄膜化が防止され、貫通接続部の接続不良が改善された半導体装置を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3と同径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が形成されている。また第1の配線層5の近傍に、貫通孔3とその内壁面等に形成された第3の絶縁層8および貫通孔3内に充填・形成された第3の配線層9から成る貫通接続部が形成されている。そして、この貫通接続部に内接された第2の配線層7と第1の配線層5とが電気的に接続され、貫通孔3の内壁面と第1の配線層5との間に第2の絶縁層6が介在し、第1の配線層5と貫通孔3内に充填・形成された第3の配線層9とが離間されるように構成されている。

(もっと読む)

半導体デバイスのデュアルストレスライナ上方の付加層を使用することによって向上するNチャネルトランジスタのトランジスタパフォーマンス

それぞれ固有応力が異なる誘電ライナ(230、240)をパターニングした後に、窒化シリコンなどの付加的誘電材料(260)を形成することによって、Pチャネルトランジスタ(220B)のパフォーマンスを実質的に低下させずにNチャネルトランジスタ(220A)のパフォーマンスを著しく向上させることができる。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の貫通配線部において、貫通孔底部での絶縁層の被覆性が向上され、電気的絶縁性の低下や接続不良が改善された半導体装置を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3と同径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が開口4aを覆い形成されている。また、貫通孔3内および半導体基板2の裏面に第2の絶縁層6が被覆されている。第2の絶縁層6は、第1の配線層5と内接するように形成され、内接部に第1の絶縁層4の開口4aよりも小径の開口6aを有している。さらに、貫通孔3内に第2の配線層7が充填・形成され、この第2の配線層7は第2の絶縁層6の開口6aを介して第1の配線層5に内接している。

(もっと読む)

半導体装置及びその製造方法

【課題】 nチャネル導電型電界効果トランジスタ及びpチャネル導電型電界効果トランジスタの電流駆動能力の向上を図る。

【解決手段】 半導体基板の一主面の第1の領域にチャネル形成領域が構成されたnチャネル導電型電界効果トランジスタと、前記半導体基板の一主面の第1の領域と異なる第2の領域にチャネル形成領域が構成されたpチャネル導電型電界効果トランジスタとを有する半導体装置であって、前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力と、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力とが、各々で異なっている。前記nチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は引っ張り応力であり、前記pチャネル導電型電界効果トランジスタのチャネル形成領域に発生する内部応力は圧縮応力である。

(もっと読む)

61 - 80 / 141

[ Back to top ]