Fターム[5F033RR12]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 不純物を含むもの (1,419)

Fターム[5F033RR12]の下位に属するFターム

Fターム[5F033RR12]に分類される特許

121 - 140 / 141

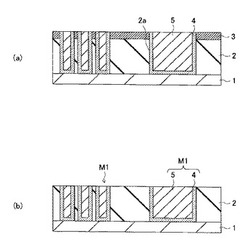

半導体装置の製造方法

【課題】バリアメタルがない場合であっても、配線の平坦性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本実施例の半導体装置の製造方法は、半導体基板1上に層間絶縁膜2を形成し、層間絶縁膜2上に金属を含むメタルマスク3を形成し、メタルマスク3および層間絶縁膜2の一部をエッチングして、メタルマスク3および層間絶縁膜2にパターン溝2aを形成し、パターン溝2a内を埋め込むように、層間絶縁膜2上に導電層5を形成し、パターン溝2a内に導電層5を残すように、層間絶縁膜2上の余剰の導電層5を研磨する。

(もっと読む)

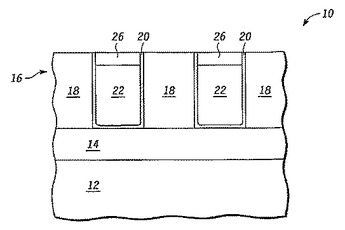

キャップ層を半導体素子の上に形成するための方法

半導体素子を形成する方法は、複数の空洞(15)を有するパターニング済み誘電体(18)を能動回路の上に形成する工程を含む。拡散バリア(20)をパターニング済み誘電体(18)の上に形成する。導電層(22)を複数の空洞の中の拡散バリアの上に形成する。導電層を、導電層が誘電体の上部表面の下方に位置するようにエッチバックして、後退領域(24)を、複数の空洞の中の導電層の上に形成する。次に、後退領域にキャップ膜(26)を充填する。キャップ膜及び拡散バリアを除去すると、非常に平滑な平坦化表面が得られる。非常に平滑な平坦化表面を形成することにより、複数の導体の間のリーク電流を低減する。  (もっと読む)

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な薄膜トランジスタ及びその作製技術を提供することを目的とする。また、薄膜トランジスタを構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】薄膜トランジスタが有する配線や電極パターンは、第1の領域及び第2の領域を有する絶縁表面上に設けられた配線層と、配線層に接する電極層とを有し、前記配線層は前記第2の領域に設けられ、電極層は第1の領域に設けられ、電極層及び配線層に対するぬれ性は、前記第1の領域より前記第2の領域が高い領域に設けられる。

(もっと読む)

表面活性化剤を用いる金属含有フィルムの原子層蒸着

表面上に金属含有フィルムを形成させる原子層蒸着法が提供される。これらの方法は、これらの方法の最も広い態様において、(a)表面を表面活性化剤にさらして表面上に表面活性化錯体の蒸着物を形成させる工程と、

b)表面活性化錯体の蒸着物を金属前駆体にさらして表面上に金属錯体の蒸着物を形成させる工程と、

c)蒸着させた金属錯体を還元剤と反応させて、表面上に酸化物を含まない金属含有フィルムを形成させる工程とを含んでなり、ここで、金属はCo、Ni、Pt、Pd、IrおよびWよりなる群から選択される。

(もっと読む)

電子デバイスの製造方法

【課題】ビアホールが形成された低誘電率膜の上に、化学増幅型レジストを用いたリソグラフィーにより、所望のトレンチパターンを持つレジスト膜を形成できるようにする。

【解決手段】炭素含有シリコン酸化膜5にビアホ−ル8を形成した後、少なくともビアホ−ル8の壁面に露出した炭素含有シリコン酸化膜5に電子受容体を吸着させ又は注入する。その後、化学増幅型レジストを用いたリソグラフィーにより、ビアホ−ル8が形成された領域を含むトレンチ形成領域に開口部を持つレジストパターン10aを形成する。

(もっと読む)

半導体集積回路装置

【課題】 ヒューズ素子に接続される保護回路の占有面積を抑制する半導体集積回路装置を提供する。

【解決手段】 表面にMOSFET12等の半導体素子が形成されたシリコン基板11、シリコン基板11の表面外側に形成された複数の第1乃至第10配線層23a〜23g、この半導体素子に正対する位置を避けたシリコン基板11の外側に形成され、配線層23a〜23gを介して第1の端子を接地されたヒューズ素子28、シリコン基板11とヒューズ素子28の間に形成された層間絶縁膜31及び層間絶縁膜31より機械的強度の弱いポーラス絶縁膜33、及び、ポーラス絶縁膜33よりシリコン基板11に近い側且つヒューズ素子28に正対する位置に形成され、配線層23d〜23gを介して一端をヒューズ素子28の第2の端子に接続され、配線層23aを介して他端をMOSFET12に接続された配線抵抗25を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】 ボラジン系化合物の絶縁膜を用いて、絶縁材料と配線材料との間の密着性や、機械強度等の特性が向上された半導体装置およびその製造方法を提供すること

【解決手段】 凹部に第1の導体層が埋め込まれた第1の絶縁層と、第1の絶縁層上に形成されたエッチングストッパー層と、エッチングストッパー層上に形成された第2の絶縁層と、第2の絶縁層上に形成された第3の絶縁層と、第2の絶縁層と第3の絶縁層との凹部に埋め込まれた第2の導体層と、を含む半導体装置であって、第2の絶縁層および第3の絶縁層は、炭素含有ボラジン化合物を原料として化学的気相反応成長法によって形成され、第3の絶縁層の炭素含有率が、第2の絶縁層の炭素含有率よりも小さいことを特徴とする半導体装置。

(もっと読む)

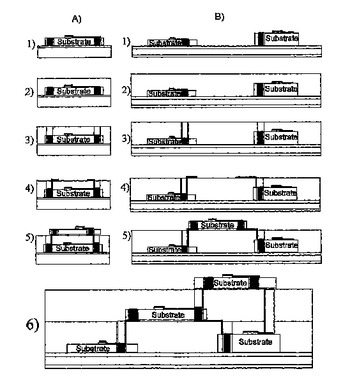

チップの架橋接続

システムは、第1半導体デバイスと第1電気接続とを有する第1チップ、第2半導体デバイスと第2電気接続とを有する第2チップ、および第3半導体デバイスと第3電気接続とを有する第3チップを有し、第3チップは、第1および第2チップの上面にスタックされ、第1および第2チップのそれぞれの少なくとも一部分を物理的に架橋し、前記第1および第2チップに接続される。  (もっと読む)

(もっと読む)

ビアホール形成方法、及び半導体装置

【課題】 ビアホール加工に際して開口チェックが実行でき、オーバーエッチングを出来るだけ少なくすると共に、エッチング不足を防止できる半導体デバイス製造技術を提供することである。

【解決手段】 第1の配線パターンと第2の配線パターンとを接続する為に用いられる所定パターンのビアホールを形成する為の方法であって、

前記第1の配線パターンを形成した後、該第1の配線パターン上に絶縁層を形成する絶縁層形成工程と、

前記絶縁層形成工程の後、前記第1の配線パターンに適合する前記所定パターンのビアホールを前記絶縁層に形成する適合ビアホール形成工程と、

前記絶縁層形成工程の後、前記第1の配線パターンに一部適合・一部不適合の不適合ビアホールを形成する不適合ビアホール形成工程と、

前記不適合ビアホール形成工程で形成されたビアホールを調べることによって前記適合ビアホール形成工程を制御する制御工程

とを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置における品質および信頼性の向上を図る。

【解決手段】 ポリイミド樹脂からなるテープキャリア1と表面にポリイミド樹脂の保護膜2eを有した半導体チップ2の接続において、テープ本体1aの半導体チップ2の電極列より内側の領域にダミーパターン1dが設けられていることにより、テープ本体1aをダミーパターン1dが支えるため、テープ本体1aと半導体チップ2の表面との間に隙間を確保できる。これにより、封止工程でアンダーフィル材8を充填する際に、テープ本体1aと半導体チップ2の間の未充填部分の発生を防ぐことができ、ボイドが形成されることを防止できる。その結果、ポリイミド樹脂の保護膜2eの剥離や、チップクラックの発生を阻止することができ、半導体装置の品質および信頼性の向上を図ることができる。

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置、制御プログラム及びコンピュータ記憶媒体

【課題】炭素含有シリコン酸化膜からなる低誘電率絶縁膜とレジストとの選択比を向上させることができるとともに、微細径、高アスペクト比のホールであっても、内壁面が良好な状態で形成することのできるプラズマエッチング方法等を提供する。

【解決手段】半導体ウエハWの表面には、下側から順に、SiCN膜101、SiCOH膜102、TEOS膜103、反射防止膜104、マスクとしてのレジスト膜(ArFレジスト)105が形成されている。図1(B)に示す状態から、所定のエッチングガス、例えば、CF4 /CH2 F2 /N2 /O2 等の混合ガス(Ar等の希ガスを含まない)を使用したプラズマエッチングにより行い、SiCOH膜102をエッチングし、図1(C)に示すように、ビアホール107を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 スルーホール等の凹部において、ボイドフリーな膜を形成することを目的とする。

【解決手段】 半導体基板上に形成された、スルーホールを有する絶縁層と、スルーホール内に形成された導電層において、導電層内部に埋め込まれた埋め込み絶縁膜を形成し、ボイドフリーの膜とする。

(もっと読む)

半導体装置の設計方法および信頼性評価方法

【課題】 所望の信頼性を有する半導体装置を設計する。

【解決手段】 半導体装置100は、第一の配線112上にビア124が形成された構成を有する。半導体装置100の設計方法は、銅配線(配線金属膜110)中において、ボイド150が一の起点から成長すると仮定したときの、所定温度でSIV保証時間topenに広がるボイド150の成長領域の想定値xopenを算出するステップと、想定値xopenと第一の配線112とビア124との接触領域のサイズとを比較することにより、ビア124の形状因子を規定するステップと、を含む。接触領域のサイズは、d+2h(dはビア124の直径、hはビア124が第一の配線112内に埋め込まれる深さ)とすることができる。

(もっと読む)

微細加工処理剤、及びそれを用いた微細加工処理方法

【課題】 タングステン膜及びシリコン酸化膜の積層膜に対して、エッチレートを制御して微細加工処理をすることが可能な微細加工処理剤、及びそれを用いた微細加工処理方法を提供する。

【解決手段】 本発明の微細加工処理剤は、フッ化水素及び硝酸を含み、基板上に積層されたタングステン膜及びシリコン酸化膜を微細加工する微細加工処理剤であって、前記タングステン膜に対する25℃でのエッチレートが0.5〜5000nm/分の範囲内であり、且つ、前記シリコン酸化膜に対する25℃でのエッチレートが、前記タングステン膜に対する25℃でのエッチレートの0.5〜2倍の範囲内であることを特徴とする。

(もっと読む)

アルミノシリケート前駆体から形成された低いkの誘電体の層

アルミノシリケート前駆体で、高い機械的な強度の、低いkの、層間の誘電体の材料を、アルミニウムがその材料のケイ素の基材の中へ手軽に組み込まれるように、形成するための方法、及び、そのように形成された一つ又はより多くの高い強度、低いkの層間の誘電体の層を含む集積回路デバイス。

(もっと読む)

(もっと読む)

半導体装置の製造方法及び製造装置

表面に絶縁領域と金属領域とが露出した基板の該表面を、有機系洗浄液を用いて洗浄する。洗浄された基板の表面に紫外線を照射する。これにより、基板表面に残留物が残ることを抑制することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】金属薄膜抵抗体を含む集積回路を備えた半導体装置において、レーザ照射による金属薄膜抵抗体の周辺領域へのダメージを低減する。

【解決手段】半導体基板1上に形成された下層側絶縁膜5と、下層側絶縁膜5上に形成された金属配線パターン11と、下層側絶縁膜5上及び金属配線パターン11上に形成された、少なくとも最上層にリン又はリン及びボロンが導入されたシリコン酸化膜15bをもつ下地絶縁膜15と、金属配線パターン11上の下地絶縁膜15に形成された接続孔17を備え、金属薄膜抵抗体21は下地絶縁膜15上から接続孔17内にわたって形成されて接続孔17内で金属配線パターン11と電気的に接続されている。

(もっと読む)

下にあるバリア層への多孔性低誘電率膜の接着を促進する手法

下にあるバリア層に対する多孔性低誘電率膜の接着は、その上にある多孔性低誘電率膜より炭素含量が低く、シリコン酸化物が豊富な中間層を形成することにより向上する。この接着層は、多数の手法のうち一つを単独で又は組み合わせて利用して形成されてもよい。一つのアプローチでは、接着層は、低誘電率材料の堆積直前にO2/CO2/などの濃酸化ガスを導入してSi前駆体を酸化することにより形成することができる。別のアプローチでは、α−テルピネン、シメン及びその他の酸素非含有有機物などの熱的に不安定な化学物質が、低誘電率膜の堆積前に除去される。また別のアプローチでは、ハードウェア又はシリコン非含有成分を導入する方式などの処理パラメータが変更されて、低誘電率膜の堆積の前に酸化物界面の形成を可能とすることもできる。さらに別のアプローチでは、吸収量、エネルギー又は熱アニール処理の使用などの電子ビーム処理のパラメータが制御され、バリアと低誘電率膜との間の界面で炭素種を除去することもできる。さらなるアプローチでは、低誘電率堆積の前に前処理プラズマが導入されバリア界面の加熱を増進することにより、低誘電率堆積ガスが導入され、低誘電率膜が堆積される時、薄い酸化物界面を形成することもできる。 (もっと読む)

アモルファス炭素膜のCVD堆積用の液体前駆体

アモルファス炭素材料を堆積するための方法が提供される。一態様では、本発明は、処理チャンバに基板を位置決めするステップと、該処理チャンバに処理ガスを導入するステップであって、該処理ガスがキャリアガス、水素および1つ以上の前駆体化合物を含むステップと、二重周波数RF源から電力を印加することによって該処理ガスのプラズマを生成するステップと、該基板上にアモルファス炭素層を堆積するステップとを含む基板処理方法を提供する。 (もっと読む)

プラズマ処理システムにおける選択性の制御方法

プラズマ処理システムにおける、半導体基板上の所定の層を介して機能をエッチングするための方法。本方法は、上記プラズマ処理システムのプラズマ処理室に基板を置くことを含む。また本方法は、上記プラズマ処理室内へエッチャント混合気を流し込むことも含み、上記エッチャント混合気は所定の層をエッチングするように構成されている。本方法はさらに、エッチャント・ソース・ガスからのプラズマを打撃することを含む。さらに本方法は、上記基板にバイアスRF信号を印加しながら、上記機能を少なくとも部分的に所定の層を介してエッチングすることを含む。上記バイアスRF信号は約27MHz乃至約75MHzの範囲のバイアスRF周波数と、バイアスRF電力成分とを有し、上記バイアスRF電力成分は、エッチ機能を、基板の第2の層への、予め決められた選択性しきい値より高いエッチング選択性でエッチングさせるように構成され、または上記機能を、バイアスRF周波数における予め決められたエッチ速度パラメータ及びエッチ・プロファイル・パラメータに従ってエッチングさせるように構成される。  (もっと読む)

(もっと読む)

121 - 140 / 141

[ Back to top ]