Fターム[5F033RR12]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 不純物を含むもの (1,419)

Fターム[5F033RR12]の下位に属するFターム

Fターム[5F033RR12]に分類される特許

101 - 120 / 141

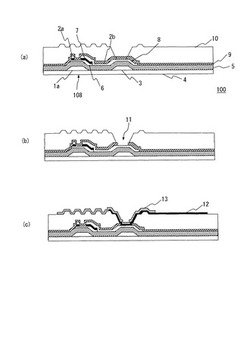

表示装置の製造方法

【課題】表示品質の優れた表示装置を生産性よく製造することができる表示装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る表示装置の製造方法は、TFT108を備える基板100を有する表示装置に関する方法である。まず、TFT108を備える基板100上にスルーホール11を有する平坦化膜10を成膜する。次に、スルーホール11を介してTFT108のドレイン部と接続され、画素電極の少なくとも一部となる透明導電膜12を成膜する。そして、透明導電膜12を成膜後、TFT108を備える基板100に対してプラズマによる第1の表面処理を行う。さらに、プラズマによる第1の表面処理後、反射膜13を成膜する。

(もっと読む)

アンテナ装置

【課題】本発明は、従来の電子機器において機器内の各回路ブロック間の高速で大量のデータ転送を無線化する際に課題となる種々の問題点、特にアンテナの実装の課題を解決し、従来のデータ伝送方式の欠点や制約を除去し低コストで信頼性の高い電子装置および無線通信端末を実現することを目的とする。

【解決手段】基板内のエリア毎に導電率の選択が可能な集積回路基板と、該集積回路基板上に導電層によって形成された導体素子とによって構成され、前記集積回路基板内で前記導体素子の直下および近傍は前記集積回路基板の他の部分よりも低導電率となるように構成する。

(もっと読む)

貴金属ライナとこれに隣接する誘電材料間の付着性を向上させた相互接続構造およびその製造方法(金属/誘電体界面のための付着性向上)

【課題】 貴金属ライナとこれに隣接する誘電材料との間の付着性を向上させた相互接続構造を提供する。

【解決手段】 化学的にエッチングした誘電材料と貴金属ライナとの間の付着性を向上させた相互接続構造およびこれを製造する方法を提供する。本発明によれば、化学的にエッチングした誘電材料に処理ステップを行って、処理した表面が疎水性になるように誘電材料の化学的性質を変更する。処理ステップは、貴金属ライナの堆積前に実行して、化学的にエッチングした誘電材料と貴金属ライナとの間の付着性を向上させるのに役立てる。

(もっと読む)

半導体装置、電子部品、回路基板及び電子機器

【課題】本発明の目的は、パッケージサイズがチップサイズに近く、応力吸収層とは別に、熱ストレスを効果的に吸収することができる半導体装置及びその製造方法、回路基板並びに電子機器を提供することにある。

【解決手段】パッケージサイズがチップサイズに近く、応力吸収層とは別に、熱ストレスを効果的に吸収することができる半導体装置である。半導体装置150は、電極158を有する半導体チップと、半導体チップの上に設けられる応力緩和層としての樹脂層152と、電極158から樹脂層152の上にかけて形成される配線154と、樹脂層152の上方で配線154に形成されるハンダボール157と、を有し、樹脂層152は表面に窪み部152aを有するように形成され、配線154は窪み部152aの上を通って形成される。

(もっと読む)

固体及び気体誘電体の組み合わせによって離間された相互接続した導電性配線及びビアを含む多層相互接続構造を形成する方法、及び、空隙を含む複数レベルの相互接続構造(空隙を含む多層相互接続構造及びその製造方法)

【課題】本発明は、空隙を含む複数レベルの相互接続構造及びその製造方法を提供する。

【解決手段】空隙を含む複数レベルの相互接続構造は、散在したライン・レベル及びビア・レベルの集合を含み、ビア・レベルは、1つ以上の誘電体層に埋め込まれた導電性ビアを含み、ビア・レベルの誘電体層は、隣接レベルのライン機構の上下に位置する固体であり、ライン機構の間でミシン目が入れられている。ライン・レベルは導電性ラインと、空隙を含む誘電体とを含む。導電性接点を含み、有孔誘電体層内に充填することによって形成された固体誘電性ブリッジ層は、散在したライン及びビア・レベルの集合上に配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】アスペクト比が大きな配線層を有する半導体装置であって、半導体装置製造プロセスのスループットを低下させることなく、ボイドを介した導電性プラグ間の短絡を抑制可能な半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板11上で相互に並行して延在する2つの配線141,142と、2つの配線141,142を覆って堆積された層間絶縁膜と、2つの配線141,142の間で層間絶縁膜を貫通して形成された2つのコンタクトプラグ191,192とを備える。2つのコンタクトプラグ191,192の間で、2つの配線141,142の相互に対向する側面は、2つの配線141,142を含む面内方向に凹凸形状を有する。

(もっと読む)

低Kデュアルダマシン集積回路の形成に用いることのできる有機BARCエッチングプロセス

ある実施形態によれば、プラズマリアクタにおいて、有機平坦化層をマスキングするハードマスクを覆うフォトレジストマスク構造を含むレジスト構造の有機平坦化層にトレンチをエッチングする方法が提供される。これには、プラズマリアクタに、N2、H2及びO2を含むエッチャントガス化学物質を導入する工程と、マスクした有機平坦化層を、エッチャントガス化学物質から形成されたプラズマを用いて、エッチングする工程とが含まれる。これには、1回のエッチング工程で、平坦化層を通してエッチングしてトレンチを形成する工程が含まれる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 多層配線の層間絶縁層の膜剥れや、クラックを防止する。

【解決手段】 半導体装置の製造方法は、銅配線を覆うシリコンカーバイド層を有する下地構造を準備する工程と、前記下地構造のシリコンカーバイド層表面を、O2より分子量が大きく、酸素を含む弱酸化性ガスのプラズマで親水化処理する工程と、親水化処理したシリコンカーバイド層表面上に、酸化シリコンより比誘電率の小さい低誘電率絶縁層を形成する工程と、を含む。

(もっと読む)

プラズマ処理方法

【課題】 マスクを除去する時にエッチングによる副生成物に起因するフッ素の反応活性種の生成を防止して下地膜の膜厚を均一に保ちながらマスクを除去して、その後の下地膜のオーバーエッチングの時間を少なくして配線層の減少を抑制することができるプラズマ処理方法を提供する。

【解決手段】 本発明のプラズマ処理方法は、処理容器11内に導入したフッ素を含むガスをプラズマ化し、ウエハ中のシリコン含有膜33を、この膜33上にあるマスク34のパターンを介して途中までエッチングする工程と、エッチングにより生成して処理容器1内の部品に付着したフッ素を含有する副生成物を除去する工程と、副生成物を除去した後、処理容器11内でマスク34を除去する工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置に記憶された情報のセキュリティ性を向上させる技術を提供する。

【解決手段】半導体基板20上に多層配線層を形成する。そして、多層配線層のうち最上層配線層に配線42を形成する。配線42上に酸化シリコン膜43、有色薄膜44および酸化シリコン膜45を順次形成し、酸化シリコン膜45上に表面保護膜となる窒化シリコン膜46を形成する。すなわち、本発明の特徴は、最上層配線層を構成する配線42と表面保護膜となる窒化シリコン膜46の間に有色薄膜44を形成する。この有色薄膜44は、可視光および特定波長域のレーザ光を減衰させる機能を有し、例えば、酸化コバルトを含有する酸化シリコン膜より形成する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】導電性が良好でありながらも銅の拡散を十分に防止することが可能な銅配線の埋め込み構造を備えた半導体装置およびその製造方法を提供する。

【解決手段】第1絶縁膜13に形成された配線溝13a内、第2絶縁膜22および第3絶縁膜に形成された配線溝24aと接続孔22a内に、拡散防止層15,25を介して銅配線17a,26aが埋め込まれた半導体装置27において、拡散防止層15,25は、ルテニウムカーバイト(RuCx)、ルテニウムシリサイド(RuSix)、またはルテニウム合金(RuTa)を用いて構成されたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】配線のマイグレーション耐性を向上させるとともに、シリコンの配線内部への拡散を抑制する。

【解決手段】半導体装置100は、シリコン基板101、シリコン基板101上に設けられ、SiCN膜103、SiOC膜105およびSiO2膜107からなる第一絶縁膜、当該第一絶縁膜中に設けられ、主として銅含有金属からなる第一銅配線111、を含む。第一銅配線111の内部の表面近傍に、シリコンが導入されたSi−O偏在層115を有し、導入されたシリコンの少なくとも一部が、Si−O結合を形成している。

(もっと読む)

無電解堆積の触媒作用にイオン注入表面改質を用いる金属膜堆積技術

無電解堆積の触媒作用にイオン注入による表面改質を用いて金属膜を堆積する技術を開示する。1つの特定の例示的な実施形態では、この技術は、金属膜を堆積する方法として実現されうる。当該方法は、基板と、基板上の誘電体層と、誘電体層上のレジスト層とを含み、誘電体層及びレジスト層は1以上の開口を有する構造上に、触媒材料を堆積することを含みうる。当該方法は更に、レジスト層を剥離することを含む。当該方法は更に、1以上の開口を充填すべく構造の1以上の開口内の触媒材料上に金属膜を堆積することを含む。 (もっと読む)

界面キャップ構造体を用いて最終レベル銅・C4間接続部を形成する方法

【課題】 ICチップの最終レベル銅相互接続部と制御崩壊チップ接続部(controlled-collapse chip connection、C4)との間に界面キャップ構造体を製造する方法を提供すること。

【解決手段】 本発明は、実質的にアルミニウムを含まない最終レベル銅・C4間接続部を含む半導体デバイスの製造方法に関する。具体的には、最終レベル銅・C4間接続部は、CoWP、NiMoP、NiMoB、NiReP、NiWP及びこれらの組み合わせを含む界面キャップ構造体(30)を含む。界面キャップ構造体は、少なくとも1つのCoWP層を含むことが好ましい。こうしたCoWP層は、選択的な無電解めっきプロセスによって、最終レベル銅相互接続部(22)の上に、容易に形成することができる。

(もっと読む)

CMOS対応の浅いトレンチのeフューズ構造体及びその製造方法

【課題】 少なくとも1つのeヒューズを含む半導体構造体と標準的な半導体技術との統合が容易であり、よって実施コストが最小になる製造方法を提供する。

【解決手段】 半導体基板(バルク又は半導体オン・インシュレータ)内に配置されたトレンチ内に埋め込まれた少なくとも1つのeヒューズを含む半導体構造体が提供される。本発明によると、eヒューズは、半導体基板内に配置されたドーパント領域と電気接触した状態にある。本発明はまた、埋め込まれたeヒューズが、トレンチ分離領域とほぼ同時に形成される半導体構造体を製造する方法も提供する。

(もっと読む)

導体−誘電体構造およびこれを作成するための方法

【課題】導体−誘電体構造およびこれを作成するための方法を提供すること。

【解決手段】導体−誘電体相互接続構造は、パターン形成されたフィーチャをその内部に有する誘電体層を含む構造を用意し、パターン形成されたフィーチャ内の誘電体層の表面にめっきシード層を付着させ、パターン形成されたフィーチャ内のめっきシード層の表面に犠牲シード層を付着させ、犠牲シード層の厚さを逆めっきによって低減させ、パターン形成されたフィーチャ内の犠牲シード層の表面に導電性金属をめっきすることによって作成される。さらに、パターン形成されたフィーチャをその内部に有する誘電体層と、パターン形成されたフィーチャ内の誘電体層の表面のめっきシード層と、パターン形成されたフィーチャ内に位置する不連続な犠牲シード層とを含む構造も提供される。

(もっと読む)

半導体装置の製造方法

【課題】水分および有機物の吸着量の少ないTEOS膜を形成する。

【解決手段】TEOSおよび酸素(O2)を含む混合ガスを反応室51に供給する工程を有するプラズマCVD法によって、ステージ53上に配置された半導体ウエハ1Wの主面上にTEOS膜を成膜する。反応室51内に配置されたシャワーヘッド52の電極には、13.56MHzの高周波電力および350kHzの高周波電力を供給し、酸素とTEOSとの流量比を、3以上、10未満とする。このTEOS膜の成膜速度が50nm/min以上、150nm/min以下となるように調整する。

(もっと読む)

半導体装置およびその製造方法

【課題】シールリングの構造を最適化して、ダイシング部の切断面からの水分の侵入やクラックの伸展に対する障壁としての機能を確保したシールリングを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上の回路形成領域とダイシング領域との間にシールリング100が配設されている。シールリング100は、断面形状がT字型をなすシール層が積層された部分と、断面形状が矩形をなすシール層が積層された部分とを有している。

(もっと読む)

金属配線構造の形成方法

【課題】平坦かつ薄いバリア膜またはRu膜をダマシン構造で形成する。

【解決手段】金属配線構造を形成する方法は、(i)露出した配線層及び露出した絶縁層を含む多層構造を反応空間内に与える工程と、(ii)還元雰囲気中で、絶縁層の少なくとも露出面上に-NH2または>NHターミナルを導入する工程と、(iii)反応空間へ還元剤を導入し、その後反応空間をパージする工程と、(iv)反応空間へハロゲン化金属化合物を導入し、その後反応空間をパージする工程と、(v) N及びHを含むガスを導入し、その後反応空間をパージする工程と、(vi)金属含有バリア層を製造するべく工程(iii)から(v)を連続して繰り返す工程と、(vii)金属含有バリア層上に金属膜を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルがない場合であっても、配線の平坦性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本実施例の半導体装置の製造方法は、半導体基板1上に層間絶縁膜2を形成し、層間絶縁膜2上に金属を含むメタルマスク3を形成し、メタルマスク3および層間絶縁膜2の一部をエッチングして、メタルマスク3および層間絶縁膜2にパターン溝2aを形成し、パターン溝2a内を埋め込むように、層間絶縁膜2上に導電層5を形成し、パターン溝2a内に導電層5を残すように、層間絶縁膜2上の余剰の導電層5を研磨する。

(もっと読む)

101 - 120 / 141

[ Back to top ]