Fターム[5F033RR12]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 不純物を含むもの (1,419)

Fターム[5F033RR12]の下位に属するFターム

Fターム[5F033RR12]に分類される特許

81 - 100 / 141

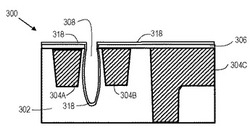

半導体装置及び半導体装置内に空洞を形成する方法(核化防止層を使用する選択的なピンチ・オフを有する空隙)

【課題】配線用の導電体相互間のクロストークを減少した半導体装置を提供する。

【解決手段】半導体装置内に空洞を形成する方法が開示される。本発明の方法は、半導体装置のILD層内の空洞の内面上に核化防止層を付着することを含む。この核化防止層は、後に付着される誘電体層が空洞内に付着することを防止する。誘電体層が空洞内に付着することを防止することにより、キャパシタンスが減少され、これにより、改善された半導体動作特性を実現する。

(もっと読む)

配線、電子装置及び電子装置の製造方法

【課題】性能劣化を抑制することが可能な高信頼性の配線を提供する。

【解決手段】第1導電膜に一端を接続し、第1導電膜と離間した第2導電膜に他端を接続する束状のカーボンナノチューブからなる複数の導電部材20と、導電部材20の間に分散されたダイヤモンド結晶構造を有する炭素粒子22とを備える。

(もっと読む)

配線、電子装置及び電子装置の製造方法

【課題】抵抗を低減することが可能な配線を提供する。

【解決手段】第1導電膜12と第1導電膜12の上層の第2導電膜26とを電気的に接続する配線24であって、第1導電膜12の上の複数の第1金属粒子16と、複数の第1金属粒子16のそれぞれを介して第1導電膜12の表面に一端を接続する複数の導電部材18と、複数の導電部材18のそれぞれの他端側の側面上の複数の第2金属粒子20と、複数の第2金属粒子20のそれぞれを介して複数の導電部材18のそれぞれの表面に一端を接続し、第2導電膜26にそれぞれ接続する複数の導電部材22とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】セルコンタクトのアクティブ領域に対する位置合わせにずれが生じた場合でも、コンタクト抵抗を増大させない半導体装置及びその製造方法を提供する。

【解決手段】半導体基板20、半導体基板に設けられた素子分離膜21、層間絶縁膜60及び導電プラグ62を備えて構成される。半導体基板は、一方の主表面20a側に、第1の方向及び第2の方向に行列配列されたメモリセルを有している。導電プラグは、層間絶縁膜内に形成されていて、メモリセルと層間絶縁膜上に形成される配線74とを電気的に接続する。各メモリセルは、ゲート電極34と、一対の不純物拡散領域40を備えている。不純物拡散領域は、主表面側に金属シリサイド膜46を有している。導電プラグは、素子分離膜上と金属シリサイド膜上とに形成されている。金属シリサイド膜は、第1部分47と、第2部分48を備えていて、第1部分の厚みが第2部分の厚みよりも大きい。

(もっと読む)

半導体素子の製造方法

【課題】絶縁膜の比誘電率が小さくて高速応答性に優れ、かつ、絶縁膜の機械的強度にも優れ、更には配線の信頼性が高い半導体素子を提供することである

【解決手段】膜2に凹部3を形成する工程を有する半導体素子の製造方法において、前記凹部3を形成した後、該凹部が形成された膜2に電磁エネルギを照射する照射工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】被覆率としては従来と変わることなく、かつシリコン酸化膜との間で選択比の取れるシリコン窒化膜を有する半導体装置の製造方法を提供することにある。

【解決手段】半導体基板の主表面上に層間絶縁膜を形成する工程と、前記層間絶縁膜に前記半導体基板の主表面に達するコンタクトホールを形成する工程と、前記側壁にシリコン窒化膜が形成されたコンタクトホール内にTi層およびTiN層を有するバリアメタル層を形成する工程と、前記バリアメタル層が形成されたコンタクトホール内に導電層を形成する工程と、SinCl2n+2とNH3との混合ガス、またはSinCl2n−2−xとNH3との混合ガスを用い(nは2以上の自然数、xは2n+2以下の自然数)、700℃以下の成膜温度で、前記コンタクトホール内の導電層上に塩素を含有するシリコン窒化膜を形成する工程とを備えたことを特徴とする。

(もっと読む)

ダメージの入った多孔性誘電体の処理方法

【課題】処理工程で変化した多孔質誘電体層の初期特性を回復させ保持する方法を提供する。

【解決手段】処理された多孔質誘電層であって少なくとも部分的に露出した多孔質誘電層10を上部に有する基板を提供する工程と、処理された多孔質誘電層10の少なくとも露出した部分に薄い水性膜を形成する工程と、表面に水性膜を有する露出した多孔質誘電体膜10を、少なくとも1のシリル化剤と濃縮CO2を含む混合物を含む雰囲気に接触させる工程とを含み、これにより多孔質誘電体10の初期特性を回復させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ダマシン法で多層配線構造を形成する際に、EM耐性およびSM耐性を高めつつ、接続不良を防いで配線の歩留まりを向上させる。

【解決手段】半導体装置は、半導体基板上に形成され、銅を主成分とする材料により構成された銅配線上にシリコン含有ガスを照射して、銅配線の表面にシリコン含有層を形成する工程(S102)と、銅配線上に、拡散防止膜を形成する工程(S104)と、拡散防止膜上に、Si、O、およびCを含む層間絶縁膜を形成する工程(S106)と、層間絶縁膜に、拡散防止膜に達する凹部を形成する工程(S108)と、凹部側壁に露出した層間絶縁膜表面に他の領域よりも酸素濃度が高い改質層を形成する工程(S110)と、拡散防止膜を除去して銅配線表面を露出させる工程(S112)と、凹部内に導電材料を埋め込み配線を形成する工程(S114)とにより形成される。

(もっと読む)

半導体装置の平坦化方法および半導体装置の平坦化システム

【課題】ダミーパターンの一部を削除することにより、ダミーパターン挿入量を最小化しつつ、かつチップ内の凹凸を抑制することができる半導体装置の平坦化方法および半導体装置の平坦化システムを提供する。

【解決手段】半導体装置の製造において、シミュレーションサーバを用いて、配線として形成される溝以外に電気的に機能しないダミーパターンを導入する半導体装置の平坦化方法であって、ダミーパターンを設計データ上にて、配線またはその他の電気的に機能するパターンが存在する場所以外の全ての領域に規定の間隔で導入した後、CMPプロセス後の膜厚が厚くなると予測される場所から設計データ上のダミーパターンを削除し、ダミーパターンが削除された後の設計データを用いてシャドウマスクを製造する。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール底部における銅配線の電気伝導度低下に起因するEM耐性の劣化を防止し、高信頼性を確保できる配線を備えた半導体装置の製造方法を提供する。

【解決手段】下層配線11上に形成された層間絶縁膜13に、コンタクトホール20が形成される。コンタクトホールが形成されると、コンタクトホール底部に露出した下層配線の酸化層25を除去する洗浄が行われる。洗浄完了後、所定時間内に、導電性バリア膜14が形成される。導電性バリア膜上には、コンタクトホールを充填するシード膜15及び銅めっき膜17が形成される。上記所定時間は、例えば、洗浄完了から導電性バリア膜形成開始までの時間と、コンタクトホールに充填された導電膜を含む配線のEM耐性との関係に基づいて設定する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】浅いソース、ドレイン接合位置を保ちつつ、ソース、ドレインがシリサイド化され、かつ、接合リークが低く抑えられた半導体装置の製造方法および半導体装置を提供する。

【解決手段】MISFET(金属絶縁物半導体電界効果トランジスタ)を有する半導体装置の製造方法であって、シリコン基板1100の表面に、このMISFETのゲート絶縁膜を形成し、このゲート絶縁膜上にゲート電極を形成し、このゲート電極の両側に、{110}面方位を有するシリコン面上に設けられ、このシリコン面上の<100>方向に垂直な長辺と、この<100>方向に平行で幅が0.5μm以下の短辺からなる矩形状を呈し、MISFETのソース、ドレイン領域の一部を構成する複数のニッケルシリサイド(NiSi)領域501a、502aを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁層への吸湿や絶縁層を通過する水分の配線層やビアへの悪影響を抑制でき、その結果、誘電率の上昇、配線金属の腐食、配線金属の絶縁膜中への滲みだし、リーク電流の増大等の問題のいずれかまたは全てを抑制できる半導体装置を提供する。

【解決手段】本半導体装置は、絶縁性組成物上の溝、穴または溝と穴の両方に、当該絶縁性組成物を窒化してなる窒素含有組成物とフッ素含有組成物と導体とがこの順に積層されてなる構造体を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Cu配線10を、その中央部のCu粒子10aが比較的大きく、その上部や下部のCu粒子10aが比較的小さくなるような構造にする。このような構造は、Cu配線10をダマシン法により形成する際の電解めっき時の電流密度を制御することによって形成することができる。このような構造にしたCu配線10では、その上部よりも中央部に比較的電流が流れやすくなり、その上部のCu原子の拡散が抑えられるようになり、また、それにより、キャップ膜14界面からのCu原子の拡散が抑えられるようになる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のインライン欠陥検査工程において、物理解析時に短時間で故障箇所の位置を確認することのできる技術を提供する。

【解決手段】テストパターンの基幹配線部、配線中央部および配線端部にそれぞれ基幹配線部セパレータ1、配線中央部セパレータ2および配線端部セパレータ3を配置し、テストパターンに搭載したこれら各種セパレータ1,2および3を、欠陥観察の際に欠陥の座標位置を確認する指標とする。例えば配線中央部セパレータ2は、セパレータ長Lの長さ分だけ第2配線層4を表面に露出させて、配線パターンとして観察される構造とし、その他の配線中央部は第1配線層5を経由して基幹配線部から配線端部へと電気的に接続することにより、配線パターンとして観察されない構造とする。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】水分の浸透を防止するシリコン窒化膜を寄生容量が増大しないように設ける不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】シリコン基板1に、ゲート絶縁膜6、浮遊ゲート電極膜7、ONO膜やNONON膜などの電極間絶縁膜8、制御ゲート電極膜9および加工用ハードマスク材10を積層してエッチング加工することによりゲート電極MGを形成する。浮遊ゲート電極膜7の上面位置までシリコン酸化膜11を埋め込み、その上にホウ素を含有した比誘電率が小さいシリコン窒化膜(SiBN)12を成膜する。この上にシリコン酸化膜13を成膜する。この構成で、シリコン窒化膜12は、水分の浸透を防止し、しかも、浮遊ゲート電極膜7や制御ゲート電極膜9の間に位置せずしかも比誘電率が小さいので寄生容量の増大を抑制できる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】多層配線の容量低減を図る半導体装置の製造方法或いは半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に犠牲膜を形成する犠牲膜形成工程(S104)と、犠牲膜上に絶縁膜を形成する絶縁膜形成工程(S106)と、犠牲膜と絶縁膜とに複数の第1の開口部を形成する第1の開口部形成工程(S108)と、複数の第1の開口部に導電性材料を堆積させる導電性材料堆積工程(S114)と、複数の第1の開口部に堆積した各導電性材料間の領域のうち、導電性材料のピッチが最小となる最小寸法領域とは異なる絶縁膜の所定の領域に第2の開口部を形成する第2の開口部形成工程(S116)と、第2の開口部を介して最小寸法領域に位置する犠牲膜を含む犠牲膜を除去する犠牲膜除去工程(S118)と、を備えたことを特徴とする。

(もっと読む)

アモルファスカーボン膜、半導体装置、成膜方法、成膜装置及び記憶媒体

【課題】比誘電率を低く抑えながら、弾性率が高く、また熱収縮率が小さいアモルファスカーボン膜及びその膜を備えた半導体装置、並びにアモルファスカーボン膜を成膜する技術を提供する。

【解決手段】成膜時にSi(シリコン)の添加量を制御しながらアモルファスカーボン膜を成膜しているので、比誘電率を3.3以下の低い値に抑えながら、弾性率が高く、また熱収縮率の小さいアモルファスカーボン膜を得ることができる。従ってこのアモルファスカーボン膜を、半導体装置を構成する膜として用いた場合に膜剥がれなどの不具合が抑えられ、その結果、低誘電率であり、かつCuなどの金属に対するバリア性を有するといった利点を生かすことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】1の層間絶縁膜について、配線の配置密度が異なる場所に同じ絶縁材料を使用し、且つ、配線の配置密度に対応した寄生容量を有する半導体装置或いは半導体装置の製造方法を提供する。

【解決手段】配線の配置密度が異なる第1のエリア及び第2のエリアを有する半導体装置の製造方法であって、前記配線間を絶縁する多孔質の絶縁膜を形成する工程と、前記絶縁膜の表出する面のうち、前記第1のエリアよりも前記配置密度が小さい前記第2のエリアにエネルギー線を照射し、前記絶縁膜のヤング率が前記第1のエリアに比べて大きな値になるように、前記絶縁膜の構造を変える工程とを有する。

(もっと読む)

Ru膜および金属配線構造の形成方法

【課題】高速論理回路素子に利用される配線構造において、連続したルテニウム(Ru)薄膜を容易に形成する方法を提供する。

【解決手段】 ルテニウム(Ru)薄膜を基板上に堆積する方法は、(i)基板表面を有機金属前駆体で処理する工程と、(ii)処理した基板表面にルテニウム前駆体を吸着させる工程と、(iii)吸着させたルテニウム前駆体を励起させた還元性ガスで処理する工程と、そして(iv)工程(ii)および(iii)を繰り返すことにより、ルテニウム薄膜を基板上に形成する工程とを含む。

(もっと読む)

低抵抗コンタクト構造体及びその製造方法

【課題】 半導体デバイスと後工程の相互接続体との間の誘電体材料層内にコンタクト構造体を製造する方法を提供すること。

【解決手段】 本発明の実施形態は、半導体デバイスと後工程の相互接続体との間の誘電体材料層内にコンタクト構造体を製造する方法を提供する。この方法は、誘電体材料層内に少なくとも1つのコンタクト開口部を作成するステップと、化学気相堆積プロセスによって第1のTiN膜を形成するステップであって、第1のTiN膜はコンタクト開口部をライニングする(内側を覆う)ステップと、物理的気相堆積プロセスによって第2のTiN膜を形成するステップであって、第2のTiN膜は第1のTiN膜をライニングするステップとを含む。本発明の実施形態によって製造されるコンタクト構造体も提供される。

(もっと読む)

81 - 100 / 141

[ Back to top ]