Fターム[5F033SS01]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 原料ガス (1,958)

Fターム[5F033SS01]の下位に属するFターム

Fターム[5F033SS01]に分類される特許

201 - 220 / 260

半導体装置の製造方法

【課題】デバイス特性の向上を図るとともにさらなる微細化に対応可能な半導体装置の製造方法を得ること。

【解決手段】半導体基板11上にゲート絶縁膜16を形成する工程と、前記ゲート絶縁膜16上にゲート電極17を形成する工程と、前記半導体基板11の表層の前記ゲート絶縁膜16およびゲート電極17の周辺領域に、チャネル領域を規定するように所定の間隔を隔てて一対のソース・ドレイン拡散層14を形成する工程と、前記ゲート電極17の表層および前記一対のソース・ドレイン拡散層14の表層にシリサイド層15、18を形成する工程と、前記シリサイド層15、18の形成後に、前記半導体基板11を減圧下において450℃以下の温度範囲で窒素含有ガス雰囲気中およびシリコン含有ガス雰囲気中に個別に暴露して半導体基板11上にライナー膜22を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 銅イオンの拡散防止機能を持つ低誘電率の層間絶縁膜の成膜初期における銅配線からの銅イオンの拡散を防止する。

【解決手段】 半導体装置の製造方法は、基板上の絶縁膜(1)に形成された銅配線(3b)における露出部位に、窒素を含む層(4a)を形成する。その後、シロキサン(Si−O−Si)結合を有する有機シリコン化合物を原料として用いて、プラズマCVD法により、窒素を含む層(4a)の上に層間絶縁膜(5)を形成する。

(もっと読む)

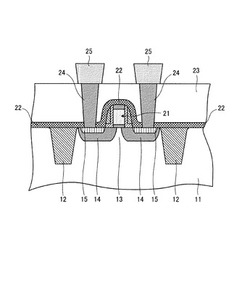

半導体装置

【課題】 絶縁ゲート型トランジスタを有する半導体素子を備えた半導体装置の信頼性を向上させることのできる技術を提供する。

【解決手段】 半導体基板1と、半導体基板1の主面に形成され、絶縁ゲート型トランジスタを有するメモリセルMCと、メモリセルMC上に形成された絶縁膜14と、メモリセルMCと電気的に接続され、絶縁膜14上に形成された金属配線21と、絶縁膜14および金属配線21を覆うように形成された絶縁膜22とを有する。絶縁膜14は、窒素の含有量が1atom%乃至15atom%の範囲内の酸窒化シリコン膜である。

(もっと読む)

層間絶縁膜の形成方法及び層間絶縁膜の膜構造

【課題】 銅イオンの拡散防止機能、熱安定性、及び機械的強度に優れた層間絶縁膜の形成方法を提供する。

【解決手段】 層間絶縁膜の形成方法は、酸素原子を含有しない有機シリコン化合物、及び酸素原子を含有する有機シリコン化合物を原料として用いて、プラズマCVD法により、基板上に層間絶縁膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ボラジン系化合物の絶縁膜を用いて、絶縁材料と配線材料との間の密着性や、機械強度等の特性が向上された半導体装置およびその製造方法を提供すること

【解決手段】 凹部に第1の導体層が埋め込まれた第1の絶縁層と、第1の絶縁層上に形成されたエッチングストッパー層と、エッチングストッパー層上に形成された第2の絶縁層と、第2の絶縁層上に形成された第3の絶縁層と、第2の絶縁層と第3の絶縁層との凹部に埋め込まれた第2の導体層と、を含む半導体装置であって、第2の絶縁層および第3の絶縁層は、炭素含有ボラジン化合物を原料として化学的気相反応成長法によって形成され、第3の絶縁層の炭素含有率が、第2の絶縁層の炭素含有率よりも小さいことを特徴とする半導体装置。

(もっと読む)

半導体集積回路装置の製造方法

【課題】層間絶縁膜をドライエッチングして下層のCu配線の上部に配線溝を形成する際、配線溝の底部に露出した下層のCu配線の表面に絶縁性の反応物が付着したり、配線溝の側壁に露出した炭化シリコン膜や有機絶縁膜がサイドエッチングされるという不具合を抑制する。

【解決手段】炭化窒化シリコン膜を含む積層膜をドライエッチングしてCu配線21の上部に配線溝30を形成する際、CHF3とN2とからなる混合ガスを使用することにより、配線溝30の側壁を垂直に加工すると共に、配線溝30の底部に露出したCu配線21の表面に堆積物や反応物が付着する不具合を抑制する。

(もっと読む)

基板の処理方法,コンピュータ読み取り可能な記録媒体及び基板処理装置

【課題】 より低誘電率で耐熱性のよいアモルファスカーボンの絶縁膜を形成する。

【解決手段】 絶縁膜形成装置32において,処理容器50内のプラズマ生成領域R1には,プラズマ生成用のガスとしてArガスを供給し,基板W側の成膜領域R2には,原料ガスとして多重結合を有するブチンガスを供給する。基板Wにバイアス電圧を印加しない状態で,ラジアルラインスロットアンテナ62から処理容器50内にマイクロ波を供給する。こうすることにより,プラズマ生成領域R1にプラズマが生成され,当該プラズマにより成膜領域R2のブチンガスが活性化されて,基板W上にアモルファスカーボンの絶縁膜が形成される。

(もっと読む)

シリコン酸化膜の形成方法、シリコン酸化膜の形成装置及びプログラム

【課題】 低温下で、ステップカバレッジのよいシリコン酸化膜を形成することができるシリコン酸化膜の形成方法、シリコン酸化膜の形成装置及びプログラムを提供する。

【解決手段】 まず、反応管2内にHCDを供給し、半導体ウエハWにHCDと反応した反応物を形成する。次に、反応管2内に水素ラジカルを供給してこの反応物と反応させ、反応物に含まれる塩素を除去する。続いて、反応管2内に酸素ラジカルを供給する。これにより、酸素ラジカルと反応物とが反応して、半導体ウエハWにシリコン酸化膜が形成される。この処理を複数回繰り返すことにより所望のシリコン酸化膜を形成することができる。

(もっと読む)

成膜方法及び半導体装置の製造方法

【課題】 2.7より低い比誘電率を有する低誘電率絶縁膜及び4より低い比誘電率を有するバリア絶縁膜を化学気相成長法により成膜する方法を提供するものである。

【解決手段】 シリコン原子による5員環以上の環状構造を有し、かつ該シリコン原子によるシロキサン結合を有する第1のシリコン含有有機化合物と、シリコン原子による4員環以下の環状構造又は4以下のシリコン原子の鎖状構造を有し、かつ該シリコン原子によるシロキサン結合を有する第2のシリコン含有有機化合物とを含む成膜ガスのプラズマを生成し、反応させて基板31上に絶縁膜32を形成する。

(もっと読む)

酸化珪素系薄膜の製造方法、酸化珪素系薄膜及び薄膜形成用原料

【課題】 膜質及び生産性において、酸化珪素系薄膜製造に適する薄膜製造プロセスを提供すること。

【解決手段】 トリス(エチルメチルアミノ)シランを含有してなる薄膜形成用原料を気化させて得たトリス(エチルメチルアミノ)シランを含有する蒸気を系内の基体上に導入し、該基体上に珪素含有薄膜層を形成した後、系内のガスを排気してから該系内に酸化性ガスを導入し、該珪素含有薄膜層に該酸化性ガス及び熱を作用させて、先に形成した珪素含有薄膜から酸化珪素系薄膜を製造する薄膜製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜として厚い窒化膜を形成する際、ストレスを抑制するため、窒化膜を2回に分けて成膜し、2回目の成膜は枚葉式プラズマCVD法で行う。しかし枚葉式プラズマCVD法の初期堆積膜はエッチングレートが速いため、層間絶縁膜のエッチング時に初期堆積膜のみエッチングが進行し、開口部側壁に段差が形成されてしまう。その上に段差被覆性の悪い金属層等を被着すると、断線する問題があった。

【解決手段】枚葉式プラズマCVD法による第2窒化膜の形成時に、反応ガスのアンモニアのガス流量を30sccm以下にする。これにより初期堆積膜は硬く薄い膜にすることができる。従って開口部形成時に初期堆積膜でのエッチングの進行を抑制でき、開口部側壁を平坦にすることができる。

(もっと読む)

半導体装置の製造方法

【課題】薄膜化された半導体層を貫通することなく、良好な形状のコンタクトホールを形成することができる半導体装置の製造方法を提供する。

【解決手段】絶縁層8の上に設けられた半導体層10に絶縁ゲート電界効果型トランジスタ20を形成すること、前記絶縁ゲート電界効果型トランジスタ20を覆う層間絶縁層30に、前記絶縁ゲート電界効果型トランジスタ20のソース領域またはドレイン領域となる不純物領域28と接続されるコンタクト層38を形成すること、を含み、前記層間絶縁層30はエッチング速度の異なる積層膜32,34で形成し、所定のパターンのマスク層50を用いて第1エッチングを行い、前記不純物領域28の表面が露出しないような凹部36aを形成した後、該不純物領域28の表面が露出するまで等方性エッチングである第2エッチングを行うことでコンタクトホール36を形成すること、を含む半導体装置の製造方法。

(もっと読む)

高分子材料の蒸着およびその前駆体

置換パラシクロファンは、プロセス中の電子デバイスなどの蒸着用基板に架橋可能なポリマーを形成する前駆体として特に有用である。アルキニルなどの架橋可能な置換基を含むパラシクロファン前駆体のフェニル連鎖を分解し、分解した前駆体に基板を接触させる。その結果、基板上に有機ポリマーが形成される。架橋可能な置換基の熱誘導反応などの反応を介してこのポリマーを架橋することによって、熱的に安定した架橋したポリマーを生成する。このような架橋したポリマーの蒸着は、集積回路の製造におけるダマシン法で用いられる超低k誘電材料の封止に特に有用である。また、このポリマーはウエハとウエハを結合する際の接着剤としても有利である。さらに、このポリマーは電子デバイスのバックエンドオブザライン処理において、窒化シリコンおよび炭化シリコンに代わるハードマスクとしても有用である。 (もっと読む)

半導体装置の製造方法および半導体装置

【課題】 NiSiが用いられたシリサイド上ライナー窒化膜のエッチング特性を改善し、コンタクトホール底での過度のエッチングを防止する。

【解決手段】 半導体基板301の素子活性領域にシリサイド層308を形成する工程と、半導体基板上にライナーになるシリコン窒化膜309を形成する工程と、シリコン窒化膜上に層間絶縁膜を形成する工程と、層間絶縁膜にコンタクトホールを形成する工程とを含み、シリコン窒化膜は、原子層蒸着法によりジクロロシランとアンモニアを用いて曝露するサイクルを繰り返すことにより成膜され、成膜段階におけるアンモニアガスの曝露時間は、表面反応が平衡状態になる緩和時間の2〜10倍である。これにより、窒化膜中の塩素濃度を低減でき、Si−N結合が増やすことができるため、ウェットエッチング耐性を向上できる。

(もっと読む)

低誘電率の隠微結晶層とナノ構造物

本発明は、応用可能な品質の低誘電率(低k)隠微結晶層を最新技術の半導体ウエハー上に生成させるための、そして組織化されたナノ構造物を隠微結晶から生成させるための方法を提供し、これらの物質から得ることができる光学的・電子的なデバイスに関する。本明細書に開示されている結果は、化学気相堆積法(CVP)を使用して単結晶マトリックスの構造と化学組成を改良することで、均一であって且つ半導体ウエハーとの平滑なインターフェースを形成する高品質の隠微結晶層が得られる、ということを示している。この方法を使用すると、誘電性の隠微結晶層を形成するために、1μm/時という高い成長速度を達成することができる。本発明はさらに、隠微結晶を組織化されたシステムに変換することによってマイクロワイヤおよびナノワイヤを製造する方法を提供する。この方法を使用すると、数ナノメートル〜最大で1000ナノメートルの範囲の寸法と、最大で50マイクロメートルの長さを有するナノワイヤを製造することができる。隠微結晶、ナノワイヤ、および組織化された構造物は、次世代のインターコネクションにおけるインターレベル誘電体およびインターメタル誘電体として、超高密度のメモリセルを製造する際において、情報セキュリティにおけるキージェネレータとして、光通信部品を製造する際において、そしてマイクロエレクトロニクスとナノエレクトロニクスの高度な実装とセンサーにおける冷却チャンネルの作製において使用することができる。  (もっと読む)

(もっと読む)

SiC系膜の成膜方法及び半導体装置の製造方法

【課題】配線層の金属の層間絶縁膜中への拡散を防止するバリア膜等として優れた特性を有する低誘電率のSiC膜を成膜することができるSiC系膜の成膜方法、及びその成膜方法により成膜されるSiC膜をバリア膜として用いた半導体装置の製造方法を提供する。

【解決手段】チャンバー内において基板20表面にNH3プラズマを発生させ、基板20に対してNH3プラズマ処理を行う工程と、チャンバー内に残留する窒素を含む反応生成物を除去する工程と、チャンバー内において、基板20上に、PECVD法によりSiC膜34を成膜する工程とを有する。

(もっと読む)

機械的特性を改善するためのその場に埋め込まれたナノ層を有する低k誘電体CVD膜の形成方法(誘電体スタック及び該形成方法、並びに該誘電体スタックを含む相互接続構造体)

【課題】 機械的特性を改善するために内部に埋め込まれたナノ層を有する低k誘電体CVD膜の形成方法を提供すること

【解決手段】 約1×10−10m/秒又はそれ以上の亀裂速度を有する1つ又は複数の膜(14)と、この1つ又は複数の膜(14)内にあるか又はそれに直接接触した少なくとも1つのナノ層(16)を含む材料スタック(12)が提供され、ここで少なくとも1つのナノ層(16)は、材料スタック(12)の亀裂速度を1×10−10m/秒より小さな値に減少させる。1つ又は複数の膜(14)は、低k誘電体に限定されず、金属のような材料を含むことができる。好ましい実施形態においては、約3.0又はそれ以下の有効誘電率kを有する低k誘電体スタック(12)が提供されるが、そのスタック(12)の機械的特性は、少なくとも1つのナノ層(16)を誘電体スタック(12)内に導入することによって改善される。機械的特性の改善は、スタック(12)内の膜の誘電率を著しく増大させることなく、また本発明の誘電体スタック(12)に何らかの後処理ステップを施すことを必要とせずに、達成される。

(もっと読む)

超低k(ULK)SiCOH膜および方法

【課題】 誘電率が2.7以下であり、弾性計数および硬度の改善等、機械的特性を向上させた超低誘電率(k)膜、および、かかる膜の製造方法を提供すること。

【解決手段】 本発明は、弾性係数および硬度が改善した多相超低k膜、ならびにこれを形成するための様々な方法を提供する。多相超低k誘電膜は、Si、C、O、およびHの原子を含み、誘電率が約2.4以下であり、ナノサイズの孔または空隙を有し、弾性係数が約5以上であり、硬度が約0.7以上である。好適な多相超低k誘電膜は、Si、C、O、およびHの原子を含み、誘電率が約2.2以下であり、ナノサイズの孔または空隙を有し、弾性係数が約3以上であり、硬度が約0.3以上である。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【目的】TEOS酸化膜形成後における酸素雰囲気での熱処理による膜質改善効果の及ばない膜厚以上に厚膜や、深いトレンチ構造に酸化膜を埋め込む場合であっても、膜質を改善できる半導体装置の製造方法を提供すること。

【構成】TEOSガスを用いて化学的気相成長法によりTEOS酸化膜を半導体基板上に堆積形成する成膜工程と前記TEOSガスの排気後、酸素ガスを供給して前記TEOS酸化膜上に酸素含有層を積層形成する酸素含有層形成工程との後、前記TEOS酸化膜成膜工程と酸素含有層形成工程とを所要の酸化膜厚さになるまで複数回繰り返す工程と、加熱により前記TEOS酸化膜中に酸素を熱拡散させる工程を備える半導体装置の製造方法とする。

(もっと読む)

有機シリコン系膜の形成方法、及び有機シリコン系膜を有する半導体装置

【課題】 比誘電率が低いと共にリーク電流が少ない有機シリコン系膜を得易い有機シリコン系膜の形成方法を提供する。

【解決手段】 原料ガスとして少なくとも1種の有機シリコン化合物を用いた化学的気相堆積法により有機シリコン系膜を成膜するにあたり、前記有機シリコン化合物として、少なくともケイ素、水素、炭素、及び窒素を構成元素として含有していると共に、ケイ素原子と窒素原子とが互いに結合していない化合物を用いることによって、上記課題を解決した。

(もっと読む)

201 - 220 / 260

[ Back to top ]