Fターム[5F033SS01]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 原料ガス (1,958)

Fターム[5F033SS01]の下位に属するFターム

Fターム[5F033SS01]に分類される特許

141 - 160 / 260

半導体装置及びその製造方法

【課題】 半導体基板上に引っ張り応力を有する層間絶縁膜や配線用金属膜等の形成された半導体装置において、ウェハの反りを抑制できる半導体装置を提供する。

【解決手段】 半導体素子が形成された半導体基板10と、半導体基板10上に堆積された1または複数層の配線用金属膜16a、16b、18を備えてなる半導体装置であって、1または複数層の配線用金属膜の内、1つの配線用金属膜の堆積によって生じるウェハ反り量の絶対値が最大となる第1配線用金属膜18の下層側及び上層側の少なくとも何れか一方側に、ウェハ反り量を緩和する応力緩和膜17を備え、応力緩和膜17が圧縮応力を有し、第1配線用金属膜18が引っ張り応力を有し、応力緩和膜17の堆積によって生じるウェハ反り量の絶対値が、第1配線用金属膜18の堆積によって生じるウェハ反り量の絶対値より小さい。

(もっと読む)

歪みシリコン窒化物膜及び該膜を含むデバイスの作製方法

歪みSiN膜及び該歪みSiN膜を含む半導体デバイスの作製方法。当該方法は、シリコン先駆体を含む気体に前記基板を曝露する工程、第1レベルのプラズマ出力のプラズマ源によって励起されて前記シリコン先駆体と第1反応特性で反応する窒素先駆体を含む気体に前記基板を曝露する工程、及び、前記第1レベルとは異なる第2レベルのプラズマ出力のプラズマ源によって励起されて前記シリコン先駆体と第2反応特性で反応する窒素先駆体を含む気体に前記基板を曝露することで、前記の基板上に作製されたシリコン窒化物膜の特性が前記歪みSiN膜を供するように変化する、工程を有する。  (もっと読む)

(もっと読む)

フッ素系薄膜の成膜方法及び半導体装置の製造方法

【課題】低誘電率且つ化学的に安定なフッ素系薄膜を成膜することができるフッ素系薄膜の成膜方法及び該成膜方法を用いた半導体装置の製造方法の提供。

【解決手段】本発明のフッ素系薄膜の成膜方法は、基板上にフッ素系樹脂からなる薄膜を成膜するフッ素系薄膜の成膜方法であって、前記基板上にガスを照射するガス照射工程と、前記フッ素系樹脂をプラズマ化するプラズマ化工程とを含む。イオン化蒸着法、イオンプレーティング法、レーザアブレション法、イオンビームスパッタ法から選択される少なくとも1種によりフッ素系樹脂からなる薄膜を成膜する態様等が好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】最下層配線に埋め込み配線を有する半導体装置の信頼性を向上させる。

【解決手段】

半導体基板1の主面にMISFETQn,Qpが形成され、その主面上に絶縁膜10,11が形成されている。絶縁膜10,11にはコンタクトホール12が形成されてプラグ13が埋め込まれている。プラグ13が埋め込まれた絶縁膜11上には、絶縁膜14,15,16が形成され、絶縁膜14,15,16に開口部17が形成されて配線20が埋め込まれている。絶縁膜15は、開口部17を形成するために絶縁膜16をエッチングする際のエッチングストッパ膜であり、シリコンと炭素を含有する。絶縁膜11は吸湿性が高く、絶縁膜15は耐湿性が低いが、それらの間に絶縁膜14を介在させ、絶縁膜14を絶縁膜11よりもSi(シリコン)原子の数密度が大きな膜とすることで、電気的に弱い界面が形成されるのを防止する。

(もっと読む)

成膜方法及び成膜装置

【課題】比較的低温で成膜しても含有する炭素濃度を多くさせてクリーニング時のエッチングレートを比較的小さくでき、もってクリーニング時の膜厚の制御性を向上させることができる成膜方法を提供する。

【解決手段】被処理体Wが収容されて真空引き可能になされた処理容器4内に、シラン系ガスと窒化ガスと炭化水素ガスとを供給して前記被処理体の表面にSiCN膜よりなる薄膜を形成する成膜方法において、前記シラン系ガスと前記窒化ガスと前記炭化水素ガスとをそれぞれ一定の供給期間でパルス状に供給する供給工程と供給を停止する停止工程とよりなる1サイクルを複数回繰り返し実行してプラズマを用いることなく前記薄膜を形成する。これにより、比較的低温で成膜しても含有する炭素濃度を多くさせてクリーニング時のエッチングレートを比較的小さくでき、もってクリーニング時の膜厚の制御性を向上させる。

(もっと読む)

絶縁膜の形成方法およびこれを用いた半導体装置

【課題】半導体装置の製造工程において、フッ素、HFまたは低分子のフルオロカーボン類の脱離が少なく、上に積層する膜との密着性が優れた絶縁膜の形成方法、およびその形成方法を用いて形成された半導体装置を提供する。

【解決手段】基板上にフルオロカーボン膜を形成する工程、および、その表面と、酸素、オゾン、一酸化炭素、二酸化炭素および亜酸化窒素などの酸化性ガスを含む処理ガス、とを接触させる工程を有する絶縁膜の形成方法。

(もっと読む)

絶縁膜の形成方法およびこれを用いた半導体装置

【課題】半導体装置の製造工程において、フッ素、HF、または、低分子のフルオロカーボン類の脱離が少なく、上に積層する膜との密着性が優れた絶縁膜の形成方法、およびその形成方法を用いて形成された半導体装置を提供する。

【解決手段】基板上にフルオロカーボン膜を形成する工程、および、その表面と、SF6、NF3、SiF4、PF5およびBF3などの無機フッ化ガスを含む処理ガスとを接触させる工程を有する絶縁膜の形成方法。

(もっと読む)

半導体装置とその製造方法

【課題】新規な特徴を有する半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板10の上方に第1絶縁膜25を形成する工程と、第1絶縁膜25の所定の深さに不純物をイオン注入することにより、第1絶縁膜25に不純物層22を形成する工程と、不純物層22を形成した後、第1絶縁膜をアニールすることにより、不純物層22をバリア絶縁膜23に改質する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】半導体集積回路におけるコンタクトホールのような微細穴パターンを形成する場合に、形状を精度良くパターニングし且つ加工すること。

【解決手段】コンタクトホールを形成するためにハードマスクを作製する。このハードマスクはそれぞれ別のフォトリソグラフィ工程により作製され、素子形成領域17と平行な方向に形成された第1のハードマスク32と、素子形成領域17と交差する方向に形成された第2のハードマスク34との重ね合わせで構成されている。第1のハードマスク32と第2のハードマスク34はストライプ状の開口を有し、その交差部にコンタクトホールの開口が形成される。このような二回露光二回加工プロセスにより作製されるハードマスクを用いることで、穴状のパターンのレチクルでパターニングを行うよりも微細でより忠実なコンタクトホールの加工が可能となる。

(もっと読む)

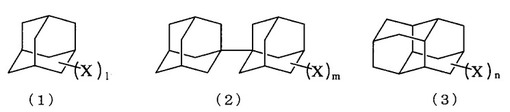

多環脂環式化合物を前駆体物質とする薄膜、及びその製造方法

【課題】低誘電率、高強度、高耐熱性を具備する薄膜を得ること及びその製造方法を提供する。

【解決手段】下記式(1)、(2)及び(3)で表される多環脂環式化合物から選ばれる1種類以上の多環脂環式化合物を前駆体物質とする薄膜であり、多環脂環式化合物をプラズマ重合法により薄膜とする製造方法であり、低誘電率、高強度、高耐熱性を備えた薄膜となり、CPU、DRAM、フラッシュメモリ等の半導体装置、薄膜上にパターン形成し、回路を描いて作製された薄膜トランジスタに代表される情報処理用小型電子回路装置、高周波通信用電子回路装置等の電子回路装置、画像表示装置、表面保護膜、光学膜等として使用することができる。 (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】MOSトランジスタを構成する材料によって熱処理温度が制限される半導体装置の層間絶縁膜の形成において、CMP平坦化処理工程でスクラッチの発生を抑制することが可能な比較的低温のプロセスで形成されるO3/TEOS系の熱−USG膜からなる層間絶縁膜を有する半導体装置の製造方法を得ること。

【解決手段】ソース/ドレイン領域となる拡散層16および/またはゲート電極13上にシリサイド膜14,17を有する電界効果型トランジスタがシリコン基板1上に形成された半導体基材上に、熱CVD法によって不純物が導入されていないシリコン酸化膜からなる層間絶縁膜22を形成する工程と、シリサイド膜14,17に影響を与えない程度の温度で、シリコン酸化膜中に混入したガス状反応生成物を除去する工程と、を含む。

(もっと読む)

絶縁膜積層体、絶縁膜積層体の製造方法、半導体装置及び半導体装置の製造方法

【課題】ボロン漏れの抑制とリーク電流増加の抑制とを同時に実現可能な、絶縁膜及びこの絶縁膜を備えた半導体装置と、絶縁膜の製造方法及び半導体装置の製造方法を提供する。

【解決手段】微結晶組織からなるハフニウム含有窒化シリコン酸化物層3aと、非晶質組織からなるハフニウム含有窒化シリコン酸化物層3bとが半導体基板2上に積層されてなる積層膜からなり、積層膜の窒素濃度が15原子%以上40原子%以下の範囲であることを特徴とする半導体装置用の絶縁膜積層体3を採用する。

(もっと読む)

絶縁ゲート電界効果トランジスタの製造方法。

【課題】ゲート電極の上方に層間絶縁層を形成するときに、ゲート電極に対向する基体の部分が酸化されることが無い、絶縁ゲート電界効果トランジスタの製造方法を提供する。

【解決手段】絶縁ゲート電界効果トランジスタの製造方法は、(a)ソース/ドレイン領域13、チャネル形成領域12、チャネル形成領域12上に形成されたゲート絶縁膜30、ソース/ドレイン領域13を覆う絶縁層21、及び、チャネル形成領域12の上方の絶縁層21の部分に設けられたゲート電極形成用開口部22を備えた基体を準備し、(b)ゲート電極形成用開口部22内を導電材料層31,32で埋め込むことでゲート電極23を形成し、次いで、(c)絶縁層21を除去し、その後、(d)全面に、第1の層間絶縁層41、第2の層間絶縁層42を、順次、成膜する工程を備え、前記工程(d)において、酸素原子を含まない成膜雰囲気中で第1の層間絶縁層41を成膜する。

(もっと読む)

多孔質低誘電率層の製造方法及び構造、相互接続処理方法及び相互接続構造

【課題】多孔質低誘電率層を形成する方法が、記載されている。

【解決手段】CVDプロセスは、基板に導入され、ここで、枠体前駆体及びポロゲン前駆体は供給される。枠体前駆体の供給の終了期間において、CVDプロセスの生成物の密度と否定的に相関している少なくとも一つの堆積パラメータの値は、減少する。

(もっと読む)

低誘電率膜の成膜装置

【課題】 極めて低い誘電率を有するホウ素炭素窒素膜を成膜することができる

成膜装置を提供すること。

【解決手段】 成膜室1内にプラズマを生成するプラズマ生成手段2と、窒素、ホウ素および炭素材料を導入する導入手段5,9,10と、プラズマの下部または内部に基板61を保持する手段6と、基板保持部を昇温する昇温手段7とを備えることを特徴とする成膜装置。

(もっと読む)

半導体装置およびその製造方法

【課題】Cuの拡散を防止することができ、かつ、層間の誘電率が高くなることを抑制することができる半導体装置およびその製造方法を提供すること。

【解決手段】 ウエハWにCu配線層6を形成し、Cu配線層6の上に、炭化水素ガスを含む処理ガスを用いたCVDによりCu拡散バリアとしてアモルファスカーボン膜7を成膜し、その上にLow−k膜8を形成する。

(もっと読む)

窒化アルミニウムを使用することによる微細構造デバイス内の銅系メタライゼーション構造の信頼性向上

自己制限プロセスシーケンスによって窒化アルミニウム層(106)を形成することにより、銅系メタライゼーション層の界面特性を大幅に改善できる一方で、層スタックの全体的な誘電率を低いレベルに保つことができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体基板としてのシリコンに形成されるp型MOSFETにストレスの影響を与え難い結晶方向が[100]方向のチャネルを形成することができる45度ノッチウエハを使用してもn型MOSFETに有利なストレスをかけることができる半導体装置を提供する。

【解決手段】半導体基板1に形成された少なくとも1つのMOSFETと、半導体基板1上にこのMOSFETを被覆するように形成されたコンタクトストップライナ膜7とを備えている。コンタクトストップライナ膜7は窒素濃度が互いに異なる複数層のシリコン窒化膜から構成されている。シリコン半導体基板に形成されるp型MOSFETにストレスの影響を与え難い結晶方向が[100]方向のチャネルを形成することができる45度ノッチウエハを使用してもn型MOSFETに有利な高いストレスをかけることができる。

(もっと読む)

ウェットエッチングアンダカットを最小にし且つ超低K(K<2.5)誘電体をポアシーリングする方法

【課題】 基板上の膜を処理する方法の提供。

【解決手段】 一態様において、方法は、シリコンと、炭素とを含み、所望により酸素及び/又は窒素を含んでもよい薄層を膜上に堆積させることによりフォトレジストが膜から除去された後のパターン形成された低誘電率膜を処理するステップを含む。薄層は、パターン形成された低誘電率膜に炭素を多く含む疎水性表面を与える。薄層は、また、続いての湿式洗浄プロセスと、低誘電率膜上に続いて堆積される層の前駆物質による浸透から低誘電率膜を保護する。

(もっと読む)

アモルファスカーボン膜、半導体装置、成膜方法、成膜装置及び記憶媒体

【課題】比誘電率を低く抑えながら、弾性率が高く、また熱収縮率が小さいアモルファスカーボン膜及びその膜を備えた半導体装置、並びにアモルファスカーボン膜を成膜する技術を提供する。

【解決手段】成膜時にSi(シリコン)の添加量を制御しながらアモルファスカーボン膜を成膜しているので、比誘電率を3.3以下の低い値に抑えながら、弾性率が高く、また熱収縮率の小さいアモルファスカーボン膜を得ることができる。従ってこのアモルファスカーボン膜を、半導体装置を構成する膜として用いた場合に膜剥がれなどの不具合が抑えられ、その結果、低誘電率であり、かつCuなどの金属に対するバリア性を有するといった利点を生かすことができる。

(もっと読む)

141 - 160 / 260

[ Back to top ]