Fターム[5F033SS01]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 原料ガス (1,958)

Fターム[5F033SS01]の下位に属するFターム

Fターム[5F033SS01]に分類される特許

61 - 80 / 260

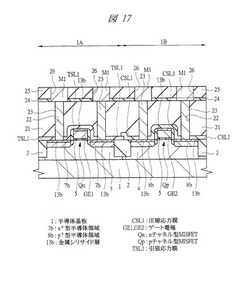

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体界面のダングリングボンドを終端させて、リーク電流が少ない半導体装置の製造方法を提供する。

【解決手段】ボンディングパッド40が設けられる最上層の配線層39の上に、フッ素を含んだ介在層41としてCVD法によりよって形成されたフッ素含有酸化シリコン膜(SiOF)を設ける。この上にパッシベーション膜42としてプラズマCVD法により形成した窒化シリコン膜を設け、フッ素に対するバリアとする。この後熱処理を行い、フッ素をシリコン基板の表面に拡散させる。

(もっと読む)

多層膜の形成方法及び表示パネルの製造方法

【課題】予め定めた形状にパターニングされた導電層の上下に配置されている絶縁層のそれぞれにコンタクトホールを形成し、これらコンタクトホールを介して互いに異なる層として形成された2つの導電層を互いに電気的に接続する場合であっても、導電不良が生じ難い多層膜の形成方法及び表示パネルの製造方法を提供する。

【解決手段】基板2上に成膜された第1導電層40上に第1絶縁層20を成膜し、前記第1絶縁層20上に第2導電層41を成膜し、前記成膜した第2導電層41をパターニングし、パターニングされた前記第2導電層41を覆うように前記基板2上に第2絶縁層25を成膜し、前記第2絶縁層25上に該第2絶縁層25よりもエッチング速度が速い第3絶縁層26を成膜し、前記第1絶縁層20、前記第2絶縁層25及び前記第3絶縁層26に対して前記第1導電層40の少なくとも一部を露出させるコンタクトホールを一括形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、しきい値電圧のばらつきが大きいトランジスタのしきい値電圧を調整してしきい値電圧のばらつきを低減することを可能にする。

【解決手段】基板11と絶縁層12とシリコン層13が積層されてなるSOI基板10の該シリコン層13の表面側にトランジスタ20を形成する工程と、SOI基板10上に、トランジスタ20を被覆する第1絶縁膜30と、トランジスタ20に電気的に接続される配線部40とを形成する工程と、配線部40を通じてトランジスタ20のしきい値電圧を測定する工程と、第1絶縁膜30表面に第2絶縁膜を介して支持基板を形成する工程と、SOI基板10の裏面側の基板11と絶縁層12の少なくとも一部を除去する工程と、測定されたしきい値電圧に基づいてトランジスタ20のしきい値電圧を調整する工程を有する。

(もっと読む)

酸素含有前駆体を用いる誘電体バリアの堆積

低誘電率及び優れた電気特性等の改良されたバリア誘電体特性を有する、ケイ素、炭素、酸素及び水素を有する前駆体を含む誘電体バリアフィルムを堆積させるための方法を与える。この方法は、相互接続構造のためのダマシン又は二重ダマシン集積で、又は他の誘電体バリア用途で用いられるバリア層に関して重要となるであろう。この例では、バリア性能を改良する特定の構造特性が注目される。  (もっと読む)

(もっと読む)

低誘電率膜の堆積処理方法、基板処理システム、デュアルダマシン構造の形成方法、およびデュアルダマシン構造

【課題】集積回路製造工程において、ガスを化学的に反応させて化学気相成長又はCVDにより、低誘電率膜の堆積処理方法を提供する。

【解決手段】約10Wから約200Wの一定RFパワーレベルか、または約20Wから約500WのパルスRFパワーレベルで、1以上のシリコン化合物と酸化ガスからなるプロセスガスから、パターン化された金属層上にコンフォーマルライニング層を堆積する工程と、前記ライニング層上にギャップ充填層を堆積させる工程とを含む低誘電率膜の堆積処理方法。

【効果】シリコン酸化物は、配線間の静電結合を弱めて、1つの堆積チャンバで高信頼性のデュアルダマシン構造を製造する集積プロセスにおいてさらに有効である。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造に使用されるシリコン酸化膜の下地依存性を改善することによって、シリコン酸化膜の狭スペースへの埋め込み性やモフォロジーを向上させる。

【解決手段】半導体素子部を有するSi基板1の表面に有機基を含まないSi含有分子を吸着させ、Si含有分子による吸着層12を形成する。あるいは、Si基板1上にSiリッチなSiN系保護膜を形成する。吸着層12またはSiリッチなSiN系保護膜上から有機シリコン材料ガスとオゾン等の活性化された酸素を含むガスとを供給し、Si基板1上にシリコン酸化物からなる絶縁膜13を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低誘電率膜を用いた層間絶縁膜SiOCH膜をCMPプロセスにおけるダメージから保護しつつ、配線間層間絶縁膜SiOCH膜の実効誘電率を低減する。

【解決手段】半導体装置100は、SiOCH膜10の表層が改質されることにより形成された、SiOCH膜10よりも炭素濃度が低くかつSiOCH膜10よりも酸素濃度が高い表面改質層20が設けられるとともに、Cu配線50の表面及び表面改質層20の表面に接するキャップ絶縁膜60を有している。このため、SiOCH膜10全体の誘電率の上昇を低減しつつ、CMPプロセスにおいて親水性の表面改質層20が露出することによって水滴が残りにくくなり、CMPプロセス後のパーティクルの残留やウォーターマークの発生を低減できる。

(もっと読む)

基板処理装置

【課題】休止の長期化や配管汚染の危惧を防止しつつ液体原料を補給可能とする基板処理装置を提供する。

【解決手段】液体原料80を供給するためのタンク81と、液体原料80を気化させる気化器83とを具備し、気化器83が液体原料80を気化させた気化ガスを処理室内に供給しウエハ上に成膜する基板処理装置において、タンク81に、液体原料80を補給するための補給容器91と、タンク81内を減圧する排気管93とを接続し、補給容器91内の圧力をタンク81内の圧力よりも高くすることにより、液体原料80を補給容器91内からタンク81内へ補給する。補給容器91には洗浄液95を貯蔵した洗浄液容器96を接続する。交換作業は補給容器91について実施すれば済むため、基板処理装置の休止の長期化や配管汚染の危惧を防止しつつ、液体原料を補給することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、絶縁膜の誘電率を低く維持すると共に、半導体装置の信頼性を高めること。

【解決手段】シリコン基板1の上方に層間絶縁膜29を形成する工程と、層間絶縁膜29に配線溝29aを形成する工程と、層間絶縁膜29の上面と配線溝29aの中とに導電膜27を形成する工程と、導電膜27を研磨することにより、層間絶縁膜29の上面から導電膜27を除去すると共に、配線溝29aの中に導電膜27を残す工程と、導電膜27の表面を還元性プラズマに曝す工程と、導電膜27の表面にシリサイド層34を形成する工程と、シリサイド層34の表面に窒化層36を形成する工程と、炭素を含むガス又は液に層間絶縁膜29の上面を曝す工程と、層間絶縁膜29の上面に紫外線を照射する工程と、導電膜27の上にバリア絶縁膜40を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】より簡易な工程(処理内容)を用いて、導電層表面にキャップ膜を形成することを可能とする。

【解決手段】 基板の上に層間絶縁膜を形成する工程と、前記層間絶縁膜中に開口部を形成する工程と、前記開口部とを充填する導電層を形成する工程と、前記導電層の表面にキャップ膜を形成する工程と、を含み、前記キャップ膜を形成する工程において、導電層の表面の還元処理と、膜形成とが同時に行われる。

(もっと読む)

半導体装置

【課題】 動作マージンを確保しつつ、微細化を可能とするSRAMセルを提供する。

【解決手段】

SRAMセルが、それぞれ、NMOSドライバとPMOSロードとが接続された第1、第2のインバータを含み、それぞれのインバータの内部ノードが他方のインバータの入力に接続されたフリップフロップ回路と、第1、第2のビット線と、第1、第2のインバータの内部ノードと第1、第2のビット線との間に接続された第1、第2のNMOSトランスファトランジスタであって、それぞれ、絶縁ゲート電極構造の両側に形成された第1、第2のn型ソース/ドレイン領域と、を含み、2つの第1のn型ソース/ドレイン領域が第1、第2のインバータの内部ノードに接続され、2つの第2のn型ソース/ドレイン領域が第1、第2のビット線に接続された第1、第2のNMOSトランスファトランジスタと、第1のn型ソース/ドレイン領域を覆って形成された圧縮応力膜と、第2のn型ソース/ドレイン領域を覆って形成された引張応力膜と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】、デュアルダマシン法により低誘電率膜に埋め込まれた配線層を形成する場合において、オープン不良の発生を伴うことなく、設計通りの配線層を形成し得る半導体装置の製造方法を提供する。

【解決手段】ビアホール形成領域の低誘電率膜42、第1のハードマスク44及び第2のハードマスク46を除去することにより、低誘電率膜42にビアホール52を形成する工程と、配線トレンチ形成領域の第2のハードマスク46を除去する工程と、第2のハードマスク46をマスクとして第1のハードマスク44をエッチングすることにより、配線トレンチ形成領域の第1のハードマスク44を除去する工程とを有し、配線トレンチ形成領域の第1のハードマスク44を除去する工程では、ビアホール52底のバリア膜40をもエッチングすることにより、ビアホール52底のバリア膜40を部分的に除去する。

(もっと読む)

障壁層と多様な液体前駆体から堆積される多孔質低k膜との間の付着を促進するための方法

基板を処理するための方法が提供され、ここで第1の有機シリコン前駆体、第2の有機シリコン前駆体、ポロゲン、および酸素源が、処理チャンバーに提供される。第1の有機シリコン前駆体は、一般に低い炭素含有量を有する化合物を含む。第2の有機シリコン前駆体は、より高い炭素含有量を有する化合物を含む。ポロゲンは、炭化水素化合物を含む。RF電力は、基板上に膜を堆積させるために印加され、さまざまな反応物の流れの流量は、膜の部分が堆積されるにつれて炭素含有量を変化させるために調節される。一実施形態では、堆積膜の最初の部分は、低い炭素含有量を有し、従って酸化物のようであり、一方次に続く部分は、より高い炭素含有量を有し、オキシ炭化物のようになる。他の実施形態は、酸化物のような最初の部分を特徴としない。膜を後処理するステップは、より高い炭素含有量を有する膜の部分に細孔を発生させる。  (もっと読む)

(もっと読む)

半導体装置用絶縁膜、半導体装置用絶縁膜の製造方法及び製造装置、半導体装置及びその製造方法

【課題】低誘電率、低リーク電流、高機械的強度の特性を備え、これらの特性の経時変化が小さく、耐水性に優れた半導体装置用絶縁膜、当該半導体装置用絶縁膜の製造方法及び製造装置、半導体装置及びその製造方法を提供する。

【解決手段】所定のアルキルボラジン化合物を気化した原料ガスを含有するガスをチャンバ2内に供給し、誘導結合型プラズマ発生機構(4、5、6)を用いて、チャンバ2内に電磁波を入射して、ガスをプラズマとし、プラズマのプラズマ拡散領域に基板8を配置し、プラズマにより解離されたアルキルボラジン化合物中のボラジン骨格系分子を基本単位として気相重合し、半導体装置用絶縁膜として基板8に成膜する。

(もっと読む)

薄いバリア層を用いた多孔性誘電体への溶媒および溶液の侵入の阻止および低減

基板を処理するための方法および装置が提供される。基板上に多孔性誘電体層が形成される。いくつかの実施形態では、誘電体を緻密な誘電体層によって覆うことができる。誘電体層がパターン形成され、基板の上に緻密な誘電体層が共形的に堆積される。緻密な共形の誘電体層は、多孔性誘電体層の孔を、孔に浸入する可能性がある化学種と接触しないように密封する。緻密な共形の封孔誘電体層の、フィールド領域とパターン開口部の底部とを覆う部分が、指向性の選択的なエッチングによって除去される。  (もっと読む)

(もっと読む)

パターン形成キャップを用いるエアギャップ形成と一体化

【課題】 膜をパターン形成する方法及びこれらの得られた構造を提供する。

【解決手段】 実施形態において、基板、例えば、ダマシン層の上にアモルファス炭素マスクを形成する。アモルファス炭素マスクの上にスペーサ層を堆積させ、スペーサ層をエッチングして、スペーサを形成するとともにアモルファス炭素マスクをさらす。アモルファス炭素マスクを選択的にスペーサまで除去して、基板層をさらす。ギャップ充填層がスペーサの周りに堆積されて、基板層を覆うがスペーサをさらす。スペーサを除去して、選択的に基板の上にギャップ充填マスクを形成する。ギャップ充填マスクのパターンは、一実施態様においては、ダマシン層に転写されて、IMDの少なくとも一部を除去するとともにエアギャップを形成する。

(もっと読む)

61 - 80 / 260

[ Back to top ]