Fターム[5F033SS01]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 原料ガス (1,958)

Fターム[5F033SS01]の下位に属するFターム

Fターム[5F033SS01]に分類される特許

21 - 40 / 260

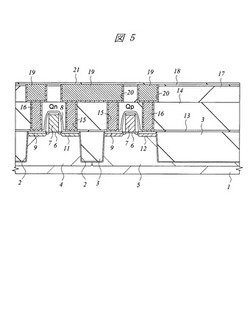

半導体集積回路装置の製造方法

【課題】プラズマCVD法を用いてCu配線上に良好な拡散バリア膜を形成する技術を提供する。

【解決手段】ダマシン法を用いて形成したCu配線19上にCuの拡散を防止する窒化シリコン膜21を形成する工程は、Cu配線19が形成された基板1をプラズマCVD装置のチャンバ内に搬入し、基板1を所定の温度に加熱する工程と、チャンバ内にアンモニアを供給し、第1のRFパワーでアンモニアをプラズマ分解することによって、Cu配線19の表面を還元処理する工程と、RFパワーが印加された状態で、チャンバ内にアンモニアとモノシランとを含む原料ガスを供給し、第2のRFパワーでアンモニアとシラン系ガスとをプラズマ分解することによって、Cu配線19上に窒化シリコン膜21を形成する工程とを含んでいる。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ビア深さのバラツキを抑制することができる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に、SiおよびCを含むキャップ絶縁膜を形成する工程と、キャップ絶縁膜上に、キャップ絶縁膜と比較して、シリコン原子数に対する炭素原子数の組成比が高い、有機シリカ膜を形成する工程と、不活性ガス、Nを含むガス、フッ化炭素ガスおよび酸化剤ガスを含む混合ガスを用いたプラズマ処理により、有機シリカ膜に、異なる開口径を有する2以上の凹部を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】どのようなレイアウトの配線に対しても、個々の配線ごとにエアギャップ部を設ける。エアギャップ部によって、配線の寄生容量を低減する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜内に埋め込まれた配線と、配線の側面と層間絶縁膜との間に設けられたエアギャップ部と、を有する。半導体装置の製造方法は、配線の側面上に第2のサイドウォール膜を形成した後、第2のサイドウォール膜の一部が露出するように第1の絶縁膜を形成する。次に、第2のサイドウォール膜を除去することによりサイドスペースを形成した後、サイドスペースが埋め込まれないように第2の絶縁膜を形成することによりサイドスペースから構成されるエアギャップ部を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】無機材料を用いてコストの低減を図りながら、応力集中によるクラックを回避しつつ、銅配線を覆うことができるパッシベーション膜を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10は、層間絶縁膜25と、層間絶縁膜25上に突出して形成され、銅を主成分とする材料からなる配線27と、配線27を覆うように形成されたパッシベーション膜30とを含む。パッシベーション膜30は、配線27側から順に第1窒化膜31、中間膜33および第2窒化膜32を積層した積層膜からなる。中間膜33は、第1および第2窒化膜31,32とは異なる絶縁材料(たとえば酸化物)からなる。

(もっと読む)

炭窒化珪素膜及び炭窒化珪素膜の成膜方法

【課題】加水分解や酸化に対する耐性が高く、かつ、低誘電率な炭窒化珪素(SiCN)膜を提供する。

【解決手段】珪素、炭素、水素を含有する前躯体分子からなる第1のガスと、窒素を含有する第2のガスとからなる原料ガスを用いてプラズマCVD法によって成膜された炭窒化珪素膜であって、前記炭窒化珪素膜を構成する窒素原子でSi−N−Si結合として存在している窒素原子の量が、前記炭窒化珪素膜中の全窒素原子の量の7%以上であることを特徴とする炭窒化珪素膜。

(もっと読む)

窒素ドープされたアモルファスカーボンハードマスク

半導体装置及びその製造方法

【課題】N型トランジスタ及びP型トランジスタの双方で可及的に製造工程を共通にして、工程数の可及的な削減を図るも、N型トランジスタ及びP型トランジスタの夫々に適合した応力を適宜印加し、トランジスタ性能の大幅な向上を実現する。

【解決手段】N型トランジスタでは、ゲート電極14a及びサイドウォール絶縁膜17を覆うようにN型領域10aの全面に引張応力膜22を形成し、P型トランジスタでは、サイドウォール17絶縁膜上のみに引張応力膜22を形成し、更にゲート電極14b及び引張応力膜22を覆うようにP型領域10bの全面に圧縮応力膜24を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

(もっと読む)

半導体装置の製造方法

【課題】貫通孔となるべきアスペクト比が20以上の深孔を埋め込む貫通電極金属としては、埋め込み特性が良好なタングステンが使用されることが多いが、通常のドライエッチングによる深孔は、ボッシュプロセスによるものに比べて寸法の大きなものとなる。この比較的大きな深孔を埋め込むためには、必然的にウエハの表面に成膜すべきタングステン膜の膜厚も厚くなり、その結果、ウエハの反りが、プロセスを正常に実行できる限界を超える程度にまで増加する。また、このような問題が許容できる限度内である場合にも、タングステン膜を堆積する際に、ウエハの周辺で下地膜の剥がれが発生する等の問題がある。

【解決手段】本願発明は、貫通ビアを形成するための非貫通孔をタングステン部材で埋め込むに当たり、ウエハの周辺部において、下地のバリアメタル膜の外延部より内側に、タングステン部材の外延部を位置させるように成膜を実行するものである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】絶縁膜の比誘電率を容易かつ十分に低下させる。

【解決手段】半導体装置の製造方法では、それぞれ環状SiO構造を主骨格とし互いに構造が異なる2種類以上の有機シロキサン化合物原料を混合した後で気化する。又は、それら2種類以上の有機シロキサン化合物原料の混合と気化とを一度に行うことによって、気化ガスを生成する。そして、その気化ガスをキャリアガスとともに反応炉に輸送する。そして、反応炉にてその気化ガスを用いたプラズマCVD法又はプラズマ重合法によって多孔質絶縁膜を成膜する。

(もっと読む)

低水分誘電体膜を形成する方法

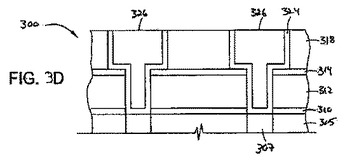

半導体装置の製造方法及び基板処理装置

【課題】W等の金属膜の酸化を防止しつつ、金属膜上に低温で酸化膜を形成することができる半導体装置の製造方法を提供する。

【解決手段】表面に金属膜が形成された少なくとも1枚のウエハ310を処理室318内に搬入する工程と、金属膜を含むウエハ310表面にシリコンを含む酸化膜を形成する工程と、を少なくとも備える半導体装置の製造方法であって、酸化膜の形成工程は、ウエハ310を所定の温度に加熱しながら、シリコン原子を含む第1の反応物質を処理室318内に供給する工程と、ウエハ310を所定の温度に加熱しながら、酸素原子を含む第2の反応物質と、水素とを処理室318内に供給する工程と、を有し、処理室318内の加熱温度と、水素に対する第2の反応物質の供給比を制御することにより、金属膜の酸化を制御する。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

プラズマ化学気相堆積による、有機官能基と共にシリコンを含有するハイブリッド前駆体を使用する超低誘電材料

低誘電率層を基板上に堆積するための方法が提供される。一実施形態では、本方法は、1種または複数のオルガノシリコン化合物をチャンバに導入するステップであって、1種または複数のオルガノシリコン化合物がシリコン原子およびこのシリコン原子に結合されたポロゲン成分を含むステップと、1種または複数のオルガノシリコン化合物を、RF電力の存在下で反応させることにより、低誘電率層をチャンバ内の基板上に堆積させるステップと、低誘電率層からポロゲン成分が実質的に除去されるようにこの低誘電率層を後処理するステップとを含む。任意選択で、不活性キャリアガス、酸化ガス、またはその両方を、1種または複数のオルガノシリコン化合物と共に処理チャンバ内に導入してもよい。後処理プロセスは、堆積した材料の紫外線硬化とすることができる。UV硬化プロセスは、熱または電子ビーム硬化プロセスと同時にまたは連続して使用してもよい。低誘電率層は、良好な機械的性質および望ましい誘電率を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、炭化シリコン薄膜の機械強度を高め、膜の消失や剥離を防止する。

【解決手段】 ポーラスな誘電率低誘電率絶縁膜上に−CH2−結合が環状になってSiと結合し且つ二重結合を含む官能基を有する原料を用いて炭化シリコン薄膜を形成する工程と、前記炭化シリコン薄膜を所定パターンにエッチングしてハードマスクを形成する工程と、前記ハードマスクをエッチングマスクとして前記低誘電率絶縁膜をエッチングして配線形成用溝或いはビアホールの少なくとも一方を形成する工程とを設ける。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体製造装置

【課題】有機シリカ膜を成膜したのちのプラズマ反応室の内壁のクリーニング時間を短縮する。

【解決手段】まずプラズマ反応室内壁をプリコート膜で被覆する(プリコート工程)。次いで基板上に、シリコン炭素組成比(C/Si)が1以上である有機シリカ膜を成長させる(基板処理工程)。次いで、基板を取り出した後、プラズマ反応室内壁に付着した有機シリカ膜とプリコート膜とをプラズマを用いて除去する(クリーニング工程)。プリコート膜としては、基板上に成膜された有機シリカ膜よりも少なくとも炭素含有率が低い有機シリカ膜である高酸素含有プリコート膜を用いる。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】高いアスペクト比で狭い幅の溝に、シリコン酸化膜を埋め込むことの可能な、スループットの高い半導体製造方法を提供する。

【解決手段】半導体装置の製造方法において、基板を処理室内へ搬入する工程と、炭素及び水素を含むシリコン化合物ガスを処理室内へ供給して、処理室内を第1の圧力の状態にする工程と、処理室内を前記第1の圧力にした状態において、処理室内へ供給されたシリコン化合物ガスに紫外光を照射して、基板上にシリコン酸化膜を形成する工程と、処理室内を前記第1の圧力よりも低い第2の圧力の状態にする減圧処理工程とを行う。これにより、高アスペクト比で狭い幅の溝内に、緻密なシリコン酸化膜を形成することができる。

(もっと読む)

21 - 40 / 260

[ Back to top ]