Fターム[5F033SS01]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 原料ガス (1,958)

Fターム[5F033SS01]の下位に属するFターム

Fターム[5F033SS01]に分類される特許

41 - 60 / 260

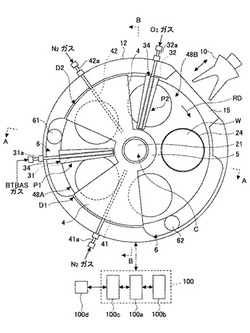

成膜装置及び成膜方法

【課題】第1の反応ガスと第2の反応ガスとの混合を効果的に抑制することにより、回転テーブルの回転速度の増大を通してスループットの向上を図る。

【解決手段】本成膜装置は、回転テーブルの中心と外周上の異なる2つの点とをカバーするように延び第1及び第2の領域に分ける分離領域であり、第1分離ガスで分離領域を第1及び第2の領域より高圧に維持可能な分離領域;第1分離ガスの回転テーブルの中心から外周への流れを抑制して、分離領域を第1及び第2の領域より高圧に制御する圧力制御部;第1の領域にて回転テーブルへ第1反応ガスを供給する第1反応ガス供給部;第2の領域にて回転テーブルへ第2反応ガスを供給する第2反応ガス供給部;第1反応ガスと分離領域からの第1分離ガスとの両方を合流して第1の領域を通して排気する第1排気口;及び第2反応ガスと分離領域からの第1分離ガスとの両方を合流して第2の領域を通して排気する第2排気口を備える。

(もっと読む)

半導体デバイスの層内または層間誘電体としての超低誘電率材料

【課題】約2.6以下の誘電率を有する超低誘電率材料およびその作製する方法を提供すること。

【解決手段】Si原子、C原子、O原子およびH原子を含み、共有結合3次元ネットワーク構造を有し、2.6以下の誘電率を有する、熱的に安定な超低誘電率膜を提供する。この誘電率膜は、さらに、共有結合環状ネットワークを有することもできる。共有結合3次元ネットワーク構造は、Si−O共有結合、Si−C共有結合、Si−H共有結合、C−H共有結合およびC−C共有結合を含み、必要ならFおよびNを含むこともできる。この膜では、必要ならSi原子の一部をGe原子で置換することもできる。この誘電率膜は、1.3マイクロメートル以下の厚さを有し、毎秒10−10メートル以下の水中での亀裂成長速度を有する。さらに、BEOL絶縁体、キャップまたはハード・マスク層として本発明の誘電膜を含むバック・エンド・オブ・ライン(BEOL)相互接続構造も提供する。

(もっと読む)

成膜方法及び半導体装置

【課題】層間絶縁膜と配線金属との間に形成されるバリア膜について、配線金属を構成する元素や層間絶縁膜を構成する元素に対して高いバリア性を提供する。

【解決手段】処理容器内に基板を載置する載置台51と周方向に沿って多数のスリットが形成された平面アンテナ部材82とを対向して設け、導波管からのマイクロ波を前記平面アンテナ部材を介して処理容器内に供給する。一方処理容器の上部からArガスなどのプラズマ発生用のガスを供給すると共にこのガスの供給口とは異なる位置から原料ガスである例えばトリメチルシランガスと窒素ガスとを供給することでこれらガスをプラズマ化し、更に載置台51の上面の単位面積当たりに供給されるバイアス用の高周波電力が0.048W/cm2以下となるようにバイアス用の高周波電力を印加する。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜の膜強度を十分に確保する。

【解決手段】第1の配線層絶縁膜と、第1の配線層絶縁膜に埋め込み形成されている複数の第1の銅配線8と、第1の銅配線8上及び第1の配線層絶縁膜上に形成されている層間絶縁膜(第2の低誘電率膜10)と、を有する。層間絶縁膜上に形成されている第2の配線層絶縁膜と、第2の配線層絶縁膜に埋め込み形成されている複数の第2の銅配線16と、を有する。第1、第2の配線層絶縁膜は、第1、第2の低誘電率膜(第1の低誘電率膜4、第3の低誘電率膜11)を含む。層間絶縁膜は、第1及び第2の配線層絶縁膜よりも高強度である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】異なる基板に形成された電極同士を接合する場合、合わせずれが発生しても、電極抵抗の上昇や電流リーク等の発生を、層間容量を大きくせず防止する。

【解決手段】第1基板11上の第1層間絶縁膜12に形成された第1溝13内に第1金属電極15が埋め込まれた第1基板11と、第2基板上の第2層間絶縁膜に形成された第2溝内に第2金属電極が埋め込まれた第2基板を用意し、第1層間絶縁膜12、第2層間絶縁膜、側のそれぞれに第1拡散防止層16、第2拡散防止層、を形成する工程と、第1金属電極15、第2金属電極、を対向して接合する際に、第1金属電極15、第2金属電極、のそれぞれの形成領域内の第1拡散防止層16、第2拡散防止層、のそれぞれに第1開口部17、第2開口部、を形成する工程と、第1開口部17、第2開口部、を対向させて熱処理を行い、第1金属電極15、第2金属電極、を熱膨張によって接合させる工程を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極間を埋め込む膜に吸湿性の高い膜を用いた半導体装置において、金属配線の信頼性劣化を防ぐ。

【解決手段】半導体装置50は、基板1上に形成された複数のゲート電極2と、複数のゲート電極2上を含む基板上を覆う第1の層間絶縁膜5と、第1の層間絶縁膜5上を覆う第2の層間絶縁膜6と、第1の層間絶縁膜5及び第2の層間絶縁膜6を貫通し、それぞれ基板1上の所定箇所又は複数のゲート電極2のいずれか一つに達する複数のコンタクトプラグ7と、第2の層間絶縁膜6上に形成され、コンタクトプラグ7に接続された金属配線9を含む配線形成層8とを備える。第1の層間絶縁膜5は、少なくとも一つのゲート電極2上方に第1の凹部5aを有すると共に、複数のゲート電極2及び基板1に接する下部膜3と、第1の凹部5a以外の部分において下部膜3上に配置された上部膜4とを有し、第1の凹部5a内に、第2の層間絶縁膜6が埋め込まれている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】疎水化のために配線層間絶縁膜の表面に形成する層をできるだけ薄くし、且つ、Cu配線上に支障なくキャップメタルを成膜できるようにする。

【解決手段】配線層間絶縁膜(第1の配線層間絶縁膜3)に配線形成用溝(第1層配線形成用溝21)を形成する。配線形成用溝内にCu配線(第1層配線4)を形成し、Cu配線の構成材料のうち配線形成用溝以外の箇所に形成された部分を除去する。Cu配線上及び配線層間絶縁膜上にSi−O、C−O、Si−CH3、Si−H、Si−C及びC−Hのうちの少なくとも何れか1つの結合を含む絶縁膜層(第1の有機ポリマー層6)を形成する。Cu配線上の絶縁膜層を選択的に除去し、Cu配線上にキャップメタル(第1のキャップメタル5)を選択的に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、埋込導体構造の密着性とCu拡散防止能を両立する。

【解決手段】 半導体基板上に設けた絶縁膜に設けた埋込導体用の凹部内に埋め込まれたCuまたはCuを最大成分とする合金からなるCu系埋込導体層と、前記凹部に露出する前記絶縁膜との間にCoを最大成分とするとともに、少なくともMn、O及びCを含むCoMn系合金層を設ける。

(もっと読む)

成膜方法

【課題】 キャップ膜、もしくはバリア膜として使用することが可能な膜を、形成するか形成しないかを選択することが可能となる成膜方法を提供すること。

【解決手段】 銅を使用している配線と絶縁膜とが表面に露出している基板に対してマンガン含有膜を成膜する成膜方法であって、銅を使用している配線上に、マンガン化合物を用いたCVD法を用いてマンガン含有膜を形成する工程(ステップ2)を備える。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 低誘電率で且つCFx、SiF4等のガスの発生がなく安定な半導体装置の層間絶縁膜とそれを備えた配線構造を提供する。

【解決手段】 下地層上に形成された絶縁膜を備えた層間絶縁膜において、前記層間絶縁膜は、実効誘電率が3以下である。配線構造は、層間絶縁膜と、層間絶縁膜に形成されたコンタクトホールと、前記コンタクトホール内に充填された金属とを備え、前記絶縁膜は、前記下地層上に形成され、表面が窒化されたフルオロカーボン膜を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】実用上十分なエレクトロマイグレーション耐性及び動作速度を有する半導体装置を得られるようにする。

【解決手段】半導体基板1の上に第1の絶縁膜2を形成し、第1の絶縁膜2に配線溝3を形成し、配線溝3の内部に金属膜5を埋め込んで第1の配線6を形成し、第1の絶縁膜2及び第1の配線6の上に保護膜7を形成し、第1の配線6と保護膜7との界面に反応層8を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】実効誘電率を低減させて、高速かつ消費電力の低い半導体装置を実現する。

【解決手段】本発明の半導体装置は、基板と、基板上に形成された層間絶縁膜51、52と、層間絶縁膜51、52に埋め込まれたCu配線1と、Cu配線1上に形成された第二のバリア絶縁膜4と、を有する。第二のバリア絶縁膜4は、炭素二重結合、アモルファスカーボン構造及び窒素を含む有機シリカ膜である。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン・ゲート電極作成のためのエッチング処理時に、クランプによって覆われていたポリサイド層上の層間絶縁膜の膜剥がれが起こりにくい半導体装置の製造方法を提供する。

【解決手段】半導体基板110上に、ポリシリコン膜220及びタングステン・シリサイド膜210をこの順に積層してポリサイド・ゲート電極230を形成する。ポリサイド・ゲート電極230を含む半導体基板110上に、B濃度が高濃度の下層BPSG膜140を第1の成膜速度v1で形成する。下層BPSG膜140の上に、B濃度が下層BPSG膜140より低い低濃度の上層BPSG膜120を第2の成膜速度v2で形成する。第2の成膜速度は前記第1の成膜速度未満である。

(もっと読む)

半導体装置の製造方法

【課題】複数の絶縁膜を有する積層膜を形成する場合のスループットの向上等を実現し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に、少なくともトリメチルシリルアセチレンを原料ガスとして用いて、組成の異なる複数の絶縁膜34、36、38、40を有する積層膜及び組成の異なる複数の絶縁膜56,58,60,62を有する積層膜64を、同一の反応室内において大気開放することなく連続的に形成する工程を有している。

(もっと読む)

酸化マンガン膜の形成方法、半導体装置の製造方法および半導体装置

【課題】 Cuとの密着性を良好とすることが可能な酸化マンガン膜の形成方法を提供すること。

【解決手段】 酸化物102上にマンガンを含むガスを供給し、酸化物102上に酸化マンガン膜103を形成する酸化マンガン膜103の形成方法であって、酸化マンガン膜103を形成する際の成膜温度を、100℃以上400℃未満とする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

半導体装置の製造方法

【課題】多孔質絶縁膜を疎水化する半導体装置の製造方法を提供する。

【解決手段】基板3に多孔質絶縁膜2を形成する工程(S101)と、多孔質絶縁膜2が形成された基板3をチャンバー1内に配置する工程(S102)と、基板3が配置されたチャンバー1内にシロキサンを投入するとともに基板3を第一の温度に昇温する工程(S103)と、投入されたシロキサンが付着した基板3を第一の温度よりも高い第二の温度に昇温する工程(S104)と、を含む。S103では、チャンバー1内の圧力を1kPa以下とする。また、第一の温度は、チャンバー1内の圧力がシロキサンの飽和蒸気圧となる温度以上であり、かつ、多孔質絶縁膜2とシロキサンとが重合反応を開始する温度以下である。

(もっと読む)

半導体装置の製造方法

【課題】 CVD−MnOxをバリア膜に用いても歩留りの低下を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】 N層以上の銅、又は銅合金配線4、8を有し、これらN層の銅、又は銅合金配線4、8のバリア膜としてCVD−MnOx膜を使用する半導体装置の製造方法であって、第1層乃至第N−1層のCVD−MnOx膜3は、セルフリミットがかかる前に成膜を完了させ、第N層のCVD−MnOx膜7は、セルフリミットがかかるように成膜する。

(もっと読む)

41 - 60 / 260

[ Back to top ]