Fターム[5F033SS03]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 原料ガス (1,958) | 有機シラン系ガス (1,382)

Fターム[5F033SS03]の下位に属するFターム

TEOS (1,124)

Fターム[5F033SS03]に分類される特許

101 - 120 / 258

薄いバリア層を用いた多孔性誘電体への溶媒および溶液の侵入の阻止および低減

基板を処理するための方法および装置が提供される。基板上に多孔性誘電体層が形成される。いくつかの実施形態では、誘電体を緻密な誘電体層によって覆うことができる。誘電体層がパターン形成され、基板の上に緻密な誘電体層が共形的に堆積される。緻密な共形の誘電体層は、多孔性誘電体層の孔を、孔に浸入する可能性がある化学種と接触しないように密封する。緻密な共形の封孔誘電体層の、フィールド領域とパターン開口部の底部とを覆う部分が、指向性の選択的なエッチングによって除去される。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Low−k膜の機械的強度を向上させることができる半導体装置の製造方法、およびそれにより得られる半導体装置を提供する。

【解決手段】半導体基板SB上に、SiOCを含有する骨格構造部と、炭化水素化合物を含有する空孔形成材料部とを有するSiOC膜である層間絶縁膜3が形成される。層間絶縁膜3に200nm以上260nm以下の波長を有する光が照射される。

(もっと読む)

ポロゲン、ポロゲン化前駆体、および低誘電定数を有する多孔性有機シリカガラスフィルムを得るためにそれらを用いる方法

【課題】特性の向上した多孔性シリカガラスフィルムを提供する化学気相蒸着方法を提供する。

【解決手段】真空チャンバーに、オルガノシランおよびオルガノシロキサンからなる群から選択される少なくとも1つの前駆体、および前駆体とは区別されるポロゲンを含めたガス状試薬を導入すること(ここに、ポロゲンは非−分岐構造、および2と等しい、またはそれ未満の不飽和の度合いを有するC4〜C14環状炭化水素化合物である);エネルギーを真空チャンバー中のガス状試薬に適用してガス状試薬の反応を誘導し、基材上に予備的フィルムを蒸着させること(ここに、予備的フィルムはポロゲンを含有する);および不安定有機物質の実質的に全てを予備的フィルムから除去して細孔および2.6未満の誘電定数を有する多孔性フィルムを供することを含む、多孔性有機シリカガラスフィルムを製造するための化学気相蒸着方法。

(もっと読む)

コンフォーマルPECVD膜を使用するクリティカルディメンジョンシュリンクのための方法

基板中に狭いビアを形成するための方法および装置を提供する。従来型のリソグラフィによって、パターンリセスを基板中にエッチングする。パターンリセスの側壁および底部を含んでいる基板の表面の上方に薄いコンフォーマル層を形成する。コンフォーマル層の厚さは、パターンリセスの実効的な幅を縮小する。下方にある基板を暴露させるために、異方性エッチングによってパターンリセスの底からコンフォーマル層を除去する。次に、マスクとしてパターンリセスの側壁を覆っているコンフォーマル層を使用して基板をエッチングする。次に、ウェットエッチャントを使用してコンフォーマル層を除去する。  (もっと読む)

(もっと読む)

エッチングマスク形成方法、エッチング方法、および半導体デバイスの製造方法

【課題】プロセス数の低減が可能であり、プロセスの単純化が容易なエッチングマスク形成方法を提供する。

【解決手段】エッチングの対象となる対象層10上に、対象層10をエッチングするためのエッチングマスクを形成するマスク膜12を形成し、マスク膜12に転写されるべき第1のパターンを有する第1のマスク層16a,20をマスク膜12上に形成し、マスク膜12に転写されるべき第2のパターンを有する第2のマスク層22a,24を第1のマスク層上に形成し、第2のマスク層の第2のパターンを第1のマスク層に転写して、第1のパターンおよび第2のパターンを有する第3のマスク層を形成する第3のマスク層形成工程と、第3のマスク層を用いてマスク膜をエッチングして、対象層のエッチングに使用されるエッチングマスクを形成するエッチングマスク形成工程と、を含むエッチングマスク形成方法が提供される。

(もっと読む)

半導体装置の作製方法

【課題】端部の勾配が急峻であり、所望の膜厚を確保することができ、マスクパターンとの形状の差が抑えられる導電膜を、エッチングを用いて作製する。

【解決手段】膜厚1μm以上10μm以下のアルミニウムまたはアルミニウム合金を含む導電膜を、ウェットエッチングを用いて所定の膜厚となるまでエッチングした後、残りをドライエッチングでエッチングすることで、サイドエッチングを抑え、なおかつマスクの膜厚が減少するのを抑える。サイドエッチングを抑え、なおかつマスクの膜厚が減少するのを抑えることで、膜厚1μm以上10μm以下といった厚膜のアルミニウムまたはアルミニウム合金を含む導電膜であっても、端部の勾配が急峻であり、所望の膜厚を確保することができ、マスクパターンとの形状の差が抑えられるようにエッチングすることが可能となる。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】十分に低いリーク電流、高い電気的ストレス耐性、及び高いエッチング耐性を有する絶縁膜を半導体基板の表面に堆積する、半導体装置の製造方法、並びに、その絶縁膜を備える半導体装置を提供する。

【解決手段】シリコンソースと酸化剤とを交互に供給して半導体基板の表面にシリコン酸化膜を堆積する、半導体装置の製造方法であって、前記シリコンソースの供給を、前記半導体基板へ前記シリコンソースの分子が吸着飽和することなく吸着量が増加する供給条件で行い、前記酸化剤の供給を、前記半導体基板に吸着された前記シリコンソースの分子中に不純物が残存する供給条件で行う。

(もっと読む)

半導体装置、半導体装置の作製方法

【課題】支持基板上に、単結晶半導体層を多層構造とした、多層集積回路を形成する場合の、工程数の簡略化を図る。また同集積化の向上を図る。

【解決手段】複数の半導体素子が絶縁層を介して積層される半導体装置において、絶縁層を介して半導体素子を構成する半導体層が積層された構造を有し、一の半導体層が配線とコンタクトする領域が、絶縁層を介して設けられる他の半導体層と重畳するように配置された構成とする。当該コンタクトする領域は、該一の半導体層に設けられる一導電型不純物領域から延在するシリサイド層によって形成される。すなわち、一の半導体素子と配線とのコンタクト領域をシリサイドで形成すると共に上層半導体素子と重畳する位置に配置させ、該半導体素子を構成する一導電型不純物領域と配線とのコンタクト領域との間をシリサイドで連結する構成を有する。

(もっと読む)

成膜方法

【課題】低温領域で成膜しても、その膜ストレスを向上させることが可能な成膜方法を提供する。

【解決手段】被処理体Wの表面に所定の特性を有するシリコン窒化膜を形成する成膜方法において、シラン系ガスと窒化ガスとを用いて第1の温度で前記被処理体の表面にシリコン窒化膜を形成するシリコン窒化膜形成工程S1と、前記被処理体を前記第1の温度よりも高い第2の温度で窒化ガスの雰囲気下にてアニールして前記シリコン窒化膜を改質する改質工程S3とを行う。これにより、低温領域で成膜しても、その膜ストレスを向上させることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体の製造工程において、層間絶縁膜へのダメージを極力抑えることが可能な配線の還元処理方法の開発。

【解決手段】本発明は、基板上に導電部材および絶縁膜を有する半導体装置の製造方法であって、該方法は、基板上に導電部材を形成する工程、該導電部材上に絶縁膜を形成する工程、該導電部材上の絶縁膜を除去する工程、該導電部材上の酸化された領域を還元するために有機シランガスおよび水素ガスをブローする工程からなり、ここで該導電部材上の酸化された領域は、該絶縁膜が除去されたときに形成されることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】酸化シリコン膜のエッチングに対するエッチング耐性を有する応力膜を形成することで、応力膜の上記エッチング時の膜減りを低減することを可能にする。

【解決手段】半導体基板11上にゲート電極形成溝23が形成されたサイドウォール絶縁膜21と、ゲート電極形成溝23内の半導体基板11上にゲート絶縁膜24を介して形成されたゲート電極25と、ゲート電極25の側壁にサイドウォール絶縁膜24を介して半導体基板11上に形成されていて応力を有する第1応力膜51と、第1応力膜51の外側の半導体基板11上に形成されていて第1応力膜51と同種の応力を有する第2応力膜52とを有し、第1応力膜51および第2応力膜52は酸化シリコン膜をエッチングするときのエッチング種に対するエッチング耐性を有し、第1応力膜51は第2応力膜52よりも前記エッチング種に対するエッチング耐性が強いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ビアファースト方法を用いるデュアルダマシン配線の形成において、レジストポイズニングを抑制する。

【解決手段】半導体装置の製造方法は、基板101上に層間絶縁膜108を形成する工程(a)と、層間絶縁膜108にビアホール109を形成する工程(b)と、ビアホール109内にダミープラグ111を形成する工程(c)と、工程(c)の後、層間絶縁膜108上に第1のバリア絶縁膜120を形成し、更にその上に反射防止膜105を形成するする工程(d)と、第1のバリア絶縁膜120上に、配線溝形成用開口114を有するレジストマスク113を形成する工程(e)と、レジストマスク113をマスクとして層間絶縁膜108、第1のバリア絶縁膜120及びダミープラグ111のそれぞれ一部を除去することにより、ダミープラグ111の残存部分に接続する配線溝を形成する工程(f)とを有する。

(もっと読む)

ケイ素含有膜およびその形成方法

【課題】高集積化および多層化が望まれている半導体素子などにおいて好適に用いることができ、機械的強度に優れ、低比誘電率でかつ吸湿性が低く、加工耐性が高いケイ素含有膜およびその形成方法を提供する。

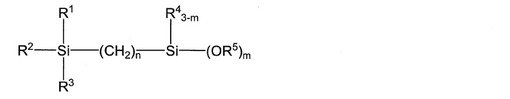

【解決手段】ケイ素含有膜の形成方法は、下記一般式(1)で表される有機シラン化合物と空孔形成剤とを用いて、化学気相成長法により堆積膜を形成する工程と、前記堆積膜を硬化させる工程と、を含む。

【化1】

・・・・・(1)

(式中、R1〜R4は、同一または異なり、水素原子、炭素数1〜4のアルキル基、ビニル基、またはフェニル基を示し、R5は炭素数1〜4のアルキル基、アセチル基、またはフェニル基を示し、nは1〜3の整数を示し、mは1〜2の整数を示す。)

(もっと読む)

半導体装置の製造方法

【目的】パターン密度の違いによるエッチング差を抑制する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上にポロジェン材料を含む絶縁膜を形成する工程(S104)と、前記絶縁膜に含まれる前記ポロジェン材料の一部を除去する工程(S106)と、前記ポロジェン材料の一部が除去された前記絶縁膜に前記絶縁膜の底部を残すように開口部を形成する工程(S112)と、前記絶縁膜に含まれる前記ポロジェン材料の残部を除去する工程(S114)と、前記開口部の前記底部をエッチングする工程(S116)と、を備えたことを特徴とする。

(もっと読む)

ケイ素含有膜形成用組成物、ケイ素含有膜の形成方法、およびケイ素含有膜

【課題】高集積化および多層化が望まれている半導体素子などにおいて好適に用いることができ、機械的強度に優れ、低比誘電率でかつ吸湿性が低く、加工耐性が高い膜を形成することができるケイ素含有膜形成用組成物、上記組成物を用いるケイ素含有膜の形成方法、および上記形成方法によって得られるケイ素含有膜を提供する。

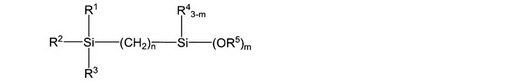

【解決手段】ケイ素含有膜形成用組成物は、下記一般式(1)で表される有機シラン化合物と、空孔形成剤とを含む。

【化1】

・・・・・(1)

(式中、R1〜R4は、同一または異なり、水素原子、炭素数1〜4のアルキル基、ビニル基、またはフェニル基を示し、R5は炭素数1〜4のアルキル基、アセチル基、またはフェニル基を示し、nは1〜3の整数を示し、mは1〜2の整数を示す。)

(もっと読む)

微細構造におけるエアギャップの製造方法

【課題】化学エッチング液の膜を通じた拡散による犠牲膜材料の分解により、微細構造のエアギャップを形成する。

【解決手段】微細構造に少なくとも一つのエアギャップ35を製造する方法として、(a)犠牲材料で充填された少なくとも一つのギャップ35を備えた微細構造を提供し、前記ギャップ35は非透過性膜であるが犠牲材料を分解する性質を有する化学エッチング液の作用により透過性膜へと転換し得る膜33によりその表面の少なくとも一部分を覆われ画定される工程と、(b)膜33を透過性へと転換させ犠牲材料を分解するために前記化学エッチング液と微細構造とを接触させる工程と、(c)微細構造から化学エッチング液を除去し、前記化学エッチング液はフッ化水素酸及び/又はフッ化アンモニウムを含む流体である工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、ダマシン構造を有する銅多層配線を構成するトレンチのCMP工程後に露出した低誘電率膜表面のダメージを回避して配線信頼性を確保するとともに、直列抵抗の増大を抑制する。

【解決手段】 ポーラス絶縁膜に設けた凹部に埋め込まれた第1の金属膜の少なくとも頂面を、前記ポーラス絶縁膜の頂面と整合する高さまでZr及びBを含む第2の金属膜で覆う。

(もっと読む)

半導体装置およびその製造方法

【課題】十分なEM耐性および配線間TDDB寿命を確保しつつ、層間絶縁膜の低誘電率化を行っても絶縁膜ライナー膜厚を薄くすることができ、配線間の実効比誘電率Keffを低減した高速で高信頼性な配線を得ることができる。

【解決手段】第1の絶縁膜1には配線溝M1が形成されており、配線溝M1内にはCu膜2bが設けられている。Cu膜2bの上にはSiCN膜3a、SiCO膜3bおよびSiOC膜4aが順に設けられており、SiOC膜4aはSiCN膜3aおよびSiCO膜3bよりも低誘電率な絶縁膜である。SiCO膜3bの上面には、高密度化処理が施されて高密度膜3cが形成されている。

(もっと読む)

半導体デバイス及びその製造方法

【課題】半導体デバイスにおける層間絶縁膜間の密着性を良好にし、デバイスの信頼性を向上する。

【解決手段】異なる二つの絶縁膜が上下に接する構造を有する半導体デバイスにおいて、上層膜51について膜強度M1[GPa]、膜密度D1[g/cm3]、膜応力S1[GPa]、膜厚T1[nm]、下層膜52について膜強度M2[GPa]、膜密度D2[g/cm3]、膜応力S2[GPa]、膜厚T2[nm]で示されるとき、

|S2×T2/10−S1×T1/10|−(M1+M2)×(D1+D2)>280・・・・(101)

を満たし、上下層間のC/Si比が1.7以下かつO/Si比が0.8以上とする。

(もっと読む)

優勢エッチング抵抗性を具備する低K誘電バリアを得る方法

【課題】低い誘電率、向上したエッチング抵抗性、優れたバリア特性を設けた誘電バリアを形成する方法を提供する。

【解決手段】半導体基板を処理する方法を提供し、この方法は、ケイ素−炭素結合および炭素−炭素結合を備える前駆物質を処理チャンバへ流すステップと、半導体基板上に炭素−炭素結合を有する誘電バリア膜を形成するために、処理チャンバ内において前駆物質の低密度プラズマを生成するステップであって、この前駆物質中の炭素−炭素結合の少なくとも一部は低密度プラズマ中に保存されかつ誘電膜内に組み込まれるステップと、を備える。

(もっと読む)

101 - 120 / 258

[ Back to top ]