Fターム[5F033SS03]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | 原料ガス (1,958) | 有機シラン系ガス (1,382)

Fターム[5F033SS03]の下位に属するFターム

TEOS (1,124)

Fターム[5F033SS03]に分類される特許

41 - 60 / 258

半導体装置の製造方法および半導体装置

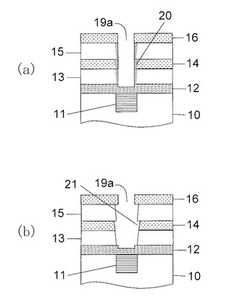

【課題】 デュアルダマシン法を用いて銅の埋め込み配線および接続プラグを形成するとき、接続プラグ中のボイド発生を防止する。

【解決手段】 Low−k膜13、15、ELK膜14、TEOS膜16からなる層間絶縁膜にプラグとなる接続孔19aを形成した後、酸素プラズマ処理を行って変質層20を形成し、この層を薬液処理により選択的に除去すると、ELK膜14が多孔質であることに起因してその側壁21にLow−k膜13、15などより大きい角度のテーパーが形成される。次に配線埋め込み用の溝の底面がELK膜14中にくるように形成して、プラグ開口の入口が広がる形状にした後、銅膜を埋め込む。

(もっと読む)

成膜方法及び半導体装置

【課題】層間絶縁膜と配線金属との間に形成されるバリア膜について、配線金属を構成する元素や層間絶縁膜を構成する元素に対して高いバリア性を提供する。

【解決手段】処理容器内に基板を載置する載置台51と周方向に沿って多数のスリットが形成された平面アンテナ部材82とを対向して設け、導波管からのマイクロ波を前記平面アンテナ部材を介して処理容器内に供給する。一方処理容器の上部からArガスなどのプラズマ発生用のガスを供給すると共にこのガスの供給口とは異なる位置から原料ガスである例えばトリメチルシランガスと窒素ガスとを供給することでこれらガスをプラズマ化し、更に載置台51の上面の単位面積当たりに供給されるバイアス用の高周波電力が0.048W/cm2以下となるようにバイアス用の高周波電力を印加する。

(もっと読む)

段階化キャップ層を有するパターニング可能low−k誘電体配線構造、エアギャップ包含配線構造、および製作方法

【課題】パターニングされた段階化キャップ層の表面上に配される少なくとも1つのパターニングされ且つ硬化されたlow−k物質を含む配線構造を提供する。

【解決手段】少なくとも1つの硬化され且つパターニングされたlow−k物質およびパターニングされた段階化キャップ層は、その中に組み込まれる導電的充填領域を各々有する。パターニングされ且つ硬化されたlow−k物質は、1つ以上の酸感受性イメージング可能基を有する機能性ポリマー、コポリマー、あるいは少なくとも2種の任意の組み合わせのポリマー類もしくはコポリマー類またはその両方を含むブレンドの硬化生成物であり、段階化キャップ層はバリア領域として機能する下部領域および恒久的な反射防止膜の反射防止特性を有する上部領域を含む。

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜の膜強度を十分に確保する。

【解決手段】第1の配線層絶縁膜と、第1の配線層絶縁膜に埋め込み形成されている複数の第1の銅配線8と、第1の銅配線8上及び第1の配線層絶縁膜上に形成されている層間絶縁膜(第2の低誘電率膜10)と、を有する。層間絶縁膜上に形成されている第2の配線層絶縁膜と、第2の配線層絶縁膜に埋め込み形成されている複数の第2の銅配線16と、を有する。第1、第2の配線層絶縁膜は、第1、第2の低誘電率膜(第1の低誘電率膜4、第3の低誘電率膜11)を含む。層間絶縁膜は、第1及び第2の配線層絶縁膜よりも高強度である。

(もっと読む)

半導体装置の製造方法。

【課題】 金属膜やHigh−k膜の膜質の劣化を抑制できる半導体装置の製造方法を提供すること。

【解決手段】 第1の薄膜2上に、第1の薄膜2とは異なる第2の薄膜3を形成し、第2の薄膜3上に、第2の薄膜3とは異なる膜からなる犠牲膜5を形成し、犠牲膜5をエッチングにより所望の間隔を持つパターンに加工し、犠牲膜パターンを形成し、シリコン含有プリカーサー、酸素含有ガスを基板上に間欠的に供給して、犠牲膜パターンにシリコン酸化膜6を被覆し、シリコン酸化膜6をエッチングにより犠牲膜5の側壁上に側壁スペーサー6aを形成し、犠牲膜5を除去し、側壁スペーサー6aをマスクとして用いて第1の薄膜2および第2の薄膜3を加工する。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造等を含む半導体装置の製造工程を簡略化する。

【解決手段】半導体装置の製造方法は、基板101上に絶縁膜102を形成する工程(a)と、絶縁膜102上にハードマスク膜103を形成する工程(b)と、ハードマスク膜103上に第1のモールド108を接触させて、陽極酸化により第1の酸化領域110を形成する工程(c)と、ハードマスク膜103上に第2のモールド111を接触させて、陽極酸化により第2の酸化領域112を形成する工程(d)と、第1の酸化領域110及び第2の酸化領域112を除去してハードマスク103aを形成する工程(e)と、ハードマスク103aをマスクとするエッチングにより、絶縁膜103中に接続孔104及び配線溝105を形成する工程(f)とを備える。第1の酸化領域110と第2の酸化領域112とは面積及び深さが異なる。

(もっと読む)

ジアルキルアミノ基を有する気相成長用シリコン原料及び当該材料を用いたシリコン含有薄膜の製造方法

【課題】 本発明の課題は、取り扱いが容易で、且つ酸化的熱分解が起こり易いジアルキルアミノ基を有する気相成長シリコン原料を提供することにある。

【解決手段】 本発明の課題は、ジアルキルアミノ基を有する気相成長用シリコン原料によって解決される。

(もっと読む)

ポロゲン、ポロゲン化された前駆体及び低誘電率をもつ多孔質有機シリカガラス膜を得るためにそれらを使用する方法

【課題】低い誘電率及び改良された機械的性質、熱的安定性及び化学的耐性を有する多孔質有機シリカガラス膜を提供する。

【解決手段】式SivOwCxHyFz(ここで、v+w+x+y+z=100%、vは10〜35原子%、wは10〜65原子%、xは5〜30原子%、yは10〜50原子%、及びzは0〜15原子%)で表わされる多孔質有機シリカガラス膜を製造する。オルガノシラン及びオルガノシロキサンからなる群より選ばれる前駆体並びにポロゲンを含むガス状試薬を真空チャンバに導入し、ガス状試薬にエネルギーを加え、ガス状試薬の反応を生じさせて基体上に予備的な膜を堆積させる。その予備的な膜は細孔を持ち、誘電率が2.6未満である多孔質膜を得るために、実質的にすべてのポロゲンを除去される。

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 低誘電率で且つCFx、SiF4等のガスの発生がなく安定な半導体装置の層間絶縁膜とそれを備えた配線構造を提供する。

【解決手段】 下地層上に形成された絶縁膜を備えた層間絶縁膜において、前記層間絶縁膜は、実効誘電率が3以下である。配線構造は、層間絶縁膜と、層間絶縁膜に形成されたコンタクトホールと、前記コンタクトホール内に充填された金属とを備え、前記絶縁膜は、前記下地層上に形成され、表面が窒化されたフルオロカーボン膜を備えている。

(もっと読む)

半導体装置の製造方法

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 絶縁膜に設けた凹部の側壁にシール絶縁膜を形成し、シール絶縁膜の内側に順にシール絶縁膜との密着性が優れている第1の導電性バリア層、Cu拡散阻止能力が高い第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設ける。

(もっと読む)

高周波デバイスおよびその製造方法

【課題】基板に開口を有する高周波デバイスを精度よく位置合わせすることが可能な高周波デバイスおよびその製造方法を提供する。

【解決手段】基板11に貫通電極下部14D、開口16および突起17を設ける。基板11の表面に、絶縁膜12、誘電体層13、絶縁膜12と誘電体層13とを貫通する貫通電極上部14Aおよびスイッチング素子15を形成する。基板11には、開口16および突起17を同時に形成したのち、基板11を貫通すると共に貫通電極上部14Aと接する貫通電極下部14Dを形成する。開口16および突起17を同時に形成することにより、インターポーザ基板などの実装基板に精度よく位置合わせすることが可能な高周波デバイス1を、工程数を増やすことなく得ることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】実用上十分なエレクトロマイグレーション耐性及び動作速度を有する半導体装置を得られるようにする。

【解決手段】半導体基板1の上に第1の絶縁膜2を形成し、第1の絶縁膜2に配線溝3を形成し、配線溝3の内部に金属膜5を埋め込んで第1の配線6を形成し、第1の絶縁膜2及び第1の配線6の上に保護膜7を形成し、第1の配線6と保護膜7との界面に反応層8を形成する。

(もっと読む)

半導体装置の製造方法

【目的】キャップ成膜時に起因するlow−k膜の絶縁性劣化を低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に絶縁材料を用いたキャップ膜を形成する工程(S106)と、前記キャップ膜を形成した後に、前記キャップ膜を介して前記前記キャップ膜の下層のシリル化処理を行なう工程(S108)と、前記シリル化処理の後、エッチング法を用いて、前記キャップ膜上から前記絶縁膜内へと続く開口部を形成する工程(S114)と、前記開口部に導電性材料を堆積させる工程(S124)と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い半導体装置を実現する構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板(半導体基板1)上に、シラン化合物およびポロジェンを含む膜(有機シリコンポリマー膜2)を設ける工程と、選択的エッチングにより有機シリコンポリマー膜2に孔(配線溝3)を設けるとともに、配線溝3の内部に金属膜(バリア膜4および銅配線5)を設ける工程と、還元ガス雰囲気中で、上記ポロジェンの沸点または分解温度以上の温度で加熱しつつ、有機シリコンポリマー膜2に紫外線6を照射して、多孔質膜7を得る工程と、を含むものである。

(もっと読む)

窒素含有前駆物質を用いる誘電体バリアの堆積

【課題】現行のバリア誘電体膜に匹敵するかそれよりも低い誘電率を有する誘電体膜を得る方法を提供する。

【解決手段】集積回路基板の誘電体膜と金属相互接続との間に、炭窒化ケイ素バリア誘電体膜を形成する方法であって、誘電体膜を有する集積回路基板を提供すること、この基板をRxR’y(NR”R”’)zSiを含むバリア誘電体膜の前駆物質と接触させること(R、R’、R”及びR”’はそれぞれ個々に、水素、直鎖若しくは分岐の飽和若しくは不飽和アルキル、又は芳香族から選択され;x+y+z=4;z=1〜3であるが、R及びR’の両方が同時に水素にはならない);及び集積回路基板上でC/Si比0.8超かつN/Si比0.2超の炭窒化ケイ素バリア誘電体膜を形成することを含む方法。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線に達するコンタクトホールを確実に形成し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38を形成する工程と、第1応力膜とエッチング特性が異なる絶縁膜40を形成する工程と、第1領域2を覆う第1マスク60を用いて、第2領域内の絶縁膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の絶縁膜をサイドエッチングする工程と、第1マスクを用いて第2領域内の第1応力膜をエッチングする工程と、絶縁膜とエッチング特性が異なる第2応力膜を形成する工程と、第2領域を覆い、第1領域側の端面が絶縁膜上に位置する第2マスクを用いて、第2応力膜の一部が第1応力膜の一部及び絶縁膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

41 - 60 / 258

[ Back to top ]