Fターム[5F033SS11]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | CVD(化学的気相成長法) (4,764)

Fターム[5F033SS11]の下位に属するFターム

常圧CVD (88)

LPCVD(減圧CVD) (289)

光CVD (19)

プラズマCVD (1,949)

Fターム[5F033SS11]に分類される特許

141 - 160 / 2,419

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 2層構造のビットライン配線において、製造工程を減少することができる半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態に係る半導体記憶装置は、半導体基板を持つ。前記半導体基板上に第1及び第2のコンタクトプラグが設けられる。前記第1のコンタクトプラグに接する第1のビットラインが設けられ、前記第2のコンタクトプラグ上には第2のビットラインが設けられる。前記第1のコンタクトプラグは、前記第1のビットラインの上面と接し、かつ前記第2のビットラインと電気的に絶縁しており、前記第2のビットラインの底面の高さは、前記第1のビットラインの上面よりも高い。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置、回路基板および電子機器

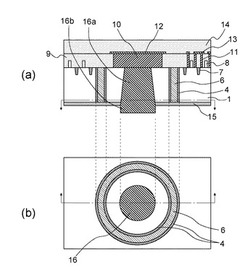

【課題】半導体基板と貫通電極との絶縁を確実とする半導体装置を提供する。

【解決手段】半導体装置10の一方の面14から他方の面16に形成された電極パッド24の裏面に到達する貫通電極13を形成した半導体装置10であって、他方の面16側には第1の絶縁膜20を介して電極パッド24が設けられ、貫通電極13を構成する貫通孔21と第1の絶縁膜20との境界面に、一方の面14側の開口よりも大きい開口を有し、貫通電極13を形成する際、他方の面16側の貫通孔21開口部内周に貫通電極13を構成する導電材料と電極パッド24との間に第2の絶縁膜23を備え、貫通孔21内壁面および第2の絶縁膜上に第3の絶縁膜22が設けられる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における配線形状を改善すること。

【解決手段】半導体装置の製造方法は、溝領域を規定する第1パターンを有する第1マスクを、サイドウォール形状の転写により、半導体装置の層間膜に設けられた金属膜上に形成する工程と、前記第1パターンに重なる少なくとも一つの開口を有する第2マスクを、平面図で見た場合に、前記2マスクが前記第1マスクに重なり、前記開口が前記溝領域に重なるように、形成し、第2パターンを形成する工程と、前記第1及び第2マスクを介して、前記層間膜をエッチングし、前記第1パターンを前記層間膜に転写させる工程と、前記第2マスクを介して前記層間膜をエッチングし、前記第2パターンを前記層間膜に転写させる工程とを具備する。前記第1パターンは、前記第2パターンとは異なる深さで前記層間膜に形成される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】耐圧確保に有利な構造を提供する。

【解決手段】実施形態の半導体記憶装置は、基板上で所定方向に平行に延伸した複数の素子分離領域と、隣接する素子分離領域に挟まれた素子領域上の第1絶縁膜と、素子領域上の所定方向に間隔を空けて形成され、第1絶縁膜の上に順に積層された電荷蓄積層、第2絶縁膜、及び制御ゲート電極をそれぞれ有する複数のワードラインと、その両側に1つずつ配置され所定方向の幅がワードラインより大きい選択トランジスタと、ワードライン及び選択トランジスタの上面を覆う層間絶縁膜と、ワードライン間に位置し上部を層間絶縁膜に覆われた第1空洞部と、選択トランジスタのワードラインとは反対側の側壁部に形成され上部が層間絶縁膜で覆われた第2空洞部を備える。実施形態の半導体記憶装置は、互いに隣接する選択トランジスタ間の基板表面に酸化膜が形成され、その下の所定方向に垂直方向の断面が凸型形状になっている。

(もっと読む)

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】樹脂基板上に設けたボトムゲート型薄膜トランジスタにおいて、製造プロセスを簡略化することにより、高品質で低コストの薄膜トランジスタとその製造方法及び画像表示装置を提供することを目的とする。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

(もっと読む)

半導体装置

【課題】絶縁耐量を改善することができる半導体装置を得る。

【解決手段】Si基板10(基板)上にゲート抵抗7(下配線)が設けられている。ゲート抵抗7を層間絶縁膜12が覆っている。層間絶縁膜12上に、互いに分離したアルミ配線5a,5b(第1及び第2の上配線)が設けられている。アルミ配線5a,5bを半絶縁性の保護膜4が覆っている。ゲート抵抗7の直上であってアルミ配線5aとアルミ配線5bとの間の領域に、保護膜4が設けられていない。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

半導体装置

【課題】容量素子を備え、電気的特性の安定化が可能な半導体装置を提供する。

【解決手段】半導体基体1上の配線層に形成されている配線と絶縁層とからなる容量素子10を備える。そして、容量素子10の形成領域内の半導体基体11上に形成されている導体パターンと、導体パターンの電位を固定するための電位固定端子28とを備える半導体装置を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

141 - 160 / 2,419

[ Back to top ]