Fターム[5F033SS11]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | CVD(化学的気相成長法) (4,764)

Fターム[5F033SS11]の下位に属するFターム

常圧CVD (88)

LPCVD(減圧CVD) (289)

光CVD (19)

プラズマCVD (1,949)

Fターム[5F033SS11]に分類される特許

2,401 - 2,419 / 2,419

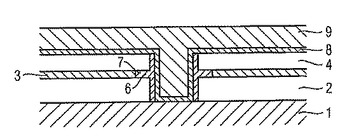

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

電子デバイス、アセンブリ、電子デバイスの製造方法

半導体基板は、共通の誘電層を有する垂直相互接続部および垂直キャパシタの両方を備えている。基板は、アセンブリを形成するために更なるデバイスと適切に組み合わせることができる。基板は、一方の面を第1のステップを含むエッチング処理で形成した後、基板の他方の面を第2のステップを含む処理で形成することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体チップ上に絶縁膜を介して外部端子と再配線とが形成される半導体装置において、従来は外部端子、若しくは再配線からのノイズの影響から電子回路を保護する為、接地電位層を設けていたが、この接地電位層の為に工程が大幅に増加し、さらに、半導体装置の厚さが厚くなってしまう可能性があった。

【解決手段】本発明では、基板上の多層配線、即ち、それぞれが層間絶縁膜を介して積層された複数の層と、それぞれの層内に形成された配線とを有する多層配線の最上位の層内において、配線が配置された領域以外の領域に、定電位が与えられるノードに電気的に接続するメタル部材が形成される。これにより、工程を大幅に増加することなく、かつ、半導体装置の厚さを厚くすることなく、電子回路がノイズの影響を受けてしまう可能性を低減することができる。

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

配線構造及びその形成方法

【課題】 Cuを含有する材料に代表されるような層間絶縁膜に対する易拡散性の材料を用いて配線を構成した場合に、前記易拡散性の材料の層間絶縁膜への拡散や材料の剥離を確実に防止するとともに、層間容量を低減させ、しかも高い耐酸化性を保持する。

【解決手段】 Cu配線に対応した保護膜として、当該Cuの拡散防止及びビア孔23形成時のエッチングストッパーとしての機能を有し、しかも低誘電率を示す構造の保護膜16を提案する。この保護膜16は、水素化シリコンカーバイド膜(SiC:H膜)21上にシリコン窒化膜(SiN膜)22が積層されてなる2層構成のものである。

(もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

配線構造の形成方法

【課題】 絶縁膜及びその上のARL膜に埋め込まれた配線同士の間における短絡を防止する。

【解決手段】 基板100上に形成されたFSG膜109及びARL膜110に複数の配線用溝111を形成した後、各配線用溝111が完全に埋まるようにARL膜110の上にバリアメタル膜(窒化タンタル膜112)及び配線用導電膜(銅膜113及び114)を順次堆積する。その後、各配線用溝111の外側の銅膜113及び114を研磨により除去した後、各配線用溝111の外側の窒化タンタル膜112を研磨により除去する。その後、研磨時に基板100に付着した異物を除去した後、ARL膜110の表面を研磨する。

(もっと読む)

配線構造の形成方法

【課題】 絶縁膜及びその上のARL膜に埋め込まれた配線同士の間における短絡を防止する。

【解決手段】 基板100上に形成されたFSG膜109及びARL膜110に複数の配線用溝111を形成した後、各配線用溝111が完全に埋まるようにARL膜110の上にバリアメタル膜(窒化タンタル膜112)及び配線用導電膜(銅膜113及び114)を順次堆積する。その後、各配線用溝111の外側の銅膜113及び114を研磨により除去した後、各配線用溝111の外側の窒化タンタル膜112を研磨により除去する。その後、研磨時に基板100に付着した異物を除去した後、銅膜113及び114の研磨工程と同じ種類の研磨剤を用いてARL膜110の表面を研磨する。

(もっと読む)

配線構造の形成方法

【課題】 絶縁膜及びその上のARL膜に埋め込まれた配線同士の間における短絡を防止する。

【解決手段】 基板100上に形成されたFSG膜109及びARL膜110に複数の配線用溝111を形成した後、各配線用溝111が完全に埋まるようにARL膜110上にバリアメタル膜(窒化タンタル膜112)及び配線用導電膜(銅膜113及び114)を順次堆積する。その後、各配線用溝111の外側の銅膜113及び114を研磨により除去した後、各配線用溝111の外側の窒化タンタル膜112を研磨により除去する。その後、研磨時に研磨パッド及び基板100に付着した異物を同時に除去した後、ARL膜110の表面を研磨する。

(もっと読む)

配線構造の形成方法

【課題】 絶縁膜に埋め込まれた配線同士の間における短絡を防止する。

【解決手段】 基板100上に形成されたFSG膜109に複数の配線用溝110を形成した後、各配線用溝110が完全に埋まるようにFSG膜109の上にバリアメタル膜(窒化タンタル膜111)及び配線用導電膜(銅膜112及び113)を順次堆積する。その後、各配線用溝110の外側の銅膜112及び113を研磨により除去した後、各配線用溝110の外側の窒化タンタル膜111を研磨により除去する。その後、研磨時に基板100に付着した異物を除去した後、FSG膜109の表面を研磨する。

(もっと読む)

配線構造及びその形成方法

【課題】 配線遅延を抑止し配線の微細化及び多層配線化を可能とする配線構造、及び当該配線構造の材料に固有の諸問題、例えば一方の材料の他方の材料への溶出等の不都合を解決して、信頼性の高い配線構造を実現する。

【解決手段】 Cu配線101と電気的に接続されるWプラグ102を形成するに際して、

半導体集積回路装置の製造方法

【課題】 アルミニウムを主成分とする導体膜パターンを有する半導体集積回路装置の信頼性を向上させる。

【解決手段】 アルミニウムを主成分とする導体膜16dを有する第1層配線L1をドライエッチング法によってパターニングした後、その加工側壁の側壁保護膜18およびエッチングマスクとして使用したフォトレジストパターン17aをプラズマアッシング処理によって除去する。続いて、絶縁膜15bおよび第1層配線L1の表面に付着した塩素成分を、酸素ガスとメタノールガスとの混合ガスを用いたプラズマアッシング処理によって除去する。この際、フォトレジストパターン17a等のアッシング除去処理時は、ウエハの主面温度が相対的に低くなるようにし、塩素成分の除去処理時は、ウエハの主面温度が相対的に高くなるようにする。また、それらのプラズマアッシング処理を別々の処理室で行う。

(もっと読む)

配線構造およびその製造方法

【課題】感光性絶縁膜を用いたダマシン配線法により、微細で信頼性の高い多層配線構造を形成する。

【解決手段】感光性ポリシラザンを主成分とした感光性絶縁膜で第1ビアホール6を有するビアホール用絶縁膜7を形成し、全面にスピン塗布法で第2の感光性絶縁膜8を形成する。そして、フォトリソグラフィ法による露光/現像のみで上記第1ビアホール6の上部に配線溝9あるいは第2ビアホール10を形成する。そして、この配線溝9および第2ビアホール10に導電体材料を埋め込んでデュアルダマシン配線を形成する。ここで、感光性絶縁膜の下層に反射防止機能を有しそのまま層間絶縁膜として使用できる絶縁膜を形成する。

(もっと読む)

配線基板の製造方法、半導体装置及びめっき装置

【課題】 導体層の研磨中に導体層の剥がれを防止できる配線基板の製造方法を提供することを目的とする。

【解決手段】 基板10の一方の面10aに少なくとも孔10bを形成する工程と、基板10の一方の面10a上、他方の面10e上及び側面10f上と、孔10bの内面上とに、めっき給電層14を形成する工程と、電解めっきにより、めっき給電層14を介して、基板10の一方の面10a上、他方の面10e上及び側面10f上に形成され、かつ孔10bを埋め込む金属層18を形成する工程と、金属層18を研磨することにより、孔10bに金属層18が埋め込まれた金属層のパターン17a,17bを形成する工程とを有する。

(もっと読む)

低誘電率層間絶縁膜の形成方法

【課題】 半導体装置の層間絶縁膜などとして有用な低誘電率の膜を形成する方法と、この方法により形成される膜を提供すること。

【解決手段】 基材上に膜を成長させるのに十分な化学気相成長条件下で、シリルエーテル、シリルエーテルオリゴマー又は1以上の反応性基を有する有機ケイ素化合物を含む、有機ケイ素前駆物質を反応させて、約3.5以下の誘電率を有する層間絶縁膜を形成する。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

配線構造の製造方法

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造の製造方法を提供する。

【解決手段】 配線構造の製造方法が、半導体素子201の上にWプラグ203(下層配線)が形成された基板上に、対電子線感光性を有する材料を含む第二層間絶縁膜204(絶縁膜)を形成する工程と、第二層間絶縁膜204に電子線を照射して、第二層間絶縁膜204を露光する工程と、第二層間絶縁膜204を現像して未露光部を除去し、配線溝および/またはビアホールおよび/またはコンタクトホールを形成する工程とを有する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

多層配線構造

【課題】 上層配線の線幅面積を減少させて、上下配線間の相互干渉による不具合を低減する。

【解決手段】 半導体基板1上に形成された第1の配線7を覆うTEOS膜から成る第1の層間絶縁膜8と、該第1の層間絶縁膜8を隔てて前記第1の配線7にコンタクトする第2の配線9と、該第2の配線9を覆うTEOS膜から成る第2の層間絶縁膜10と、該第2の層間絶縁膜10を隔てて前記第2の配線9にコンタクトする第3の配線11と、該第3の配線11を覆うシリコン窒化膜13とポリイミド系絶縁膜14から成るパッシベーション膜12とを具備し、前記第3の配線11には相互干渉を起こし易い映像信号に用いられているクロマ系信号や同期信号やシリアルコントロール信号等が流れていることを特徴とするものである。

(もっと読む)

2,401 - 2,419 / 2,419

[ Back to top ]