Fターム[5F033WW02]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 長さ、寸法 (1,572) | 厚さ (759)

Fターム[5F033WW02]に分類される特許

81 - 100 / 759

配線構造体、半導体素子、配線基板、表示用パネル及び表示装置

【課題】 酸化物電極との良好な接続を行うことや、絶縁膜等との界面で生じる相互拡散を抑制することができ、かつ製造工程の低コスト化を図ることができる配線構造体、それを用いた半導体素子、配線基板、表示用パネル及び表示装置を提供する。

【解決手段】 アルミニウム層、銅層及び銅合金層からなる群より選択される少なくとも1つの層と、アルミニウム合金層とを含む2層以上の積層体であり、該アルミニウム合金層が表層に配置されている配線構造体である。これにより、液晶表示装置等において、酸化物電極と配線との接続部で酸化膜が形成されず、良好な接続を行うことができる。

(もっと読む)

垂直型トランジスタと埋め込みビットラインとを有する半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタのドレイン領域と埋め込みビットラインとの間に抵抗接点(ohmic contact)を形成しつつも、その製造工程が簡単な半導体メモリ素子及びその製造方法を提供すること。

【解決手段】基板に形成されたトレンチによって上部へ突出した形のアクティブ領域と、アクティブ領域の上部に配置される第1の不純物領域と、アクティブ領域の下部に配置される第2の不純物領域と、第1の不純物領域と第2の不純物領域との間のアクティブ領域の側面に沿って配置されるゲート絶縁膜と、ゲート絶縁膜上に配置されるゲート電極膜と、そして、トレンチの下部でライナー膜によって第2の不純物領域と離隔するように配置される金属膜と、金属膜上で前記第2の不純物領域と直接接触されるように配置されるポリシリコン膜とからなる埋め込みビットラインとを備えることを特徴とする。

(もっと読む)

印刷された第1構造体を含む電気または電子構成要素を製造するための方法

【課題】精確かつシャープな輪郭を有する平坦な構造体を、既存のジェット方法を用いて製造する方法を提供する。

【解決手段】基板2を準備するステップと、第1構造体3を基板2の上にジェット方法によって印刷するステップであって、該印刷された第1構造体3が少なくとも1つの第1角部5を含む、ステップと、第2構造体をジェット方法によって、第1構造体3の第1角部5から該第1構造体3の外側にある終点まで、第2構造体4が第1構造体とコンタクトするように印刷するステップであって、該印刷は、第2構造体4とコンタクトする第1構造体3の材料が少なくとも部分的に流体状態にある間に実施される、ステップと、第1構造体3および/または第2構造体4を電気的にコンタクトさせるステップ、とを有することを特徴とする。

(もっと読む)

半導体基板上のボンディングコンタクト

【課題】殊に銅ボンディングとの両立性の点で高い信頼性を有するボンディングコンタクトを提供すること。

【解決手段】半導体基板上の、補強構造体を有するボンディングコンタクトにおいて、このボンディングコンタクトには、半導体基板上に配置される少なくとも1つの第1金属層と、この第1金属層の上方に配置される第3金属層とを有しており、第1金属層には、パターンを有する補強構造体が収容され、第3金属層は、ボンディング面を有するボンディングコンタクト層であり、さらに上記のボンディング面の下方かつ第1金属層の上方に絶縁層が配置されており、この絶縁層は、ボンディング面の縁部を越えて突き出ている。る、ボンディング個所(1)において、上記の補強構造体は、ボンディング面の上側から見た場合にこのボンディング面の下方において第1金属層内に構成されており、この補強構造体には誘電体島が含まれている。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

半導体装置の製造方法、配線用銅合金、及び半導体装置

【課題】半導体装置の歩留まりと信頼性を向上させる。

【解決手段】配線凹部に埋め込まれた部分以外のバリアメタル膜3b上のCu膜5bを化学機械研磨によって除去する。そして配線凹部内のCu膜5b上に、添加元素からなる層6bを形成する。添加元素を層6bからCu膜5b中に拡散させて、Cu表面、及びCu結晶粒の粒界及び該粒界近傍の位置においてCu結晶粒内部よりも添加元素の濃度が高い界面及びその近傍を形成するとともに、Cu膜5b中の酸素を層6bにゲッタリングさせる。その後、余剰な層6bを除去し、さらに絶縁膜上のバリアメタル膜3bを除去する。

(もっと読む)

ウェットエッチング性に優れた表示装置用配線膜

【課題】ウェットエッチング性が良好な表示装置用配線膜を提供する。

【解決手段】希土類金属元素、Zn、Mg、およびCaよりなる群から選択される少なくとも一種の元素を5原子%以上50原子%以下の範囲で含むMo合金と、純CuまたはCu合金との積層構造を有する表示装置用配線膜である。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】高い電荷移動度を有し、大面積表示装置に対して均一な電気的特性を得ることができる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】絶縁基板上に形成されたゲート電極と、前記ゲート電極上に形成されたSiNxから構成された第1ゲート絶縁膜と、前記第1ゲート絶縁膜の上に形成されたSiOxから構成された第2ゲート絶縁膜と、前記ゲート電極と重畳するように形成され、チャネル部を有する酸化物半導体層と、前記酸化物半導体層及び前記ゲート電極の上部に形成されたSiOxから構成された保護膜とを含み、前記保護膜はドレイン電極拡張部を露出するコンタクトホールを含む。ここで、前記コンタクトホールは、ドレイン電極拡張部を直接的に露出する部分の保護膜が、その上部の保護膜よりさらに狭い領域を占める形状を有する。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備える。

(もっと読む)

配線回路基板及びその製造方法

【課題】配線回路基板において、コンタクト抵抗の上昇を抑制し、熱応力による断線を防止することのできるコンタクト構造を提供する。

【解決手段】 配線回路基板は、第1配線層(5)、第2配線層(7)、及び前記第1配線層と前記第2配線層を電気的に接続するコンタクト配線(6)を有する。前記コンタクト配線は、前記第1配線層のコンタクト面を被覆する第1被覆部(6a)と、前記第2配線層のコンタクト面を被覆する第2被覆部(6c)と、前記第1被覆部と前記第2被覆部の間に延びるプラグ部(6b)を有する。前記第1被覆部、前記プラグ部、及び前記第2被覆部は、同一の導電性材料で一体的に形成された内部に界面のないコンタクト配線である。

(もっと読む)

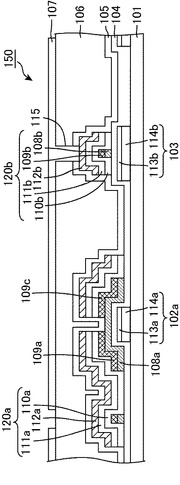

高耐圧配線、配線設計装置および方法

【課題】層間絶縁膜を厚くすることなく、放電耐圧を向上させ、デバイスの特性の安定化や性能の向上を図る。

【解決手段】高耐圧配線は、Si基板101上に形成された配線層103と、絶縁膜104と、上層配線105,106と、絶縁膜104に形成された溝107とを有する。配線層103上の絶縁膜104の厚さTは、上層配線105と106間の距離dよりも小さく、溝の幅Wは、距離dよりも小さい。絶縁膜104の厚さTは、配線層103と上層配線105,106との間に与えられる最大の電位差Vmaxよりも絶縁膜104の耐圧が大きくなるように設定され、絶縁膜104の露出量Xは、溝の幅Wと距離dとが等しいときの絶縁膜104に沿った沿面放電開始電圧をV0(V0=b×lnT+c、b,cは定数)としたとき、Vmax<aX+V0(aは定数)となるように設定される。

(もっと読む)

半導体装置の製造方法

【課題】特性のばらつきを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板1の上方に絶縁膜4を形成し、絶縁膜4に、絶縁膜4下に位置する導電領域3dを露出する開口部6を形成し、導電領域3d上及び開口部6の側面上に、Tiを含有するグルー膜17を形成する。また、グルー膜17の表面に存在する自然酸化膜を除去して、グルー膜17の表面を露出し、グルー膜17の表面を一定の条件下で酸化し、酸化が行われたグルー膜17上に、Wを含有する導電膜を形成する。なお、酸化を、グルー膜17の表面が露出した状態で開始する。

(もっと読む)

半導体装置の製造方法

【課題】余分な工程を追加することなく、コンタクト抵抗の増加を抑制する半導体装置を提供する。

【解決手段】半導体装置の製造方法では、Cu配線上の第2層間絶縁膜内に設けたコンタクトホール内に第1のTi膜、TiN膜、第2のTi膜、第1のAl膜、及び第2のAl膜をこの順に形成する。第1のTi膜を成膜する際には、コンタクトホール底面上の第1の部分と第2層間絶縁膜上の第2の部分の膜厚の比(第1の部分)/(第2の部分)を0.05以下とする。また、第2のAl膜はアルミ・リフロー法を用いて形成し、この際に第2のTi膜及び第1のAl膜をアルミニウム・チタン合金膜とする。

(もっと読む)

表示装置用Al合金膜

【課題】シリコン半導体層および/または透明導電膜との間のバリアメタル層を省略しても、AlとSiの相互拡散を抑制でき、低抵抗のオーミック特性を有する電気的接触が得られると共に、十分な耐熱性を有する表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜および/または薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、Al合金膜は、30原子%以上のMoを含有するAl−Mo合金、またはMoと、Mn、Nd、Ni、Mg、およびFeよりなるX群から選択される少なくとも1種とを含有するAl−Mo−X合金の単層から構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】吸湿性の高い絶縁膜を使用してもコンタクト又は配線の劣化を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板10上に第1の絶縁膜15を形成する工程(a)と、第1の絶縁膜15にホール24を形成する工程(b)と、ホール24の側壁上に、第1の絶縁膜15よりも水分を通しにくい第2の絶縁膜17を形成する工程(c)と、工程(c)の後、ホール24に導電体30を埋め込むことにより、プラグ19を形成する工程(d)とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数及び製造コストを削減しつつ、信頼性の高い半導体装置を製造することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1上にTiを主成分とする密着層2を形成する工程と、密着層2上にWを主成分とする導電層3を形成する工程と、導電層3上にSiONを主成分とするハードマスク層4を形成する工程と、ハードマスク層4上にレジストパターン5を形成する工程と、レジストパターン5を保護膜とするエッチング処理により導電層3の一部3aを露出させる工程と、レジストパターン5及びハードマスク層4の残部4aを保護膜とするエッチング処理により密着層2の一部2aを露出させる工程と、その後、エッチング処理により下地層1の一部1aを露出させると共に、導電層3の残部3bを露出させる工程とを有する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

耐ITOピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供すること。

【解決手段】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記Al合金膜は、Geを0.1〜5原子%含むと共に、前記Al合金膜の3倍以上のGeを含む第1層と、第1層よりもGe含有率の低いAl合金からなる第2層と、を含む積層構造を有すること。

(もっと読む)

ミクロスケール構造中でのシード層堆積

半導体装置およびその製造方法

【課題】 銅からなる柱状電極上に半田ボールが設けられた半導体装置において、半田ボール中の錫が柱状電極への拡散をより一層抑制することができるようにする。

【解決手段】 下地金属層8をメッキ電流路とした銅、ニッケルおよび半田の電解メッキをこの順で連続して行なうことにより、メッキレジスト膜25の開口部26内の上部金属層9のランド上面に柱状電極10、錫拡散抑制層11および酸化抑制層12をこの順で形成する。この結果、この半導体装置が大きな電流を扱う電源IC等であっても、酸化抑制層12を含む半田ボール14中の錫が柱状電極10に拡散するのをより一層抑制することができる。

(もっと読む)

81 - 100 / 759

[ Back to top ]