Fターム[5F033WW02]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 長さ、寸法 (1,572) | 厚さ (759)

Fターム[5F033WW02]に分類される特許

161 - 180 / 759

半導体装置およびその製造方法

【課題】平坦な表面を有する層間絶縁膜を短時間で形成することができ、また、層間絶縁膜の厚さの増大を招くことなく、金属イオンによる半導体基板の汚染に対する長期信頼性を保証することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板2と、半導体基板2上に形成された層間絶縁膜8とを備えている。そして、層間絶縁膜8は、半導体基板2側から順に、HDP膜10、ゲッタリング層12およびNSG膜11が積層された構造を有している。ゲッタリング層12は、金属イオン、とくに可動イオンを捕獲する性質を有している。

(もっと読む)

配線パターンの形成方法

【課題】インプリントモールドの凹部への感光性配線ペースト層の充填不良や、ウェットエッチング(現像)工程での配線パターンの倒壊や剥がれの発生を抑制,防止して、効率よく精度の高い配線パターンを形成する。

【解決手段】感光性配線ペースト層2を形成する工程と、凹凸パターン17を有するインプリントモールド3を感光性配線ペースト層2に押し付けて光照射する工程と、感光性配線ペースト層2の未感光部をウェットエッチングにより除去して、インプリントモールドの凹凸パターンに対応する配線パターンを形成する工程とを備えた配線パターンの形成方法において、感光性配線ペースト層2の厚みtpを下記の式(1)の範囲で規定する。

6μm+(V/S)<tp<20μm+(V/S)……(1)

ただし、

tp:感光性配線ペースト層の厚み、

S:ペースト転写領域の面積、

V:前記凹凸パターンの、前記感光性配線ペースト層と接する領域における凹部の体積

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗を維持しつつ、絶縁膜を構成するSiN膜や半導体膜におけるSiN層との密着性に優れると共に、エッチング時に良好にテーパ状にエッチングできるCu合金膜を提供する。

【解決手段】絶縁膜および/または半導体膜と直接接触する表示装置用Cu合金膜であって、該Cu合金膜は、上記SiN膜やSiN層と直接接触する第一層と、該第一層上に形成される第二層とを含み、前記第一層は、窒素を0.4原子%以上5.0原子%未満含むと共に、Ni、Al、Zn、MnおよびFeよりなる群から選択される1種以上の元素(X元素)を0.1〜0.5原子%、および/または、Ge、Hf、Nb、MoおよびWよりなる群から選択される1種以上の元素(Z元素)を0.1〜0.3原子%含み、かつ前記第一層の膜厚が2〜100nmである表示装置用Cu合金膜。

(もっと読む)

半導体装置の製造方法

【課題】 極短時間アニール処理を行う際に、基板自体の損傷を抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上にゲート電極を形成する工程と、前記半導体基板に導電性の不純物を導入する工程と、前記半導体基板及び前記ゲート電極上に保護膜を形成する工程と、前記保護膜を形成後に前記半導体基板の裏面全面を研磨する工程と、前記半導体基板の裏面全面を研磨した後に前記半導体基板の表面が1000℃以上での保持時間が0.1秒以下となるような加熱処理により前記不純物を活性化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

表示デバイスおよびその製法

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供する。

【解決手段】基板上に配置された薄膜トランジスタと、透明電極によって形成された透明導電膜、および、これら薄膜トランジスタと透明導電膜を電気的に接続するアルミニウム合金膜を有し、該アルミニウム合金膜と前記透明導電膜の界面には該アルミニウム合金の酸化皮膜が形成されており、該酸化皮膜の膜厚が1〜10nmで、該酸化皮膜中の酸素含有量が44原子%以下である表示デバイスとその製法を開示する。

(もっと読む)

MOS型半導体装置

【目的】耐放射線特性の改善と高耐圧化が図れるMOS型半導体装置を提供する。

【解決手段】LOCOS膜18上に窒化膜18を形成し、窒化膜14上にPBSG膜10を形成する。窒化膜14の屈折率を2.0〜2.1とし、膜厚を0.1μm〜0.5μmとすることで半絶縁性薄膜にする。γ線でLOCOS膜18内に発生した電子―正孔対のうち移動度が小さい正孔31を窒化膜14を通してソース電極12に逃がし、LOCOS膜18にできる正の固定電荷33の蓄積量を抑制する。このように3層構造とすることで耐放射線特性の改善と高耐圧化が図れる。

(もっと読む)

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗を維持しつつ、ガラス基板との密着性に優れると共に、エッチング時にアンダーカットを生じることなく良好にテーパ状にエッチングできるCu合金膜を提供する。

【解決手段】ガラス基板と直接接触する表示装置用Cu合金膜であって、該Cu合金膜は、該基板と直接接触する第一層と該第一層上に形成される第二層とを含み、前記第一層が、窒素を0.4原子%以上5.0原子%未満含むと共に、Ni、Al、Zn、MnおよびFeよりなる群から選択される1種以上の元素(X元素)を0.1原子%以上0.5原子%以下、および/または、Ge、Hf、Nb、MoおよびWよりなる群から選択される1種以上の元素(Z元素)を0.1原子%以上0.3原子%以下含むものであり、かつ前記第一層の膜厚が2nm以上100nm以下であることを特徴とする表示装置用Cu合金膜。

(もっと読む)

半導体装置及びその製造方法

【課題】所定の配線間距離を確保すると共に、配線間距離を確保するために形成される絶縁膜をパターニング等によって形成する際に、下層配線の損傷を防ぐ。

【解決手段】本発明に係る半導体装置は、半導体基板11と、半導体基板11上に形成された第1配線1と、半導体基板11上の第1配線1との交差部において、隙間9を介して第1配線1を跨ぐように形成された第2配線2と、交差部の第2配線2下において、少なくとも第1配線1を覆うように半導体基板11上に形成された保護膜8と、交差部の第2配線2下の保護膜8上において、保護膜8の端部よりも内側に形成され、交差部の第1配線1を覆うように島状に形成された絶縁膜3と、備えている。

(もっと読む)

小臨界次元のタングステン接点装置及び相互接続子の製法

【課題】高縦横比の特徴部のボイドなしの充填方法を提供する。

【解決手段】種々の実施例に於いて、この方法は低温化学蒸着工程によるタングステンでの特徴部の充填に関する。或る実施例に於いて、工程温度は特徴部充填の化学蒸着の間約350°C以下に維持される。この低温化学蒸着タングステン充填により、標準の化学蒸着充填と同様は薄膜抵抗を達成する一方、高縦横比の特徴部への向上された充填と下地層へとのフッ素移動への向上されたバリヤが得られる。発明は更に低抵抗を有するタングステンフィルムの堆積方法に関する。種々の実施例に於いて、この方法ではタングステンバルク層の堆積及び/或は低温化学蒸着によるバルク層の堆積の前に堆積された核形成層に低温低抵抗処理を実施し、その後高温化学蒸着を実施する。

(もっと読む)

半導体装置

【課題】小型化・高耐圧化に優れ信頼性の高いパワー半導体装置を生産効率良くかつ高い製品歩留まりで製造できる誘電体分離型の半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板内のチップ配列領域において格子状のスクライブ領域によって区画された複数のチップ領域が整列配置され、前記複数のチップ領域の各々に半導体素子が形成された誘電体分離型の半導体装置であって、少なくとも前記複数のチップ領域の上には電極配線膜が厚さ0.8μm以上2.3μm以下で形成されており、前記電極配線膜の上に前記電極配線膜を保護するパシベーション膜が厚さ0.8μm以上2.7μm以下で形成されており、前記電極配線膜の厚さに対する前記パシベーション膜の厚さの比率が1.0以上1.2以下であることを特徴とする。

(もっと読む)

固体撮像素子

【課題】多層配線の側壁による入射光の上方への乱反射を抑える。

【解決手段】複数の配線層115、117、119の少なくとも1つの配線層の側壁面が、複数の配線層115、117、119の上方から入射する光の入射方向に対して、光の受光側となる下方よりも光の入射側となる上方の方が長くなる逆方向のテーパ状に形成される。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

半導体装置の製造方法

【課題】欠陥の発生を防止し且つ電気的特性に優れた強誘電体キャパシタを用いた半導体装置の製造方法を提供する。

【解決手段】第1の導電層40を形成し、第1の導電層40の表面に酸化膜10を形成し、酸化膜10を大気にさらし、酸化膜10を、減圧下且つ第1の温度で減圧加熱処理し、減圧加熱処理された酸化膜10を大気にさらすことなく、減圧下且つ第1の温度よりも低い第2の温度で、非晶質の第1の誘電体層41を酸化膜10上に形成し、第1の温度よりも高い第3の温度で、非晶質の第1の誘電体層41を結晶化する。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板の側面下端のエッジ部を保護し、且つ、装置全体を薄型化する。

【解決手段】 シリコン基板1の側面に形成された円弧状に凹んだ傾斜面13にはアモルファスシリコンやポリイミド系樹脂等からなる側部保護膜14が設けられている。これにより、シリコン基板1の側面下端のエッジ部1aを保護することができる。この場合、側部保護膜14の下端部下面はシリコン基板1の下面と面一となっているので、シリコン基板1の下面に樹脂保護膜を形成する場合と比較して、薄型化することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】高信頼性でかつ高レイアウト密度配線と混載可能な容量素子を備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明は、容量素子を有する半導体装置であって、アルミニウム合金膜102と、高融点金属膜を含む上層バリア膜103とを含む金属配線200aおよび下部電極200bと、下部電極200b上に形成された容量絶縁膜104と、容量絶縁膜104上に形成された上部電極105とを有する。高融点金属膜の膜厚は、40nm以上、80nm以下であり、容量絶縁膜104は、有機シランを原料としたシリコン酸化膜からなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 下部電極とビア配線とのコンタクト抵抗の増大を抑制可能な、容量素子を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置は、半導体基板101上に形成され下部電極110と誘電体膜120と上部電極130とを有する容量素子を含む。容量素子の下部電極110は、例えばTi膜である金属膜111と、金属膜111上に形成されたTiN膜113とを有する。半導体装置は更に、容量素子を覆う絶縁膜142と、絶縁膜142を貫通して下部電極110のTiN膜113と接触するビア配線150とを含む。TiN膜113は好ましくは30nm未満の厚さを有する。Ti膜111の表面の少なくとも一部には、ビア配線150とTi膜111との間に介在するよう、Ti膜111の窒化処理による窒化層112が形成されている。

(もっと読む)

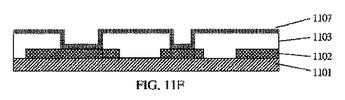

光焼結及び/またはレーザー焼結を強化するためのバッファ層

電子部品間に電気を伝えるための配線を製造するために、基板上に導電線を堆積させる。基板上にパターン形成された金属層が形成され、次いで低熱伝導率を有する材料の層が、パターン形成された金属層及び基板上に被覆される。低熱伝導率を有する材料の層を通るビアが形成されることによって、パターン化された金属層の一部が露出される。次いで、導電性インクの膜が低熱伝導率を有する材料の層上及びビア内に被覆されることによって、パターン化された金属層の前記部分が被覆され、その後焼結される。パターン化された金属層の部分に被覆された導電性インクの膜は、低熱伝導率を有する材料の層上に被覆された導電性インクの膜ほど、焼結由来のエネルギーを吸収しない。低熱伝導率を有する材料の層は、ポリイミドなどのポリマーであり得る。  (もっと読む)

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力を開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

マスクを使用せずに導電性ビアに対して裏面位置合わせを行うことによる半導体構成部品の製造方法

半導体構成部品(90)を製造する方法が、回路面(54)と、裏面(56)と、導電性ビア(58)とを有する半導体基板(52)を提供するステップと、導電性ビア(58)の端子部分(76)を露出するために、基板(52)の一部分を裏面(56)から除去するステップと、端子部分(76)を封入するポリマー層(78)を裏面(56)に堆積するステップと、次いで、ポリマー層(78)および端子部分(76)の端部を平坦化して、ポリマー層(78)に埋め込まれた自己整合導体を形成するステップとを含む。導電性ビア(58)に電気的に接触させて、端子接点(86)や裏面再分配導体(88)等の追加の裏面要素を形成することもできる。半導体構成部品(90)は、半導体基板(52)と、導電性ビア(58)と、およびポリマー層(78)に埋め込まれた裏面導体とを有する。積重ね半導体構成部品(96)が、電気的に互いに通じる位置の整合した導電性ビア(58)を有する複数の構成部品(90-1、90-2、90-3)を有する。  (もっと読む)

(もっと読む)

161 - 180 / 759

[ Back to top ]