Fターム[5F033WW02]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 長さ、寸法 (1,572) | 厚さ (759)

Fターム[5F033WW02]に分類される特許

101 - 120 / 759

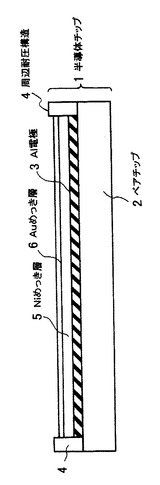

半導体チップおよびこれを用いた半導体装置

【課題】接続導体との間のはんだ接合部の信頼性を確保する。

【解決手段】ジンケート法による無電解めっき法を用いて、半導体チップ1の表面側のAl電極3の上にNiめっき層5が形成される。Al電極3の上には、選択的にNiめっき層5が析出されるため、周辺耐圧構造4部分には、Niめっき層5は形成されない。また、形成されるNiめっき層5は、所定の厚さに均一に形成することができる。続いて、Niめっき層5の上にAuめっき層6が形成される。無電解めっき法を用いることによって、Auめっき層6もNiめっき層5と同様に、Niめっき層5の上に選択的、かつ均一に形成される。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】基板を薄板化しても基板の反りを抑制でき、耐熱性、機械特性に優れた絶縁膜で保護された半導体素子及びその製造方法を提供する。

【解決手段】基板1の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板の表面に、芳香族テトラカルボン酸及び芳香族テトラカルボン酸二無水物から選ばれる1種以上のアシル化合物を、前記芳香族ジアミンよりも1モル%以上多く反応して得られるポリアミド酸を含むポリイミド前駆体組成物を塗布し、イミド化して絶縁膜3を形成し、第1表面電極2及び絶縁膜3が少なくとも形成された基板1を、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板上にポリイミドなどからなる保護膜が形成された半導体装置の製造中に、保護膜の上面層が変質しても、この変質による悪影響が生じないようにする。

【解決手段】 ポリイミドなどからなる保護膜5に開口部6を形成したとき、保護膜5の開口部6を介して露出された接続パッド2の上面にポリイミドなどからなる残渣が残存する場合がある。そこで、次に、この残渣を酸素プラズマアッシングにより除去する。この場合、保護膜5の上面側に凸凹構造の変質層Aが形成される。次に、開口部4、6を介して露出された接続パッド2の上面に形成された自然酸化膜をアルゴンプラズマエッチングにより除去する。この場合、変質層Aがさらに変質して網目構造の変質層Cが形成される。次に、チタンなどからなる第1の下地金属層7を成膜する。この場合、第1の下地金属層7は網目構造の変質層Cの上面に成膜されるため、その界面の密着力は高い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の配線における電気的干渉を低減する。

【解決手段】半導体装置1Aにおける接続パッド12と半田端子23を繋ぐ電流経路となる配線を、半導体基板11を覆う下地絶縁膜14上に形成された下層配線17と、下地絶縁膜14を覆うフィルム材19上に形成された上層配線21とを組み合わせて構成するとともに、半導体基板11から比較的離間した位置に配されて、下層配線17よりも半導体基板11と電気的に干渉しにくくなっている上層配線21の割合を高くするように、上層配線21を下層配線17よりも長く形成することとした。

(もっと読む)

低水分誘電体膜を形成する方法

周期的な酸化およびエッチングのための装置と方法

成膜方法、半導体装置の製造方法及び半導体装置

【課題】表面の平坦性の優れたシリコン膜を形成する成膜方法、半導体装置の製造方法及び半導体装置を提供する。

【解決手段】基体上にジシラン及びトリシランの少なくともいずれかを用いて第1温度で第1膜を形成する第1膜形成工程と、前記基体及び前記第1膜を、水素を含む雰囲気中において、前記第1温度から、前記第1温度よりも高い第2温度に向けて昇温する昇温工程と、前記昇温の後に、前記第1膜の上に、シランを用いて前記第2温度で第2膜を形成する第2膜形成工程と、を備えたことを特徴とする成膜方法が提供される。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

絶縁膜、積層体、半導体装置および半導体装置の製造方法

【課題】誘電率が低く、半導体装置の製造に適用した際に絶縁不良等の問題を生じにくい絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成されたものであって、フッ素系ガスでエッチングした際のエッチングレートが、SiO膜の0.75倍以下であることを特徴とする。前記重合性反応基は、芳香環と、当該芳香環に直接結合するエチニル基またはビニル基とを有するものであり、前記重合性化合物において、前記芳香環由来の炭素の数は、当該重合性化合物全体の炭素の数に対して、15%以上、38%以下であるのが好ましい。

(もっと読む)

半導体集積回路

【課題】少なくともロジック回路ブロックを含む半導体集積回路において、半導体集積回路の電源用パッドとロジック回路ブロックの電源ラインとを接続する電源配線、及び/又は、半導体集積回路のグランド用パッドとロジック回路ブロックのグランドラインとを接続するグランド配線の抵抗値を下げる。

【解決手段】この半導体集積回路は、半導体基板と、半導体基板上にそれぞれの層間絶縁膜を介して形成され、半導体基板に形成された複数のトランジスタに接続されて複数のトランジスタと共に少なくともロジック回路ブロックを構成する複数の配線層と、複数の配線層が形成された半導体基板上に層間絶縁膜を介して形成され、複数の配線層における最大膜厚の5倍〜20倍の膜厚を有する最上層の配線層とを具備する。

(もっと読む)

半導体装置、及びその製造方法

【課題】配線の導通信頼性を損なうことなく、エアギャップを形成でき、配線間容量Cが低減した配線膜構造を有する半導体装置を提供することである。

【解決手段】 半導体装置の製造方法において、第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜に配線膜を形成する配線膜形成工程と、前記配線膜が形成されてない箇所の前記第1絶縁膜にドライエッチングで溝を形成するドライエッチング工程と、前記ドライエッチング工程の後、前記溝が埋め尽くされることが無いよう、前記配線膜および前記溝上に第2絶縁膜を形成する第2絶縁膜形成工程とを具備する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

電子デバイスの製造方法

【課題】接合熱処理温度が低くて済み、凝固後は高い融点を確保し得る高耐熱性の電子デバイス及びその製造方法の提供。

【解決手段】複数枚の基板WF1〜WFrのそれぞれは、縦導体31と、接続導体4とを有している。複数枚の基板WF1〜WFrのうち、隣接する基板WF1、WF2は、一方の基板WF2の接続導体(縦導体)31が、他方の基板WF1の接続導体4と、接合膜5によって接合されている。接合膜5は、第1金属または合金成分と、それよりも融点の高い第2金属または合金成分とを含み、凝固後の溶融温度が第1金属または合金成分の融点よりも高くなっている。

(もっと読む)

絶縁膜のダメージ回復方法及びダメージが回復された絶縁膜

【課題】層間絶縁膜のダメージ回復処理の際に、銅配線層などの配線材料上に回復剤が残留することがなく、かつドライプロセスによる処理が可能な、量産性に優れる絶縁膜のダメージ回復方法を提供する。

【解決手段】プラズマ処理によりダメージを受けた絶縁膜を、炭酸エステル系の化合物である回復剤と接触させてダメージ回復処理を行うことを特徴とする絶縁膜のダメージ回復方法を選択する。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

電子デバイスの製造方法および該方法により製造された電子デバイス

GaAs半導体基板(HS)を備えた電子デバイスにおいて、基板前面には半導体素子(BE)が、基板背面には多層の背面金属化部(RM)が設けられている。このような電子デバイスのために、背面金属化部の有利な積層体構造が提案される。たとえば背面金属化部は固着層としてAu層を有している。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】空孔を含む絶縁膜を用いる半導体装置及びその製造方法において、配線間耐圧を向上すると共に配線間容量を低減する。

【解決手段】半導体装置200の製造方法は、基板上に、単一層からなり且つ空孔形成材料202を含む絶縁膜203を形成する工程(a)と、絶縁膜203の表面部である第1領域210には空孔を形成することなく、絶縁膜203における第1領域210よりも下方の第2領域には空孔形成材料202の除去により空孔204を形成する工程(b)と、絶縁膜203に少なくとも1つの配線溝211を形成する工程(c)と、配線溝211を埋め込むように導電膜215を形成する工程(d)と、配線溝211からはみ出た余剰部分の導電膜215を除去することにより配線207を形成する工程(e)とを備える。

(もっと読む)

貫通電極基板及び貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板は、表裏を貫通する貫通孔を有する基板と、前記貫通孔内に充填され、金属材料を含む導通部と、を備え、前記導通部は、結晶粒径が29μm以上の金属材料を少なくとも含み、前記導通部の一端は、前記導通部の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部は、面積重み付けした平均結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】信頼性の高い半導体集積回路装置の製造プロセスを提供する。

【解決手段】銅ダマシン配線プロセスのバリアメタル膜のタンタル系積層膜に関し、スパッタリング成膜チャンバ内のシールド内面に、比較的薄い窒化タンタル膜およびタンタル膜が交互に成膜されるが、この連続成膜プロセスを断続的に繰り返すと、膜の内部応力により剥がれて、異物やパーティクルの原因となる。この異物やパーティクルの防止のため、繰り返し、成膜するに際して、所定の間隔を置いて、厚い膜厚を有する異物防止用タンタル膜をチャンバの実質的な内壁に成膜する工程を設ける。

(もっと読む)

101 - 120 / 759

[ Back to top ]