Fターム[5F033WW02]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 長さ、寸法 (1,572) | 厚さ (759)

Fターム[5F033WW02]に分類される特許

21 - 40 / 759

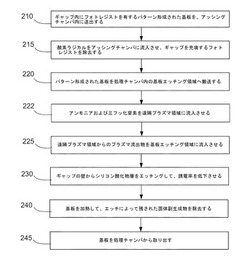

アッシュ後の側壁の回復

【課題】有効誘電率を増大させ、デバイスの性能を制限する可能性がある環境に低K薄膜を曝した後、より低い有効誘電率を維持する新しいプロセスを提供する。

【解決手段】集積回路の2つの導電性構成要素の間に存在する、有効誘電率を低下させる方法。その方法は、低K誘電体層の酸素が豊富な部分に対して選択的な気相エッチの使用を伴う。エッチング速度は、エッチプロセスが比較的高Kの酸素が豊富な部分を通過し、低K部分に達すると減じる。気相エッチプロセスが望ましい低K部分を容易に除去することはないため、エッチプロセスのタイミングを簡単に合わせることができる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】配線抵抗の上昇や絶縁耐性の劣化を抑制しつつ、配線信頼性を確保する。

【解決手段】半導体装置100は、半導体基板と、半導体基板上に設けられた層間絶縁膜50と、層間絶縁膜50に埋め込まれた、Cuにより構成される配線10と、配線10の表層に設けられた、銅錯体を含有する表面層20と、を備える。配線10の表層に銅錯体を含有する表面層20を備えることにより、配線抵抗の上昇や絶縁耐性の劣化を抑制しつつ、配線信頼性を確保することができる。

(もっと読む)

電子部品用積層配線膜

【課題】 Moの持つSiバリヤ性、ITOコンタクト性という利点を維持しながら、耐酸化性を改善し、尚且つCuとの積層時や信号ケ−ブルの取り付け等の加熱工程を経ても低い電気低抵値を維持できる、電子部品用積層配線膜を提供する。

【解決手段】 基板上に金属膜を形成した電子部品用積層配線膜において、Cuでなる主導電層と、該主導電層の一方の面および/または他方の面を覆う被覆層からなり、該被覆層は原子比における組成式がMo100−XNiX、10≦X≦70で表され、残部不可避的不純物からなるMo−Ni合金である電子部品用積層配線膜。

(もっと読む)

半導体発光素子

【課題】メタル電極に設けられた延伸部の表面を覆う絶縁膜の剥離が抑制された半導体素子を提供する。

【解決手段】半導体からなる活性層に積層されたn型またはp型の半導体層と、該半導体層の上に配置され接続部および延伸部を有するメタル電極と、該メタル電極の該延伸部の上面および側面を少なくとも覆う絶縁膜と、を備え、該延伸部はメタル多層膜で形成され、該メタル多層膜は少なくとも2層の第1メタル層と、該第1メタル層と交互に積層された第2メタル層とを含み、かつ、その最上層は該第2メタル層のひとつであり、該メタル多層膜に含まれる該最上層の第2メタル層以外の第2メタル層の各々の端面が該延伸部の側面に露出して該絶縁膜と接しており、該第2メタル層を構成する第2メタル材料は該第1メタル層を構成する第1メタル材料よりも導電率は低いが該第1メタル材料よりも該絶縁膜との密着強度に優れている。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、この配線20を窒素プラズマに曝露する。これにより、既存の側壁保護膜32にAlNが合わさって側壁保護膜32を分厚くすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】マスク倒れを防止でき、しかもAlCu配線のサイドエッチングを防止することができる半導体装置およびその製造方法を提供すること。

【解決手段】第2層間膜17上に、下側TiN/Ti膜29、AlCu膜30および上側TiN/Ti膜31を順に積層することによってAlCu配線層34を形成する。次に、AlCu配線層34上に、SiO2からなるハードマスク37を形成する。そして、このハードマスク37を利用してAlCu配線層34をドライエッチングすることにより、第1AlCu配線20を形成する。第1AlCu配線20の形成後、この配線20の表面を覆うように、SiN膜38を形成する。これにより、既存の側壁保護膜36にSiN膜38が合わさって側壁保護膜32が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】配線レイアウトや配線構造の複雑化や大幅な変更を伴うことなく、積層配線間に生じるクロストークノイズを低減する。

【解決手段】配線103上に絶縁膜104及び106を挟んで配線108が形成されている。配線103と配線108とは平面視において少なくとも部分的にオーバーラップしている。少なくとも配線103と配線108とのオーバーラップ部分の前記絶縁膜中に導電性シールド層105が形成されている。

(もっと読む)

電力用半導体装置及びその製造方法

【課題】本発明は、信頼性の高い外部電極との接続構造を有する電力用半導体装置及びその製造方法の提供を目的とする。

【解決手段】本発明の電力用半導体装置は、段差を有する絶縁膜9と、絶縁膜9の前記段差を覆って形成された上部配線10と、上部配線10上の少なくとも前記段差の側壁に対応する部分を含む所定箇所に、部分的に形成された酸化膜16と、上部配線10及び酸化膜16上に形成され、半田21により外部導体22と接合するバリア層20とを備える。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体装置およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体装置等を提供する。

【解決手段】半導体装置は、下層側の第1導電体部および上層側の第2導電体部と、第1の導電体部と第2の導電体部との間に設けられた、厚膜状の絶縁体層と、この絶縁体層に対する貫通孔の内面形状に倣うように形成され、第1導電体部と第2導電体部とを電気的に接続するコンタクト部とを備え、貫通孔のテーパ角が鋭角となっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 薄板化の際に層間絶縁膜が破損することを抑制できる半導体装置を得る。

【解決手段】 第1の硬度を有する材料で構成された基板10と、基板10の第1主面10aに設けられたドリフト層11と、ドリフト層11上に絶縁膜60を介して形成されたゲート電極70と、ゲート電極70を覆うように形成され、第1の硬度よりも小さい第2の硬度を有する材料で構成された層間絶縁膜80とを備え、基板10とドリフト層11とを合わせた厚みは200μm以下であり、層間絶縁膜80に、平面視において、全ての内角が90°より大きい多角形、円形または楕円形の開口90が設けられている半導体装置。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

Cu合金膜および表示装置

【課題】酸化物半導体層を用いた表示装置において、保護膜形成時のプラズマ処理におけるCu配線の酸化を有効に防止し得る技術を提供する。

【解決手段】基板1の上に、基板側から順に、薄膜トランジスタの半導体層4と、電極に用いられるCu合金膜5と、保護膜6と、を備えており、半導体層は酸化物半導体からなる。Cu合金膜5は、基板側から順に、第一層(X)5aと第二層(Z)5bを含む積層構造を有し、第一層(X)は、純Cu、またはCuを主成分とするCu合金であって第二層(Z)よりも電気抵抗率の低いCu合金からなり、第二層(Z)は、Zn、Ni、Ti、Al、Mg、Ca、W、Nb、希土類元素、Ge、およびMnよりなる群から選択される少なくとも1種の元素を合計で2〜20原子%含むCu−Z合金からなり、第二層(Z)の少なくとも一部は、前記保護膜と直接接続されている。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、半導体装置のレイアウト方法

【課題】新たな要因に起因したクラックの発生を抑制すること。

【解決手段】第1のAl配線31と絶縁膜33とを含む第1のAl配線層30と、第2のAl配線41と絶縁膜43とを含む第2のAl配線層40と、複数の第3のAl配線51と絶縁膜52とを含む第3のAl配線層50と、第1のAl配線31と第2のAl配線41とを接続する第1のビア32と、第2のAl配線41と第3のAl配線51とを接続する第2のビア42とを有し、少なくとも一部の第3のAl配線51は隣り合う第3のAl配線51同士の間隔Bが2.25μm以下である隙間60を形成しており、平面視で隙間60の中の少なくとも一部は第1のAl配線31及び第2のAl配線41と重ならない領域を有し、隙間60を形成するように対峙した第3のAl配線51の対峙方向の配線幅Cは15μmより大きく、第2のビア42同士の間隔Fは第2のビア42の径Gの3倍以上である半導体装置。

(もっと読む)

半導体装置用Al合金膜

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられた半導体装置用Al合金膜を提供する。

【解決手段】500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が500nm〜5μmであることを特徴とする半導体装置用Al合金膜。(a)Alマトリックスの最大粒径が800nm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一表面上に絶縁膜を介して形成された導電層と、半導体基板の他面上に形成されたバンプ部と、導電層とバンプ部とを接続する半導体基板を貫通する貫通電極部とを有する半導体装置を提供する。

【解決手段】半導体基板の他面側から導電層に接続する貫通孔を形成し、貫通孔及び他面上にメタル膜(バリアメタル及びシードメタル)6を形成し、その上にフォトレジスト10を形成し、貫通孔より大きなパターンに加工してメッキマスク層を形成し、電解メッキ法により銅からなる第1メッキ膜7を形成して、貫通電極部と第1バンプ部を形成し、第1バンプ部上に第2バンプ部となる第2メッキ膜8を形成する。

(もっと読む)

下地導電層付き基板の製造方法および貫通電極基板の製造方法

【課題】製造時間とコストの大幅な削減が可能な下地導電層付き基板および貫通電極基板の製造方法を提供する。

【解決手段】厚さ方向に複数の貫通孔2を有するガラス基板3の貫通孔2内に下地導電層4を有する基板の製造方法であって、前記ガラス基板3の貫通孔2内に、金属粒子と分散媒とを含有する流動性の導電性組成物(金属インク)の層を形成する工程と、この導電性組成物の層を加熱して、貫通孔2の内壁面に金属粒子の金属を主体とする下地導電層4を形成する工程とを備える方法である。貫通電極基板5の製造方法は、こうして形成された下地導電層4上に電解めっき等により導電性金属の層を形成して、貫通孔2内に充填された貫通電極6を形成する工程を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ワイヤがCuワイヤであっても、ボンディング時の衝撃による金属のスプラッシュを抑制する。

【解決手段】半導体装置は、電極パッド103を有する半導体チップと、電極パッド103にボンディングされたワイヤ(例えばCuワイヤ105)と、を有している。電極パッド103において、ワイヤがボンディングされている領域の少なくとも表層はルテニウム又は酸化ルテニウムにより構成され、その表層の膜厚は20nm以上である。

(もっと読む)

21 - 40 / 759

[ Back to top ]