Fターム[5F033WW02]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 長さ、寸法 (1,572) | 厚さ (759)

Fターム[5F033WW02]に分類される特許

741 - 759 / 759

金属の化学的機械的研磨用の新規なスラリー

一般に集積回路の製造に有用な、金属を取り除くための、及び、特に貴金属の化学的機械的研磨用の、スラリーは、過ヨウ素酸、研磨剤、及び緩衝系を組み合わせることによって、形成されてもよく、ここでそのスラリーのpHは、約(4)と約(8)との間にある。

(もっと読む)

(もっと読む)

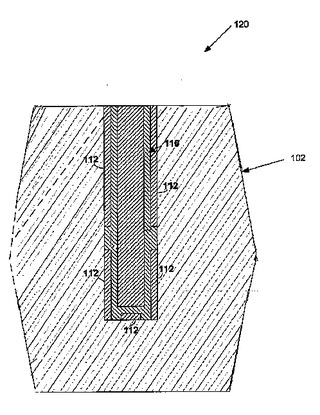

無電解メッキ化学反応を用いた深いビアシードの修復

高アスペクト比ビア内に連続シード層を形成する方法とそれに関連付けられる構造体を記載する。この方法は、基板内に凹部(104)を形成する段階と、凹部内に非連続金属層を形成する段階と、凹部内の非連続金属層(112)と、少なくとも1つの非堆積領域(109)を活性化させる段階と、凹部内の非連続金属層及び少なくとも1つの非堆積領域上にシード層(116)を無電解メッキする段階と、実質的にボイドがなく、金属が充填された凹部を形成するようシード層上に金属充填層を形成する段階を含む。  (もっと読む)

(もっと読む)

ビア・ファースト・デュアルダマシン相互接続配線形成のための構造体充填方法

厚さが溶剤により容易に制御できる間隙充填底部反射防止膜を用いたビア・ファースト・デュアルダマシン相互接続構造体を形成する方法である。基板に塗布後、底部反射防止膜は低温焼成により部分硬化される。次に皮膜したウェハ上に溶剤を施し、膜と一定時間接触させて置く。底部反射防止膜の焼成温度と溶剤との接触時間により制御できる速さで溶剤が底部反射防止膜を除去しつつも、薄い底部反射防止膜を作り誘電体積層上に最適の光吸収特性は維持される。本方法の別の実施例では底部反射防止膜を充分除去し、ビアを単に部分充填し、続く処理工程でビア底部が保護されるようにしてもよい。溶剤はウェハから除去され、底部反射防止膜は高温焼成処理により完全に硬化される。次にウェハはフォトレジストにより被覆されトレンチパターンが露出する。使用される底部反射防止膜材によりトレンチパターン形成上、より平坦な表面形状が維持され、誘電体積層上に無機光吸収材層を設ける必要がなくなり、トレンチのエッチング工程時ビアの底部を保護し、溶剤を用いてビアの厚さを制御することにより境界問題の発生を防止する。 (もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

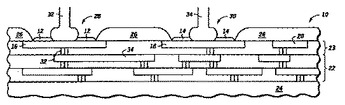

能動領域ボンディングの両立性のある高電流構造体

ボンディング・パッド下方に各回路を有する集積回路。一実施例において、集積回路は基板と、最上部導電層と、1つ以上の中間導電層と、絶縁材料から成る各層と、各デバイスとを具備する。最上部導電層は少なくとも1個のボンディング・パッド及び比較的硬質の材料から成る副層を有する。1つ以上の中間導電層は最上部導電層及び基板の間に形成する。絶縁材料から成る各層は各導電層を分離する。更に、絶縁材料から成る各層のうちの1つの層は比較的硬質で、最上部導電層及びこの最上部導電層に最も近接した中間導電層の間に位置する。各デバイスは集積回路に形成する。また、最上部導電層に最も近接した少なくとも中間導電層は、ボンディング・パッド下方の各選択デバイスの機能的相互接続部に対して適合する。

(もっと読む)

(もっと読む)

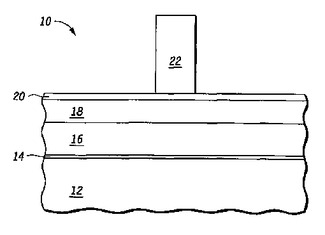

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

多層配線構造の製造方法

【課題】高集積化、微細化されたパターンにおいて、ビアホール等を良好に埋め込み、かつ電気抵抗率の低い埋め込み型の多層配線構造を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法が、絶縁層に孔部を形成する工程と、孔部の表面に、物理的真空堆積法で、平均膜厚が0.2nm以上で10nm以下である触媒層6、または触媒層の平均膜厚が、触媒層の材料原子の1原子層以上で10nm以下である触媒層6、を形成する工程と、触媒層を触媒に用いた無電解めっき法により、孔部の表面に無電解めっき層7を形成する工程と、無電解めっき層をシード層に用いた電解めっき法で、孔部を電解めっき層8で埋め込む工程とを含む。

(もっと読む)

バリヤ金属上に直接銅めっきするマルチステップ電着法

本発明の実施形態は、基板表面に、通常はバリヤ層に銅シード層を堆積させる方法を教示している。その方法は、基板表面を銅溶液に入れるステップであって、該銅溶液が錯体形成銅イオンを含んでいる、前記ステップを含んでいる。電流又はバイアスを基板表面に印加し、錯体形成銅イオンを還元してバリヤ層に銅シード層を堆積させる。 (もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

電解加工装置及び電解加工方法

本発明は、被加工物の不良品化を招くと考えられるピットの発生を効果的に防止することができるようにした電解加工装置及び電解加工方法を提供する。この電解加工装置は、被加工物を加工する加工電極(210)と、被加工物に給電する給電電極(212)と、加工電極(210)と給電電極(212)との間に電圧を印加する電源(232)と、加工電極(210)及び給電電極(212)を内部に収納した耐圧容器(200)と、耐圧容器(210)内に高圧液体を供給する高圧液体供給系(204)を有する。  (もっと読む)

(もっと読む)

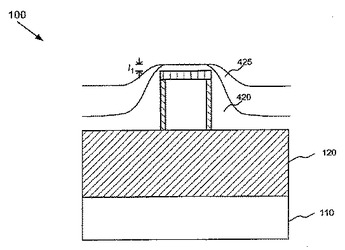

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

銅コンタクトを有する集積回路ダイおよび該集積回路ダイのための方法

集積回路ダイ(10)は、銅コンタクト(16,18)を有する。銅コンタクトは、周辺空気にさらされると天然の酸化銅を形成する。有機材料を、銅コンタクトに塗布する。有機材料は、天燃の酸化銅と反応して、銅コンタクト上に有機コーティング(12,14)を形成し、さらなる銅の酸化を防ぐ。このようにして、たとえば100℃を上回る高温でさらに処理を行なっても、過剰な銅の酸化によって妨げられることはない。たとえば高温でワイヤ・ボンド・プロセスを行なっても、有機コーティングのために、信頼性の高いワイヤ・ボンディングを妨げる過剰な酸化には至らない。したがって、有機コーティングを形成することによって、信頼性が高くかつ耐熱性のあるワイヤ・ボンド(32,34)が可能になる。あるいは、集積回路ダイを形成する間のいつでも、露出する銅に有機コーティングを形成して、銅の酸化の形成を防止または抑制することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

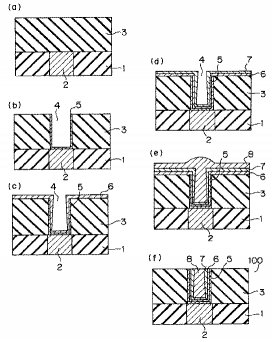

デュアルダマシンによる半導体装置の製造方法

【課題】 放熱性が良好で、製造コストが低く、微細加工に好適なデュアルダマシンによる半導体装置の製造方法を提供する。

【解決手段】 基板1上に無機層間膜5、有機層間膜6、シリコン酸化膜からなる下部マスク7、シリコン窒化膜からなる上部マスク8を形成し、上部マスク8上にシリコン酸化窒化膜からなり膜厚が20乃至100nmであるカバーマスク10を形成する。そして、反射防止膜11及びレジスト膜12を形成する。次に、レジスト膜12をマスクとして、反射防止膜11、カバーマスク10、下部マスク7をエッチングする。そして、カバーマスク10をマスクとして、有機層間膜6及び無機層間膜5をエッチングしてビアホールを形成する。次に、上部マスク8をマスクとして有機層間膜6をエッチングして配線溝を形成する。

(もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

配線構造およびその製造方法

【課題】感光性絶縁膜を用いたダマシン配線法により、微細で信頼性の高い多層配線構造を形成する。

【解決手段】感光性ポリシラザンを主成分とした感光性絶縁膜で第1ビアホール6を有するビアホール用絶縁膜7を形成し、全面にスピン塗布法で第2の感光性絶縁膜8を形成する。そして、フォトリソグラフィ法による露光/現像のみで上記第1ビアホール6の上部に配線溝9あるいは第2ビアホール10を形成する。そして、この配線溝9および第2ビアホール10に導電体材料を埋め込んでデュアルダマシン配線を形成する。ここで、感光性絶縁膜の下層に反射防止機能を有しそのまま層間絶縁膜として使用できる絶縁膜を形成する。

(もっと読む)

導電線間に空隙を有する導電線構造体の製造方法

【課題】半導体回路の隣接導体線間容量性クロストークを減少させる。

【解決手段】フィラー材料を蒸発させて形成された空隙を有する金属被覆体の製造方法で、フィラー材料30は透過性の誘電層40により覆われる。フィラー材料はPPG、PB、PEG、非結晶フッ化炭素及びPCLからなる群から選択され、スピン・オン法又はCVD法により形成される。フィラー材料を、間隔をあけた導電線20及び半導体構造体10上に形成し、エッチバック処理し、導電線の上面を露出させる。次に、フィラー材料上に透過性の誘電層40を形成する。透過性の誘電層は分解したガス相フィラー材料が拡散するのを許容する性質がある。フィラー材料を蒸発させ、気相フィラー材料に変化させる。気相のフィラー材料は透過性の誘電層を通じて拡散して、間隔をあけた導電線の間に空隙を形成する。透過性の誘電層上に絶縁層が形成される。

(もっと読む)

多層配線構造及びその製造方法

【課題】 エレクトロマイグレーション耐性と、ストレスマイグレーション耐性を同時に向上させる多層配線構造及びその製造方法を提供する。

【解決手段】 AlCu膜103Cと、厚みが0〜15nmのTi膜との反応によりAl3 Ti層103DをAlCu膜とTiN膜の界面に形成することにより、界面拡散を抑制し、かつAl3 Ti層形成時に発生する引張り応力を低減し、EM耐性を向上させる。その後のFSG膜104AをHDP−CVD法で成膜する際に、ウェハ裏面に不活性ガスを流してウェハを冷却し、ウェハ温度を450℃以下にすることにより、FSGとAlCuの熱膨張率差に起因するAlCu膜の残留引張り応力の発生を低減し、SM耐性及びEM耐性を向上させる。さらに、FSG膜の上にSiON膜を設けることにより、FSG膜の遊離フッ素の上方への拡散を阻止して、上層配線の剥がれを防止する。

(もっと読む)

フリップチップ用高性能シリコンコンタクト

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

741 - 759 / 759

[ Back to top ]