Fターム[5F033WW02]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 長さ、寸法 (1,572) | 厚さ (759)

Fターム[5F033WW02]に分類される特許

61 - 80 / 759

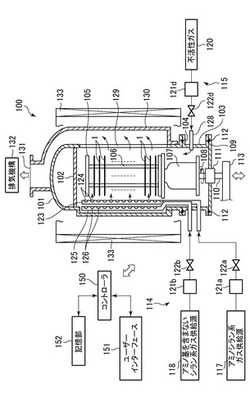

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

電子部品の製造方法

【課題】高温で成膜される低融点金属の凝集を防止し、十分なバリア性及びぬれ性を有するバリア層を形成して、凹部に低融点金属を付け回り良く充填する。

【解決手段】電子部品の製造方法が、4Pa以上20Pa以下の圧力下で、被処理体306と接する電極301に第1のバイアス電力を印加し、プラズマ処理により被処理体306の上にTiNxからなる第1のバリア層404を成膜する手順と、4Pa以上20Pa以下の圧力下で、電極301に第1のバイアス電力よりも小さいイオン入射エネルギーを与える第2のバイアス電力を印加し、またはバイアス電力を印加しないで、プラズマ処理により第1のバリア層の上にTiNxからなる第2のバリア層405を成膜する手順と、第2のバリア層405の上に、Tiからなる第3のバリア層409を成膜する手順と、第3のバリア層409の上に低融点金属406を充填する手順と、を有する。

(もっと読む)

半導体装置の製造方法並びにコンタクトホール及び/又はラインの埋め込み方法

【課題】 表面ラフネスの精度をさらに改善でき、コンタクトホールやラインなどの微細化の進展に対応可能なアモルファスシリコン膜を成膜できる半導体装置の製造方法を提供すること。

【解決手段】 半導体装置内部のコンタクトホール5及び/又はラインが形成された層間絶縁膜である下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜4を形成する工程と、を備える。

(もっと読む)

チップの製造方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

半導体構造同士を直接結合する方法、およびこの方法を使用して形成された結合された半導体構造

【課題】半導体構造同士を直接結合する方法を提供すること。

【解決手段】本発明の実施形態は、半導体構造同士を直接結合する方法を含む。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ間の境界面に、キャップ層を提供することができる。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ内に、不純物が提供される。そのような方法を使用して、結合された半導体構造が形成される。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いる配線形成方法で、特に最上層の配線を含む上層配線を形成する場合、接続孔の周囲に生ずるクラウンフェンスを容易に除去して信頼性の高い半導体装置を提供する。

【解決手段】 接続孔19a、19b上に形成された開口を有するマスク層21をマスクとして、第3絶縁膜17および第3絶縁膜17より密度の小さい、あるいは比誘電率が小さい第2絶縁膜16をエッチングして配線溝22を形成すると、接続孔19bに埋め込まれた有機性材料20の突出部と同時に、第2絶縁膜16の構成材料を主成分とするクラウンフェンス23が生ずる。これに対しマスク層21の除去工程を兼ねるなどの処理において、少なくとも配線溝22の内部にプラズマ処理を施した後、第2絶縁膜16を溶解可能な処理液で処理し上記のプラズマ処理で変質したクラウンフェンス25を選択的に除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

銅の電着方法

【課題】特に半導体集積回路(IC)デバイス製造の分野において、約100nmより小さい、好適には約70nmより小さい、更に好適には約50nmより小さい、より好適には約35nmより小さい幅を有するトレンチ、バイアなどの開口部を充填する電着方法を提供する。

【解決手段】0.5mmol・l−1と50mmol・l−1との間に含まれる銅イオン濃度と、電着浴の体積あたり0.05%と10%との間に含まれる酸濃度とを有する電着浴中に基板を浸責し、銅の堆積物を電着する。

(もっと読む)

半導体装置の製造方法

【課題】より視認が容易なアライメントマークを簡素な工程で形成することが可能な、半導体装置の製造方法を提供する。

【解決手段】半導体基板SUBの主表面上に、主表面に対して段差を有するパターンMKが形成される工程と、パターンMK上に、半導体材料を含む第1の半導体層PS1が形成される工程と、第1の半導体層PS1上に、半導体材料を含む第2の半導体層PS2が形成される工程と、第2の半導体層PS2上にレジストパターンRSが形成される工程とを備えている。レジストパターンRSが形成される工程において、パターンMKが位置合わせマークとして用いられる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CFx膜を層間絶縁膜として有する多層配線構造の半導体装置において、低誘電率であるCFx膜の利点を生かすことができ、かつCMP処理による特性の劣化を防止することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、CFx膜を成膜する工程(a)と、CFx膜に所定パターンの凹部を形成する工程(b)と、凹部を埋めかつCFx膜上にわたって配線層を設ける工程(c)と、凹部内以外の前記CFx膜上の余剰の配線層をCMP(化学機械研磨)によって除去してCFx膜の表面を露出させる工程(d)と、を有し、工程(b)の前または後において、CFx膜の表面を窒化する工程(e)を備える。

(もっと読む)

パワーデバイス

【課題】ポリイミド膜上に設けた電極パッドに導体バンプなしにAlワイヤを確実に接合でき、ポリイミド膜からの電極パッドの剥離や電極パッドとAlワイヤとの接合不良を防止できるパワーデバイスを提供する。

【解決手段】絶縁基板1上に設けられた半導体素子(2,3,6)と、絶縁基板1上に形成され、半導体素子(2,3,6)を覆う軟質ポリイミド膜11と、軟質ポリイミド膜11上に形成された電極パッド9と、電極パッド9にワイヤボンディングにより一端が接合されたAlワイヤ12とを備える。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体集積回路上及びスクライブ領域上を覆うパッシベーション膜を備えた半導体装置の製造装置に関し、パッシベーション膜に起因する半導体基板の反りを低減することを課題とする。

【解決手段】スクライブ領域B上に設けられたパッシベーション膜13に、複数の回路形成領域Aを囲むように格子状の溝47を形成した。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

半導体装置とその製造方法

【課題】銅のワイヤを用いたボンディングに関し、効率の良い製造が可能な半導体装置とその製造方法を提供する。

【解決手段】基材2上に形成されている銅の電極パッド3と、前記電極パッド3を覆うように設けられている金の金属層4と、前記金属層4上にボンディングされている銅のワイヤ5とを有することを特徴としている。

(もっと読む)

半導体基板の処理方法及び半導体装置の製造方法

【課題】半導体基板の裏面研削後にスパッタリング法を含む方法で導電膜を形成する際に、研削時に半導体基板を支持体に固定する接着剤の基板外周部のはみ出した部分から放電現象の発生を防止する。

【解決手段】半導体基板1の裏面研削後、導電膜の成膜を実施する前に、基板端部E1と接着剤との隙間d1を所定値以上にするために、基板端部又は接着剤の少なくとも一方を除去する。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

多重膜のエッチング液組成物及びそのエッチング方法

【課題】Cu/Mo積層金属膜、Cu/Mo合金積層金属膜、Cu合金/Mo合金積層金属膜のような、銅又は銅合金の1層以上の銅層と、モリブデン又はモリブデン合金の1層以上のモリブデン層とを含む多重膜を、効率的で優秀に同時に一括してエッチングすることができるエッチング液組成物及びこれを用いた多重膜のエッチング方法を提供する。

【解決手段】エッチング液組成物は、総重量に対して、リン酸50〜80wt%;硝酸0.5〜10wt%;酢酸5〜30wt%;イミダゾール0.01〜5wt%;及び残量の水を含む。添加剤イミダゾールは、銅/モリブデンガルバニック反応調節剤として機能する。

(もっと読む)

61 - 80 / 759

[ Back to top ]