Fターム[5F033WW02]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 長さ、寸法 (1,572) | 厚さ (759)

Fターム[5F033WW02]に分類される特許

141 - 160 / 759

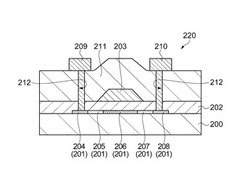

半導体装置ならびに半導体装置の製造方法

【課題】ヒロックに対して400℃程度の耐熱性を有するNd添加量2at%のAlNd層を塩素系ガスでプラズマエッチングする場合、フェンスと呼ばれる反応生成物が堆積した領域が生じる。フェンスの存在により、AlNd層をゲート電極としてTFTを形成した場合、ゲート電極脇に電気的に不安定な領域ができることから、TFTの電気的特性が不安定になる場合があるという課題がある。

【解決手段】AlNd層203を層厚0.45μm以上0.8μm以下、Ndの含有量を0.5at%以上1.0at%以下に形成した。この条件範囲であれば、塩素ガスを主としたプラズマエッチングを行ってもフェンスの発生が抑えられる。また、基板温度を500℃まで上げられることから、層間絶縁層211として信頼性が高い酸化シリコン層をAlNd層203にヒロックを発生させることなく形成することができ、信頼性が高いTFT220を提供することが可能となる。

(もっと読む)

Cu−Al合金粉末、それを用いた合金ペーストおよび電子部品

【課題】本発明は、配線や電極をペーストから焼成して製造する電子部品や、ガラス又はガラスセラミックス部材と接する配線を有する電子部品において、酸化による電気抵抗増大を抑制でき、あるいは、ガラス又はガラスセラミックスの気泡の発生を抑制可能で、マイグレーション耐性に優れたCu系配線材料を用いた電子部品を提供することを目的とする。

【解決手段】本発明は、ガラスまたはガラスセラミックス部材と接する配線・電極・コンタクト部材、あるいはガラスまたはガラスセラミックスと共にペーストを形成し焼成して成る配線・電極・コンタクト部材を有する電子部品であって、Cu及びAlを含む合金粉末粒子から構成され、かつ、Cu及びAlを含む合金粉末粒子の表面が80nm未満の酸化Al皮膜(Al2O3)で覆われていることを特徴とする。

(もっと読む)

反射電極、および反射電極を備えた表示デバイス

【課題】高い反射率および低い接触抵抗を有しており、しかも、ヒロックなどの欠陥を生じることのない耐熱性にも優れた反射電極を提供する。

【解決手段】基板1上に形成される表示デバイス用の反射電極2であって、前記反射電極は、0.05〜2原子%のNi及び/又はCo、並びに0.1〜2原子%のNdを含有する第1のAl−(Ni/Co)−Nd合金層2aとAlとO(酸素)を含有する第2のAl酸化物層2bと、を有している。上記Al酸化物層は透明画素電極3と直接接続しており、前記Al酸化物層中のO原子数とAl原子数との比である[O]/[Al]が、0.30以下であり、前記Al酸化物層の最も薄い部分の厚みが、10nm以下である。上記反射電極は、前記Al酸化物層と前記透明画素電極とが直接接続する領域において、前記透明画素電極と前記基板との間に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】下層金属膜上の絶縁性保護膜に貫通部を形成した後の残渣処理を簡単かつ確実に行い、下層金属膜の露出面を良好な状態に維持することによって上層金属膜の形成を確実に行うこと。

【解決手段】ウェハ表面の下層金属膜上に絶縁性保護膜を形成する。その絶縁性保護膜上にマスクを形成し、このマスクを用いて絶縁性保護膜を選択的に除去して下層金属膜の一部を露出させる。薬液によるウェット処理を行ってマスクを除去する。その後、その露出した下層金属膜の表面に存在する残渣を酸素系プラズマ処理により除去する。酸素系プラズマ処理によって下層金属膜の露出面にできたダメージを、水素系プラズマ処理を行って取り除く。そして、下層金属膜の露出面上に上層金属膜をメッキ等により積層する。

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 低誘電率で且つCFx、SiF4等のガスの発生がなく安定な半導体装置の層間絶縁膜とそれを備えた配線構造を提供する。

【解決手段】 下地層上に形成された絶縁膜を備えた層間絶縁膜において、前記層間絶縁膜は、実効誘電率が3以下である。配線構造は、層間絶縁膜と、層間絶縁膜に形成されたコンタクトホールと、前記コンタクトホール内に充填された金属とを備え、前記絶縁膜は、前記下地層上に形成され、表面が窒化されたフルオロカーボン膜を備えている。

(もっと読む)

半導体デバイスおよびその構造体の製造方法

【課題】集積回路の配線間に空隙を形成することにより、容量成分が低減された半導体装置の製造方法を提供する。

【解決手段】基板202上に第1の絶縁材が堆積され、この上に、犠牲部分を有する第2の絶縁材232が堆積される。上記第1および第2の絶縁層内に、導電線210がダマシン法により形成される。犠牲部分となる第1の絶縁材を除去するために第2の絶縁材が処理され開口部238が形成される。そして第1の絶縁材が除去されて、導電線間に空隙242が形成される。第2の絶縁材は、堆積時には不透過性であるが、処理後により透過性とし、これを介して犠牲部分を除去する。第2の絶縁材の処理はエッチングによる開口、あるいは熱感受性成分のアニールによる除去である。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の一端は、導通部106の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部106は、結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

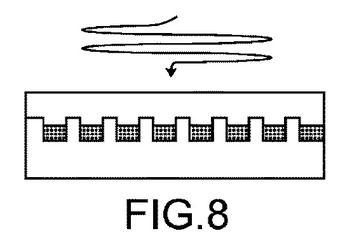

金属結晶領域、特に集積回路における金属結晶領域を生成する方法

本方法は、例えば相互接続ラインを形成するために、薄い結晶(8)のシートを、基板(1)のトレンチに堆積される、このシートと同一のタイプであるが、アモルファスであるか小さな粒径である金属(6)に固定することを含む。焼鈍しは、このラインにシートの結晶構造を徐々に与える。結晶(8)が除去されると、高度の導電結晶ラインが得られる。それは、その粒径が非常に拡大されているからである。金属は、銅、銀及びアルミニウムから選択される。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置の外部端子に加わる外力により外部端子下の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】シリコン基板1の主面s1上に形成された配線層のうちの最上の配線層MHは、アルミニウムからなる導体パターン3によって形成されたパッドPD1を有し、パッドPD1の下面には、下層から順に積層された第1バリア導体膜bm1および第2バリア導体膜bm2からなるバリア導体膜BMaが配置されている。最上の配線層MHの一つ下の第5配線層M5のうち、パッドPD1のプローブ接触領域PAと平面的に重なる領域には導体パターン3は配置されていない。また、第1バリア導体膜bm1はチタン、第2バリア導体膜bm2は窒化チタンをそれぞれ主体とする導体膜であり、第1バリア導体膜bm1の方が、第2バリア導体膜bm2よりも厚く形成されている。

(もっと読む)

貫通電極で貼り合わせた300mmウエハと半導体装置

【課題】ウエハを貫く貫通電極でウエハ上のデバイスを接続し、ウエハを貼り合わせて高集積で高機能の半導体装置を製造するとき、貫通電極とウエハを絶縁分離する工程とバンプを形成する工程、バンプを接続する工程があった。これらの工程を省きチップを積層した半導体装置の原価を低減することが課題であった。

【解決手段】ウエハを貫くリング状の孔にシリコン酸化膜を埋め込み、これの中の貫通電極を形成することでウエハと貫通電極を絶縁分離した。この方法で工程数が少なくなった。

(もっと読む)

半導体装置、半導体ウェハおよびその製造方法

【課題】バンプ電極を各チップ領域に形成した半導体ウェハを個々の半導体チップに個片化する際、個片化された半導体チップにクラックが発生することを抑制できる技術を提供する。

【解決手段】半導体ウェハWFの主面に接着テープATを貼り付けた状態で、半導体ウェハWFの裏面に溝DTを形成する。半導体ウェハWFの裏面に溝DTを形成するには、半導体ウェハWFの裏面にレジスト膜を塗布した後、フォトリソグラフィ技術を使用することにより、レジスト膜をパターニングする。レジスト膜のパターニングは、溝DTを形成する領域にレジスト膜が残らないように行なわれる。そして、パターニングしたレジスト膜をマスクにしたドライエッチング技術により、半導体ウェハWFの所定領域に溝DTを形成する。具体的に、ダイシングラインDLの近傍領域に溝DTを形成する。

(もっと読む)

配線層構造及びその製造方法

【課題】半導体基板又はガラス基板の下地基板に対する密着性が高く、下地基板への拡散バリア性に優れ、かつ水素プラズマ耐性に優れた低抵抗な配線層構造、及びその製造方法を提供する。

【解決手段】半導体又はガラス基板の下地基板1と、下地基板1上に形成された酸素含有Cu合金層2と、酸素含有Cu合金層2上に形成された、Al、Zr、Tiのうち少なくとも一種を含有する酸化物層3と、酸化物層3上に形成された、Al、Zr、Tiのうち少なくとも一種を含有するCu合金層4と、Cu合金層4上に形成された、Cu導電層5とを有する。

(もっと読む)

半導体デバイスの製造方法

【課題】薄型化されたウェハにめっき処理をする際にウェハ裏面への金属析出やウェハの反り及び損傷を抑制すると共に、ウェハのめっき処理効率が良好な半導体デバイスの製造方法を提供する。

【解決手段】ウェハを薄型化する工程1、薄型化された前記ウェハの裏面をダイシングテープでリングフレーム内にマウントする工程2、及び、前記リングフレーム内にマウントされた前記ウェハの表面にめっき処理を行う工程3を備えた半導体デバイスの製造方法。

(もっと読む)

配線部材、その製造方法及びそれを用いた電子部品

【課題】600℃〜700℃の高温であっても高い耐酸化性と低抵抗を両立し、かつ低コストで形成可能な配線材料を提供する。

【解決手段】基板上に形成される銅配線と、銅配線上に50nm以上200nm以下の膜厚で形成される50重量%以上のアルミニウムを含有する銅合金薄膜と、を具備する配線部材を用いる。上記銅配線の膜厚は、1μm以上50μm以下である。基板と銅配線の間には下地層が配置されている。配線部材の電気抵抗率は、4×10-6Ωcm以下である。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン・ゲート電極作成のためのエッチング処理時に、クランプによって覆われていたポリサイド層上の層間絶縁膜の膜剥がれが起こりにくい半導体装置の製造方法を提供する。

【解決手段】半導体基板110上に、ポリシリコン膜220及びタングステン・シリサイド膜210をこの順に積層してポリサイド・ゲート電極230を形成する。ポリサイド・ゲート電極230を含む半導体基板110上に、B濃度が高濃度の下層BPSG膜140を第1の成膜速度v1で形成する。下層BPSG膜140の上に、B濃度が下層BPSG膜140より低い低濃度の上層BPSG膜120を第2の成膜速度v2で形成する。第2の成膜速度は前記第1の成膜速度未満である。

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の表面に対するダメージを防ぎ、配線膜厚を均一に制御することにより、配線間ショート及び信頼性劣化を防止できるようにする。

【解決手段】半導体基板101の上に絶縁膜102を形成し、絶縁膜102の内部にイオン注入法によりイオン注入層103を形成し、絶縁膜102に少なくともイオン注入層103に達する深さの配線溝104を形成し、配線溝104に導電膜107Aを形成し、絶縁膜102及び導電膜107Aにおけるイオン注入層103よりも上に形成されている領域を除去する。

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETにおいては、アルミニウム系ソース電極下のアルミニウム拡散バリア・メタル膜として、チタンおよび窒化チタンからなるチタン系バリア・メタル膜が広く使用されている。しかし、本願発明者らが検討したところによると、チタン系バリア・メタル膜を使用すると、ウエハの反りが増大して、ウエハ・ハンドリングが困難となり、ウエハ割れやウエハ欠け等の問題が不可避となることが明らかとなった。この傾向は、最小寸法が0.35マクロ・メートル以下の製品において特に顕著である。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜(TiW等のタングステンを主要な成分とする合金膜)をスパッタリング成膜によって形成する際、スパッタリング成膜チャンバの気圧を1.2パスカル以下とするものである。

(もっと読む)

141 - 160 / 759

[ Back to top ]