Fターム[5F033WW03]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 温度 (833)

Fターム[5F033WW03]に分類される特許

161 - 180 / 833

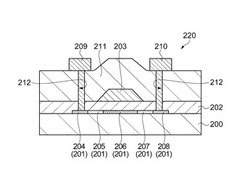

半導体装置ならびに半導体装置の製造方法

【課題】ヒロックに対して400℃程度の耐熱性を有するNd添加量2at%のAlNd層を塩素系ガスでプラズマエッチングする場合、フェンスと呼ばれる反応生成物が堆積した領域が生じる。フェンスの存在により、AlNd層をゲート電極としてTFTを形成した場合、ゲート電極脇に電気的に不安定な領域ができることから、TFTの電気的特性が不安定になる場合があるという課題がある。

【解決手段】AlNd層203を層厚0.45μm以上0.8μm以下、Ndの含有量を0.5at%以上1.0at%以下に形成した。この条件範囲であれば、塩素ガスを主としたプラズマエッチングを行ってもフェンスの発生が抑えられる。また、基板温度を500℃まで上げられることから、層間絶縁層211として信頼性が高い酸化シリコン層をAlNd層203にヒロックを発生させることなく形成することができ、信頼性が高いTFT220を提供することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の裏面側で貫通ビア回りに損傷や欠陥を生じないようにし、あるいは大幅に低減すること。

【解決手段】ビア・ラストにおいて、BEOLまで終えたシリコン基板10に対し、基板のおもて面に穴16を開け、穴16の内壁に絶縁膜18を形成し、穴16の中にビア導体24としてCuを電解めっき法により埋め込んでから、穴16の底部つまりCuビア導体24の底部が露出するまでシリコン基板10の裏面をウエットエッチングで削る。

(もっと読む)

半導体集積回路装置の製造方法

【課題】主にアルミニウム系通常配線を有するLSIの製造工程BEOLプロセスでは、配線の信頼性に関して、EM耐性およびSM耐性の向上が特に重要である。アルミニウム系配線に関する不良の中でも、配線メタル膜の膨張や欠けの発生は、EM耐性およびSM耐性を大きく劣化させる要因となる。

【解決手段】本願発明は、層間絶縁膜を成膜するプラズマCVDチャンバのウエハ・ステージ上に於いて、アルミニウム系配線メタル膜のパターニングの後であって層間絶縁膜の成膜前に、ウエハのデバイス面に対して、不活性ガスを主要な成分の一つとして含む雰囲気下、アルミニウム系配線メタル膜および層間絶縁膜の成膜温度よりも高いウエハ温度において、プラズマ・アニール処理を実行することにより、配線メタル層の側壁部の付着物が完全に除去され、膨張不良の原因が取り除かれ、更に、不動態化の進行、ストレス開放等により、欠け不良を抑制するものである。

(もっと読む)

半導体装置

【課題】レジストパターンの解像不良を引き起こす反応阻害物質を確実に除去することが可能なダマシン構造の半導体装置及びその製造方法の提供。

【解決手段】基板上に、少なくとも第1層間絶縁膜6及び低誘電率膜からなる第2層間絶縁膜4を有し、第2層間絶縁膜上に形成した第1レジストパターン1aを用いてビアホール9を形成し、アミン成分を含有する有機剥離液で有機剥離処理を行った後、続いて第2層間絶縁膜上に第2レジストパターン1bを形成する工程を含む半導体装置の製造方法であって、ウェット処理後、第2レジストパターン下層の第2反射防止膜2bを塗布する前に、アニール処理、プラズマ処理、UV処理又は有機溶媒処理の少なくとも一の処理を行い、露光時にレジスト中で発生する酸の触媒作用を阻害するアミン成分を除去して第2レジストパターン1bの解像度の劣化を防止する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】疎水化のために配線層間絶縁膜の表面に形成する層をできるだけ薄くし、且つ、Cu配線上に支障なくキャップメタルを成膜できるようにする。

【解決手段】配線層間絶縁膜(第1の配線層間絶縁膜3)に配線形成用溝(第1層配線形成用溝21)を形成する。配線形成用溝内にCu配線(第1層配線4)を形成し、Cu配線の構成材料のうち配線形成用溝以外の箇所に形成された部分を除去する。Cu配線上及び配線層間絶縁膜上にSi−O、C−O、Si−CH3、Si−H、Si−C及びC−Hのうちの少なくとも何れか1つの結合を含む絶縁膜層(第1の有機ポリマー層6)を形成する。Cu配線上の絶縁膜層を選択的に除去し、Cu配線上にキャップメタル(第1のキャップメタル5)を選択的に形成する。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

窒化銅膜の形成方法

【課題】最終的に得られる製造コストが高く且つ基板の大きさが制限される、従来のプラズマ処理による窒化銅膜の形成方法の課題を解消する。

【解決手段】窒素ガスとアンモニアガスとから成り、アンモニアガス濃度が0.8vol%以上の混合雰囲気内に設けられたヒータブロック18上に載置した基板10を、ヒータブロック18によって蟻酸銅の熱分解温度以上に加熱し、基板10の加熱温度で蒸発する溶媒中に蟻酸銅を溶解した原料供給槽22に貯留した蟻酸銅溶液を、基板10の所定面に向けて噴霧して、噴霧した蟻酸銅溶液中の溶媒を蒸発し且つ蟻酸銅を熱分解して、基板10の所定面に窒化銅膜を形成する。

(もっと読む)

ポロゲン、ポロゲン化された前駆体及び低誘電率をもつ多孔質有機シリカガラス膜を得るためにそれらを使用する方法

【課題】低い誘電率及び改良された機械的性質、熱的安定性及び化学的耐性を有する多孔質有機シリカガラス膜を提供する。

【解決手段】式SivOwCxHyFz(ここで、v+w+x+y+z=100%、vは10〜35原子%、wは10〜65原子%、xは5〜30原子%、yは10〜50原子%、及びzは0〜15原子%)で表わされる多孔質有機シリカガラス膜を製造する。オルガノシラン及びオルガノシロキサンからなる群より選ばれる前駆体並びにポロゲンを含むガス状試薬を真空チャンバに導入し、ガス状試薬にエネルギーを加え、ガス状試薬の反応を生じさせて基体上に予備的な膜を堆積させる。その予備的な膜は細孔を持ち、誘電率が2.6未満である多孔質膜を得るために、実質的にすべてのポロゲンを除去される。

(もっと読む)

配線形成方法

【課題】樹脂基板上に、接着層等を形成するための別の工程を加えることなく、基板との密着性の高い導電性配線を簡単に形成することができる配線形成方法を提供することを目的とする。

【解決手段】樹脂基板1上に、導電性微粒子を含有する分散溶液の塗布層3を形成する工程と、レーザ光6を塗布層3の特定領域に連続的に照射していくことで、導電性微細配線4を形成する工程と、導電性微細配線4以外の領域の材料を除去する工程とを備え、塗布層3の厚さをd、塗布層3の光吸収係数をα、レーザ光6の入射光強度をI0、樹脂基板1上に到達するレーザ光6の透過光強度をI1とするとき、以下の関係式から成り立つことを特徴とする。

log(I1/I0)=−αd

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 低誘電率で且つCFx、SiF4等のガスの発生がなく安定な半導体装置の層間絶縁膜とそれを備えた配線構造を提供する。

【解決手段】 下地層上に形成された絶縁膜を備えた層間絶縁膜において、前記層間絶縁膜は、実効誘電率が3以下である。配線構造は、層間絶縁膜と、層間絶縁膜に形成されたコンタクトホールと、前記コンタクトホール内に充填された金属とを備え、前記絶縁膜は、前記下地層上に形成され、表面が窒化されたフルオロカーボン膜を備えている。

(もっと読む)

半導体装置の製造方法

【課題】下層金属膜上の絶縁性保護膜に貫通部を形成した後の残渣処理を簡単かつ確実に行い、下層金属膜の露出面を良好な状態に維持することによって上層金属膜の形成を確実に行うこと。

【解決手段】ウェハ表面の下層金属膜上に絶縁性保護膜を形成する。その絶縁性保護膜上にマスクを形成し、このマスクを用いて絶縁性保護膜を選択的に除去して下層金属膜の一部を露出させる。薬液によるウェット処理を行ってマスクを除去する。その後、その露出した下層金属膜の表面に存在する残渣を酸素系プラズマ処理により除去する。酸素系プラズマ処理によって下層金属膜の露出面にできたダメージを、水素系プラズマ処理を行って取り除く。そして、下層金属膜の露出面上に上層金属膜をメッキ等により積層する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

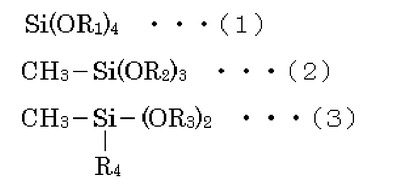

塗布型シリカ系被膜形成用組成物、この塗布型シリカ系被膜形成用組成物を用いたシリカ系被膜、及びそれを用いた半導体装置

【課題】 ゾル−ゲル法を用いて、硬化時の収縮率が小さく低誘電率である塗布型シリカ系被膜を得ることが可能な、塗布型シリカ系被膜形成用組成物を提供することを目的とする。

【解決手段】 下記一般式(1)、(2)及び(3)にて表される化合物を含む(A)成分を必須成分とし、200〜300℃での一段目硬化から、600℃の二段目硬化迄の膜収縮率が5%以下であり、二段目硬化温度が400℃の場合の、シリカ系被膜の比誘電率が2.5以下である、前記(A)成分の加水分解・重縮合反応を経て得られる塗布型シリカ系被膜形成用組成物。

[R1、R2、R3は炭素数1〜3の有機基を示し、同一でも異なっていてもよい。R4は炭素数6〜20の直鎖状アルキル基を示す。]

(もっと読む)

半導体デバイスおよびその構造体の製造方法

【課題】集積回路の配線間に空隙を形成することにより、容量成分が低減された半導体装置の製造方法を提供する。

【解決手段】基板202上に第1の絶縁材が堆積され、この上に、犠牲部分を有する第2の絶縁材232が堆積される。上記第1および第2の絶縁層内に、導電線210がダマシン法により形成される。犠牲部分となる第1の絶縁材を除去するために第2の絶縁材が処理され開口部238が形成される。そして第1の絶縁材が除去されて、導電線間に空隙242が形成される。第2の絶縁材は、堆積時には不透過性であるが、処理後により透過性とし、これを介して犠牲部分を除去する。第2の絶縁材の処理はエッチングによる開口、あるいは熱感受性成分のアニールによる除去である。

(もっと読む)

配線形成方法、半導体装置及び回路基板

【課題】 半導体装置や回路基板の配線において、バリア膜の拡散バリアとしての機能を確保しながら、バリア膜による配線抵抗の増大を抑制する

【解決手段】 インプリント法に用いるスタンパ13のパターン面をバリア膜形成化合物14で被覆し、スタンパ13のパターン面を、基板11上に塗布された樹脂膜12に押し当てつつ、バリア膜形成化合物14の分解・転写処理を行う。これにより、スタンパ13のパターン面のパターンにより樹脂膜12内に配線溝16が形成され、配線溝16に沿ってバリア膜17が形成される。その後、配線溝16内にバリア膜17を介して配線材料を埋め込み、配線18を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線抵抗の増加を抑えつつ、配線のエレクトロマイグレーション寿命、およびストレスマイグレーション寿命を向上させる。

【解決手段】半導体装置100は、基板102上に形成された層間絶縁膜104に形成された凹部に、高融点金属を含むバリアメタル膜106と、配線金属膜114を構成する銅および銅とは異なる不純物金属を含むシード合金膜ならびに銅を主成分として含むめっき金属膜とを形成し、シード合金膜およびめっき金属膜を、200℃以上、10分以下で熱処理する第1の熱処理工程と、第1の熱処理工程の後、凹部外部に露出しためっき金属膜、シード合金膜、およびバリアメタル膜106を除去する工程と、シード合金膜およびめっき金属膜を熱処理する第2の熱処理工程と、を含む。

(もっと読む)

銅要素の結晶構造を修正する方法

平坦面を伴う銅要素(II’)の結晶構造を修正する方法であって、a)大粒子を有し、且つ平坦面を含む銅標準(I’)を作る段階と、b)前記平坦面(14、16)の粗さを1nm未満の粗さまで低減する段階と、c)前記平坦面(14、16)を洗浄する段階と、d)前記2つの平坦面(14、16)を接触させる段階と、e)アニーリングする段階と、を含む。前記粗さは0.5nm以下である。この方法は更に、前記標準(I’)と前記要素(II’)とを分ける追加段階f)を含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板および該シリコン基板上に設けられた低誘電率膜と配線との積層構造からなる低誘電率膜配線積層構造部を備えた半導体装置において、低誘電率膜が剥離しにくいようにする。

【解決手段】 シリコン基板1の上面の周辺部を除く領域には低誘電率膜4と配線5との積層構造からなる低誘電率膜配線積層構造部3が設けられている。低誘電率膜配線積層構造部3の周側面は封止膜15によって覆われている。これにより、低誘電率膜4が剥離しにくい構造となっている。この場合、シリコン基板1の下面には、該下面をクラック等から保護するために、下層保護膜18が設けられている。

(もっと読む)

電子デバイス及びその製造方法、並びに電子機器

【課題】製造プロセスを増加させずに、信頼性が高く、かつ反射特性に優れる電子デバイスを提供する。

【解決手段】本発明に係る電子デバイス200は、基板1と、基板1上に形成され、少なくともMo系膜41と、その上層に形成されたAl系膜42とからなる導電性反射膜40とを備える。そして、導電性反射膜40のMo系膜41の表面荒さRaが5nm以下であり、Al系膜42の波長350nm〜550nmにおける反射率が85%以上である。

(もっと読む)

161 - 180 / 833

[ Back to top ]