Fターム[5F033WW03]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 温度 (833)

Fターム[5F033WW03]に分類される特許

141 - 160 / 833

半導体装置及び半導体装置の作製方法

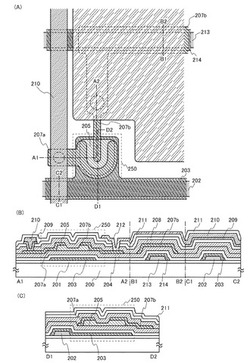

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

高温印刷部分と低温印刷部分の2つの部分を有する光起電力電池導体

半導体材料(1)上に少なくとも1つの導体を形成する方法は、(E1)−シルクスクリーン印刷によって第1の高温ペーストを堆積させるステップと、(E2)−前のステップの間に堆積された第1の高温ペーストに少なくとも部分的に重ねて、シルクスクリーン印刷によって、低温ペーストを堆積させるステップとを有する。 (もっと読む)

レジスト膜の除去方法および表示装置の製造方法

【課題】 CF4、CHF3、C2F6等の地球温暖化の一因となるガスを用いずに、レジスト膜を良好にアッシングするレジスト膜の除去方法、およびそれを用いた表示装置の製造方法を提供する。

【解決手段】 薄膜トランジスタ及び画素電極の上層側に成膜されたオーバーコート膜12から前記画素電極の少なくとも一部を露出させる際のマスクとして前記オーバーコート層12上にパターニングして形成されたレジスト膜28を、前記オーバーコート層12から前記画素電極の少なくとも一部を露出させた後にCOF2またはF2のいずれか一方と酸素ガスとを含む混合ガスを用いて除去する。

(もっと読む)

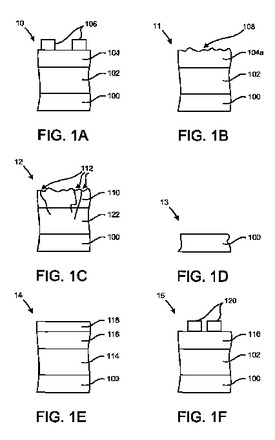

基板上のシリコン含有反射防止コーティング層の再加工方法

半導体デバイス製造においてシリコン含有反射防止コーティング(SiARC)層を有する膜構造を再加工する方法が供される。当該方法は、上にSiARC層を有する膜積層体を含む基板、及び、前記SiARC層上に形成されるレジストパターンを供する工程を有する。当該方法はさらに、前記SiARC層から前記レジストパターンを除去する工程、前記SiARC層を、オゾン(O3)気体を含む処理気体に曝露することで、前記SiARC層を改質する工程、希釈フッ化水素(DHF)液体によって前記の改質されたSiARC層を処理する工程、及び、遠心力により、前記基板から前記の改質されたSiARC層を除去する工程を有する。  (もっと読む)

(もっと読む)

回路基板の貫通電極の形成方法

【課題】基板上の微細な貫通孔へ貫通電極となる金属を充填する方法であって、基板への熱的影響を軽減することができ、且つ、効率的な製造を可能とする方法を提供する。

【解決手段】本発明は、貫通孔を有する基板の貫通孔に導電性金属を充填する貫通電極の形成方法であって、所定の純度及び粒径の金属粉と有機溶剤とからなる金属ペーストを用いるものである。このとき、金属ペーストに周波数60Hz〜100kHzの機械的振動を印加しながら基板に塗布し、金属ペーストの塗布と同時、又は、金属ペーストの塗布後に貫通孔を他端側から減圧して金属ペーストを貫通孔内に吸引し、その後金属ペーストを焼結して貫通電極とする。この金属ペーストの塗布は、機械的振動が印加されたブレードを基板と非接触な状態で移動させることが好ましい。

(もっと読む)

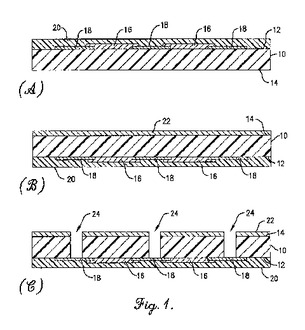

有機珪素化合物とヒドロキシル形成化合物との反応による液状シリカ層の形成

【課題】サブミクロン素子におけるギャップ充填層、プリメタル誘電体層、インターメタル誘電体層、浅いトレンチ分離誘電体層等として使用するための低誘電率を有する酸化珪素層を均一に堆積するための方法と装置とを提供する。

【解決手段】約400℃未満の基板温度での有機珪素化合物とヒドロキシル形成化合物との反応によって低比誘電体率を有する酸化珪素層を堆積する。これらの低誘電率薄膜は、残留炭素を含んでおり、サブミクロン素子におけるギャップ充填層、プリメタル誘電体層、インターメタル誘電体層および浅いトレンチ分離誘電体層のために有用である。堆積に先立って水あるいは有機化合物からヒドロキシル化合物を調製することができる。酸化珪素層は、約3.0未満の誘電率を有するギャップ充填層を与えるために有機珪素化合物から生成されたライナー層の上に約40℃未満の基板温度で堆積されることが好ましい。

(もっと読む)

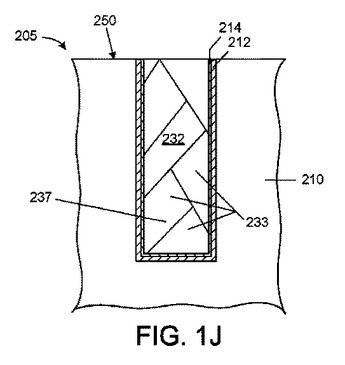

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】保護膜の亀裂や膜剥がれを防止する。

【解決手段】化合物半導体基板1上に少なくとも一層からなる下層配線2を形成し、化合物半導体基板1上に有機材料からなる層間膜3を堆積し、層間膜3上に金からなる上層配線5を形成し、層間膜3中に下層配線2と上層配線5とを接続するヴィア4を形成し、上層配線5の表面および層間膜3の表面の上にシリコン窒化膜からなる密着性向上用膜6を形成し、密着性向上用膜6上にシリコン酸化膜からなる熱膨張抑制膜7を形成し、熱膨張抑制膜7上にシリコン窒化膜からなる保護膜8を形成する。

(もっと読む)

Cu配線の形成方法

【課題】配線形成後に500℃以上の高温プロセスが存在する場合に適用可能なCu配線を形成すること。

【解決手段】500℃以上の温度の処理をともなう後工程が施されるCu配線の形成方法は、表面にトレンチおよび/またはホールを有する基板上の少なくともトレンチおよび/またはホールの底面と側面に、Cuの格子面間隔との差が10%以内の格子面間隔を有する金属からなる密着膜を形成する工程と、密着膜の上に前記トレンチおよび/またはホールを埋めるようにCu膜を形成する工程と、 Cu膜形成後の基板に350℃以上のアニール処理を行う工程と、Cu膜を研磨してCu膜のトレンチおよび/またはホールに対応する部分のみを残存させる工程と、研磨後のCu膜にキャップを形成してCu配線とする工程とを有する。

(もっと読む)

Cu系配線材料前駆体、Cu系配線材料およびこれらの形成方法

【課題】Cu-Ti系スパッタ膜を従来よりも低い温度で熱処理しても、配線表面にTi系自己拡散バリア膜を形成できるようにする。

【解決手段】極薄のTi系膜を第一の膜2として基材1上に形成した後、Ti系材料のTi系材料とCu系材料との傾斜構造を持つ複合膜を第二の膜3として形成し、その上にCu系電極となる第三の膜4を形成することにより、3層構造の前駆体を形成する。この前駆体を450℃以下で熱処理することで、Ti系バリア膜を有するCu系電極を形成することが可能となる。

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

背面処理中に前面側電気回路を保護するための耐傷性コーティング

マイクロエレクトロニクスメカニカルおよび半導体デバイス特徴の前面側を保護する、耐傷性コーティングを、その使用方法とともに提供する。上記コーティングは、非感光性で、除去可能であり、高い処理温度に耐える。また、これらのコーティングは、デバイス設計において、別個のエッチング停止層を不要とする。上記コーティングは、溶媒系に溶解または分散した成分を含有する組成物から形成される。上記成分は、スチレンアクリロニトリル共重合体および芳香族スルホンポリマーからなる群から選択される。  (もっと読む)

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、半導体層と例えばソース電極やドレイン電極を構成するAl系膜とを安定して直接接続させることが可能であるとともに、ウェットプロセスで用いる電解質液中で、半導体層とAl系膜との間でガルバニック腐食が生じにくく、Al系膜の剥離を抑制することのできる配線構造を提供する。

【解決手段】基板1の上に、基板1側から順に、薄膜トランジスタの半導体層4と、半導体層4と直接接続するAl合金膜6と、を備えた配線構造であって、半導体層4は酸化物半導体からなり、Al合金膜6は、Niおよび/またはCoを含む。

(もっと読む)

半導体装置の製造方法

【課題】 広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】 ガラス基板上に薄膜トランジスタ及び配線を有する半導体装置を製造する方法において、ガラス基板上に下地絶縁層を形成する工程と、前記下地絶縁層上に下地バリア層を形成する工程と、前記下地バリア層上にシード層を形成する工程と、前記シード層を前記配線に対応する形状にパターニングしてシード層パターンを形成する工程と、前記シード層パターンの表面に銅配線層を無電解めっき法で形成する工程と、前記銅配線層マスクとして前記下地バリア層をパターニングする工程と、前記銅配線層を被覆するように絶縁層を形成する工程とを備えたことを特徴する半導体装置の製造方法。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】基板側から順に、Al合金膜と、当該Al合金膜と直接接続する薄膜トランジスタの酸化物半導体層と、を有し、TiやMoなどの高融点金属を省略してAl合金膜を酸化物半導体層と直接接続しても低コンタクト抵抗を実現できる新規な表示装置用Al合金膜を有する配線構造を提供する。

【解決手段】上記配線構造において、半導体層は酸化物半導体からなり、Al合金膜は、Niおよび/またはCoを含むものである。

(もっと読む)

銅の選択的かつ清浄なエッチングのための集束イオンビームプロセス

集積回路編集のための銅の集束イオンビームエッチング用のエッチング促進剤はイオンビームによる隣接する誘電体の損失を防ぎ、隣接面上のスパッタされ再堆積した銅を非導電性にして電気的短絡を回避する。促進剤は分子中にN−N結合を有し、約70〜220℃の沸点を有し、ヒドラジン及び水の溶液と、ヒドラジン誘導体と、メチル、エチル、プロピル及びブチルから選択された2つの炭化水素基によって飽和したニトロソアミン誘導体と、ニトロソアミン関連化合物と、四酸化窒素とを含み、好適にはヒドラジン一水和物(HMH)、ヒドロキシエチルヒドラジン(HEH)、CEH、BocMH、BocMEH、NDMA、NDEA、NMEA、NMPA、NEPA、NDPA、NMBA、NEBA、NPYR、NPIP、NMOR及びカルムスチン単独、又は四酸化窒素との組合せである。促進剤は高アスペクト比(深さ)の孔の銅をエッチングするのに有効である。  (もっと読む)

(もっと読む)

カーボン・ナノチューブを選択的に成長させる方法

【課題】1つ以上のカーボン・ナノチューブを選択的に成長させる方法を提供する。

【解決手段】本方法は、上面を有する絶縁層を基板上に形成するステップと、絶縁層内にビアを形成するステップと、ビアの側壁及び底面を含め、絶縁層上に活性金属層を形成するステップと、ビアの内部での1つ以上のカーボン・ナノチューブの選択的な成長を可能にするために、イオン・ビームを用いて上面の部分にある活性金属層を除去するステップとを含む。

(もっと読む)

多孔質膜の前駆体組成物、多孔質膜及びその作製方法、並びに半導体装置

【課題】多孔質層間絶縁膜作製の際の多層化工程数を削減することができる前駆体組成物、この前駆体組成物を用いて得られた多孔質膜及びその作製方法、並びにこの多孔質膜を利用した半導体装置の提供。

【解決手段】式:Si(OR1)4の化合物(A)及び式:Ra(Si)(OR2)4−aの化合物(B)(上記式中、R1は1価の有機基を表し、Rは水素原子、又は1価の有機基を表し、R2は1価の有機基を表し、aは1〜3の整数であり、R、R1及びR2は同一であっても異なっていてもよい。)から選ばれた少なくとも1種の化合物と、250℃以上で熱分解する熱分解性有機化合物(D)と、90〜200℃の温度範囲内で熱分解し、そしてこの熱分解によりアミン類を発生する化合物であって、この熱分解温度以下では、この化合物の水溶液又はこの水溶液とアルコールとの混合溶液のpHが6.5〜8の範囲内に入る化合物(E)を含む。

(もっと読む)

半導体装置の製造方法。

【課題】 金属膜やHigh−k膜の膜質の劣化を抑制できる半導体装置の製造方法を提供すること。

【解決手段】 第1の薄膜2上に、第1の薄膜2とは異なる第2の薄膜3を形成し、第2の薄膜3上に、第2の薄膜3とは異なる膜からなる犠牲膜5を形成し、犠牲膜5をエッチングにより所望の間隔を持つパターンに加工し、犠牲膜パターンを形成し、シリコン含有プリカーサー、酸素含有ガスを基板上に間欠的に供給して、犠牲膜パターンにシリコン酸化膜6を被覆し、シリコン酸化膜6をエッチングにより犠牲膜5の側壁上に側壁スペーサー6aを形成し、犠牲膜5を除去し、側壁スペーサー6aをマスクとして用いて第1の薄膜2および第2の薄膜3を加工する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

141 - 160 / 833

[ Back to top ]