Fターム[5F033XX04]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 微細化 (1,181) | 高アスペクト化 (211)

Fターム[5F033XX04]に分類される特許

161 - 180 / 211

無電解フェーズと電流供給フェーズとを含むウェット化学堆積によりパターニングされた絶縁体上の金属層

無電解堆積および電気堆積プロセスをインサイチュで実行することによって、非常に信頼性のあるメタライゼーションが供給され、その際に、シード層を形成する、従来の化学気相堆積(CVD)、原子層堆積(ALD)ならびに物理気相堆積(PVD)技術にみられるような、汚染物質ならびにデバイススケーリングに関する欠点を克服することができる。ある実施例では、バリア層はさらに、ウェット堆積プロセスに基づいて堆積される。  (もっと読む)

(もっと読む)

半導体ウェハへの貫通孔配線の形成方法

【課題】高アスペクト比の貫通孔の内側へ貫通孔配線となる金属部を形成する電気メッキ工程におけるメッキ時間を短縮可能な半導体ウェハへの貫通孔配線の形成方法を提供する。

【解決手段】半導体ウェハ20aの一表面の開口径が他表面の開口径に比べて大きなテーパ状の貫通孔22をドライエッチングにより形成し(図1(d))、半導体ウェハ20aの一表面側および他表面側および貫通孔22の内周面に絶縁層23を形成し(図1(e))、半導体ウェハ20aの他表面側で絶縁層23の表面に金属薄膜43を形成し(図1(f))、半導体ウェハ20aの他表面側において貫通孔22を閉塞する導電体部45を形成し(図1(g))、半導体ウェハ20aの一表面側に陽極を対向配置し導電体部45を陰極として貫通孔配線24となる金属部24aを電気メッキにて陰極における貫通孔22側の露出表面から半導体ウェハ20aの厚み方向に沿って析出させる(図1(h))。

(もっと読む)

成膜方法及び成膜装置

【課題】例えアスペクト比が高く、深さが深いビアホール等の凹部にあっても、銅等の金属材料を、内部にボイドを発生させることなく、凹部内に高速かつ確実に埋込むことができるようにする。

【解決手段】凹部202を有し該凹部202の内部を含む表面に通電層206を形成した基板Wを用意し、凹部202の内部を除く通電層206の表面に電着法で高分子絶縁膜208を形成し、高分子絶縁膜208を形成した基板Wの表面に電解めっきを行って凹部202内に金属材料210を埋込む。

(もっと読む)

半導体装置の製造方法

【課題】下層導電体と上層導電体とを接続する低抵抗のコンタクトを安定して形成する。

【解決手段】コンタクト孔17が形成されたシリコン酸化膜15上にチタン膜19を形成し、当該状態でコンタクト孔17の底部に露出したポリシリコンプラグ13の表面の自然酸化膜18をスパッタエッチングにより除去する。このとき、シリコン絶縁膜15の上面はチタン膜19で被覆されているためシリコン酸化膜15のスパッタエッチングが防止される。したがって、コンタクト孔17底部にスパッタエッチされたシリコン酸化膜が再付着することが防止され、低抵抗で抵抗ばらつきの小さいコンタクトを安定して製造することが可能となる。

(もっと読む)

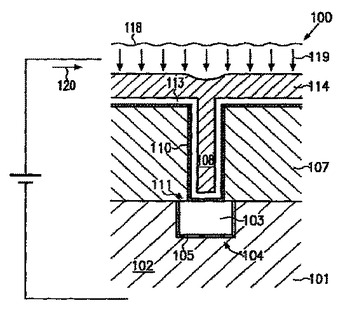

ゲートに近接したコンタクト・ホールを有する半導体トランジスタ

【課題】 デバイス密度を増加させるために、S/Dコンタクト・ホールが、トランジスタ構造体のゲートに近接して形成されるが、ゲートから電気的に絶縁された、トランジスタ構造体(及びその製造方法)を提供すること。

【解決手段】 構造体、及びその製造方法である。この構造体は、(a)第1のS/D領域と第2のS/D領域との間に配置されたチャネル領域と、(b)チャネル領域上のゲート誘電体領域と、(c)ゲート誘電体領域上にあり、かつ、ゲート誘電体領域によりチャネル領域から電気的に絶縁されたゲート領域と、(d)ゲート領域上の保護アンブレラ領域であって、保護アンブレラ領域は第1の誘電体材料を含み、ゲート領域が完全に保護アンブレラ領域の影の中にある、保護アンブレラ領域と、(e)(i)第2のS/D領域の真上にあり、これと電気的に接続され、かつ、(ii)保護アンブレラ領域のエッジと位置合わせされた充填されたコンタクト・ホールであって、コンタクト・ホールは、第1の誘電体材料とは異なる第2の誘電体材料を含む層間誘電体(ILD)層によってゲート領域から物理的に分離された充填されたコンタクト・ホールと、を含む。

(もっと読む)

炭素含有膜エッチング方法及びこれを利用した半導体素子の製造方法

【課題】炭素含有膜エッチング方法及びこれを利用した半導体素子の製造方法を提供する。

【解決手段】炭素含有膜上に炭素含有膜の上面を一部露出させるマスクパターンを形成し、マスクパターンをエッチングマスクとして利用して、O2、及びSi含有ガスからなる混合ガスのプラズマによって炭素含有膜を異方性エッチングする炭素含有膜エッチング方法である。これにより、高密度セルアレイ領域で互いに隣接した2個のコンタクトホールの間隔が数十nmまたはそれ以下のレベルに小さくなっても、コンタクトホールが互いに良好に分離して隣接した単位セル間の短絡が防止される。

(もっと読む)

半導体装置及びその製造方法

【課題】 信頼性及び歩留りの低下を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 バイアホール18が形成された半導体基板11と、半導体基板11の表面上に形成された絶縁膜13と、絶縁膜13、バイアホール18の内壁及び半導体基板11の表面上に形成されたスパッタ金属層14と、絶縁膜13上のスパッタ金属層14を除くスパッタ金属層14上に形成された第1のメッキ層15と、第1のメッキ層15及びスパッタ金属層14上に形成された第2のメッキ層16とを備える。

(もっと読む)

配線基板のメッキ膜形成方法

【課題】絶縁層に形成された高アスペクト比の溝やビア孔に電気銅メッキを行うとき、メッキ層中でのボイド(空孔)発生が抑制された配線層やビアの形成を可能とする。

【解決手段】溝やビア孔の底面部に、電気メッキを促進する添加剤を含む膜を選択的に形成してから、電気銅メッキを行う。この底面部のメッキ促進添加剤含有膜は、メッキ促進添加剤を含む溶液に、メッキ形成用の開口基板を浸漬しつつ脱気して開口部内の気泡を除去した後、スピン・リンス法と乾燥処理を行って形成する。

(もっと読む)

誘電性材料に狭いトレンチを形成する方法

【課題】半導体装置内に非常に小さいトレンチを形成する方法を提供する。

【解決手段】これら小さいトレンチの形成は、第1誘電体層の特性を局部的に化学的に変換することに基づいており、前記第1誘電体層内のパターニングされた穴の側壁が局部的に変化させられ、第1エッチング物質によりエッチング可能となる。その後、パターニングされた構造内に第2誘電体層が積層され、小さいトレンチが得られるように第1誘電体材料のダメージを受けた部分が除去される。誘電体層の特性を化学的に変化させることにより得られた小さなトレンチは、(10−30nm単位の)非常に小さいトレンチ内でのバリアーの積層、銅メッキ及びシード層の積層の研究をするための試験手段として用いることができる。

(もっと読む)

ドライエッチング方法

【課題】 ハードマスクで形成されたアルミニウム(Al)を含有する金属膜をプラズマエッチングする場合において、サイドエッチングを抑制し異方性形状を得ることができるエッチング方法を提供する。

【解決手段】 エッチングガスに、三塩化ホウ素(BCl3)、塩素(Cl2)、メタン(CH4)、エチレン(C2H4)、アルゴン(Ar)の混合ガス、もしくは三塩化ホウ素(BCl3)、塩素(Cl2)、メタン(CH4)、アセチレン(C2H2)、アルゴン(Ar)の混合ガスを用いることにより、サイドエッチング無く異方性形状、低パーティクルを提供する。

(もっと読む)

基材表面を金属でコーティングするための電気めっき用組成物

【課題】本発明は、特に集積回路の配線の製造において銅拡散防止層をコーティングするための、電気めっき用組成物に関する。

【解決手段】

本発明によれば、本組成物は、溶媒中の溶液に、0.4〜40mMの濃度の銅イオン源と;1級脂肪族アミン、2級脂肪族アミン、3級脂肪族アミン、芳香族アミン、窒素複素環化合物およびオキシムからなる群から選択される少なくとも1種の銅錯化剤とを含み;

銅/錯化剤のモル比は0.1〜2.5、好ましくは0.3〜1.3であり;かつ、

上記組成物のpHが7未満、好ましくは3.5〜6.5であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

多層回路基板又はウエハーに設けられた貫通孔又は非貫通孔に充填材を充填する方法

【課題】 多層回路基板又はウエハーにおいて、孔径25ミクロン以下、アスペクト比5以上の微細孔でも完全に液状粘性材料又は低融点合金の溶融物を充填できる方法である。

【解決手段】 多層回路基板又はウエハーに設けられた貫通孔又は非貫通孔に充填材を充填する方法であって、前記充填材を真空雰囲気下で前記多層回路基板又はウエハー上に孔版印刷した後、雰囲気を大気圧又は大気圧を超える圧力にして差圧充填すると共に、孔版印刷過程及び差圧充填過程を通じて前記多層回路基板又はウエハーに超音波振動を与える。充填材としては液状粘性材料、低融点合金粉末、又は低融点合金溶融物などが挙げられる。

(もっと読む)

開口不良の評価方法及び半導体装置の製造方法

【課題】 製品不良の原因となる開口不良を感度よく検出することが可能な、開口不良の評価方法及び半導体装置の製造方法を提供する。

【解決手段】 本発明は、半導体基板1上に設けられた第1の絶縁膜2に形成され、かつ少なくとも1つの接続孔を有する接続孔パターンの開口不良を評価する方法であって、接続孔パターンを半導体基板1に転写する転写工程と、転写工程後に第1の絶縁膜2を除去する除去工程と、転写工程にて接続孔パターンが転写された場合に、開口不良がない正常接続孔3であると判定する一方、接続孔パターンが転写されない場合には、開口不良が生じた不良接続孔4である判定する判定工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 アスペクト比の高い微細コンタクトホールを容易に制御性良く形成することができる半導体装置の製造方法を提供する。

【解決手段】 本発明は、絶縁膜に開孔を形成する半導体装置の製造方法であって、基体上に絶縁膜を形成する工程と、絶縁膜上にエッチングマスクとなる第1のエッチングマスク膜を形成する工程と、第1のエッチングマスク膜に開口を形成する工程と、該開口を用いて、絶縁膜に第1の異方性エッチングにより絶縁膜の膜厚よりも浅い第1の開孔を形成する工程と、第1のエッチングマスク膜を除去する工程と、絶縁膜上に第2のエッチングマスク膜を、前記第1の開孔の開口部を塞がないようにエッチングマスクとなるエッチングマスク膜を形成し、開口部に自己整合的に開口を形成する工程と、第2の異方性エッチングにより、第1の開孔の下部に第2の開孔を形成することにより開孔を形成することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 拡散防止機能を高めることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に形成された酸素を含有する絶縁体の表面上に、銅以外に少なくとも2種類の金属元素を含む銅合金皮膜を形成する。(b)銅合金皮膜上に、純銅または銅合金からなる金属膜を形成する。(c)工程aまたは工程bの後に、絶縁体中の酸素と銅合金皮膜中の金属元素とが反応して絶縁体の表面に金属酸化物膜が形成される条件で熱処理を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】 1.5以上の高アスペクト比である微細ホールに対しても、金属配線膜を埋め込むことができるように、ホールへの金属配線膜の埋め込み性を従来よりも向上させる。

【解決手段】 TiN膜の成膜工程63で、スパッタにより、ホールの内壁に沿ってTiN膜を成膜する。このとき、成膜温度を、従来よりも低温の150℃とすることで、アモルファス構造のTiN膜を形成する。その後、スパッタ工程64、65で、アモルファス構造のTiN膜の表面上にAl合金膜を形成することで、TiN膜を下地とした状態で、Al合金膜をコンタクトホールの内部に埋め込む。このように、Al合金膜の下地となるTiN膜をアモルファス構造にすることで、TiN膜の表面エネルギーを大きくし、TiN膜のAl合金膜に対する濡れ性を従来よりも向上させることができ、ホールへのAl合金膜の埋め込み性を従来よりも向上させることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】 本発明は、シロキサン結合を含む絶縁層を選択的にエッチングする技術について提供することを課題とする。また、本発明は、エッチングの際に生じる不具合に起因した動作不良等の低減された半導体装置を提供することを課題とする。

【解決手段】 本発明の一は、半導体層と導電層との上に設けられ、シロキサン結合を含む絶縁層を、絶縁層の上に設けられた感光性樹脂をマスクとし、臭化水素ガスと酸素ガスとを含む処理用ガスを用いて絶縁層をエッチングする工程を含むことを特徴とする半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】 所望の形状を有するホールを的確に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 下地領域11上に、下層有機絶縁膜12を形成する工程と、下層有機絶縁膜上に無機絶縁膜13を形成する工程と、無機絶縁膜上に上層有機絶縁膜14を形成する工程と、上層有機絶縁膜を貫通する第1の貫通部分及び無機絶縁膜を貫通する第2の貫通部分を有する第1のホール23を形成する工程と、酸素ガス及び窒素ガスの少なくとも一方を含んだエッチングガスを用いて上層有機絶縁膜及び第1のホール下の下層有機絶縁膜に対してドライエッチングを行い、第2の貫通部分及び下層有機絶縁膜を貫通する第3の貫通部分を有する第2のホールを形成するとともに、上層有機絶縁膜を除去する工程とを備え、ドライエッチングは、ドライエッチングが行われるチャンバー内におけるエッチングガスのレジデンスタイムが0.25秒以上となる条件で行われる。

(もっと読む)

電気的接続構造、その製造方法および半導体集積回路装置

【課題】 低抵抗の電気的接続構造を提供する。

【解決手段】 導電体に炭素細長構造体が電気的に接続された電気的接続構造において、導電体上に、導電性触媒担持体層と炭素細長構造体を生成するための触媒微粒子層と炭素細長構造体とを順次積層して、電気的接続構造を得る。

(もっと読む)

161 - 180 / 211

[ Back to top ]