Fターム[5F033XX04]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 微細化 (1,181) | 高アスペクト化 (211)

Fターム[5F033XX04]に分類される特許

201 - 211 / 211

バリア膜の形成方法

【課題】低温プロセスで、アスペクト比の高い微細なホール、トレンチ等の上部でオーバーハングが発生することなく、カバレージ良くZrB2膜等のバリア膜を形成する方法の提供。

【解決手段】基板を50〜450℃に加熱し、Zr(BH4)4ガスを0.1〜10秒の間、0.5〜200sccmの流量で導入し、真空チャンバー内の圧力がZr(BH4)4の導入時の圧力に比べ1/5以下になった時点で原料の吸着工程を終了し、チャンバー内へ触媒室で励起されたH2ガス及び/又はNH3ガスからなる反応ガスを0.1〜10秒の間、20〜1000sccmの流量で導入し、チャンバー内の圧力が、反応ガス導入時の圧力に比べ1/5以下になった時点で反応工程を終了させて、バリア膜を得る。

(もっと読む)

半導体装置及びその製造方法

【課題】 配線及びコンタクトを微細化しながら活性領域の増大を抑制して、配線と活性領域とのコンタクトを良好に保つ。

【解決手段】 半導体装置では、配線M1乃至M3がY方向に平行して設けられ、配線直下に活性領域SDGが設けられ、配線M2が第1のコンタクトC1及び第2のコンタクトC2を介して活性領域SDGと接続されている。第1のコンタクトC1は、配線M2よりも幅の広い活性領域SDG内に、第1のコンタクトと活性領域との余裕Zだけ内側に設けられ、開口部にコンタクトプラグ6が埋設されている。配線M2内に設けられた第2のコンタクトC2は、第1のコンタクトC1上に第1のコンタクトC1と接して設けられ、X方向の寸法X1が第1のコンタクトC1及び配線M2よりも第2のコンタクトと配線の余裕Wの2倍分だけ小さく、且つY方向の寸法Y1が第1のコンタクトC1よりも大きく、活性領域SDGの外側まで設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ドライエッチングにより半導体基板やポリシリコン層に生じるダメージ層を効果的に除去して、寄生抵抗や接合リークが低減された半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板上に絶縁膜を形成する工程と、前記絶縁膜を、ドライ工程によりエッチングする工程と、前記エッチングにより前記半導体基板上に生じたダメージ層を、熱分解した原子状の水素により、所定の温度下で除去する工程とを含む。

(もっと読む)

薄膜の加熱処理方法

【課題】 ランプアニールにより効果的に被処理膜を加熱処理するための方法を提供する。

【解決手段】 基板101の上面側からは紫外光ランプ104を用いて紫外光107が照射される。また、基板101の下面側からは赤外光ランプ108を用いて赤外光111が照射される。本発明では赤外光照射による振動励起効果に加えて紫外光照射による電子励起効果が付加されるため、被処理膜103の励起効率が大幅に高まり、効果的な加熱処理が可能となる。

(もっと読む)

素性構造及びウエハの均一な被覆率のため、磁場エンベロープの移動を伴う強くイオン化されたPVD

本発明は半導体ウエハのイオン化PVDプロセスに関し、単一プロセスチャンバ内の高い均一性の堆積−エッチングプロセスシーケンス及び高アスペクト比形状の被覆能力用状態を供する。プラズマは誘起結合プラズマ供給源で発生維持される。堆積プロセス段階は金属蒸気のPVD供給源のターゲットから発生中に行われる。ターゲット表面での位置やスパッタリング効率は磁場エンベロープの移動や掃引を生じて磁石の束の移動で増大する。ターゲットはDC供給源から電圧を印加されてスパッタリングされた原子の効率的熱運動化用の有効圧力が堆積中チャンバ内で保持される。ウエハ上での一様な厚さは各磁石の掃引サイクルで形成される。全ターゲット表面に亘る環状の掃引運動を用いた磁場の局在化は、合理的堆積率、高ターゲット利用率、金属原子の高イオン化、一様平坦領域堆積及びエッチング用状態、ウエハ中心及び端でHAR形状の被覆率に略同一な状態を生じる。  (もっと読む)

(もっと読む)

シリコンゲルマニウム犠牲層を用いた半導体素子の微細パターンの形成方法及びそのパターンの形成方法を用いた自己整列コンタクトの形成方法

【課題】 シリコンゲルマニウム犠牲層を使用して半導体素子の微細パターンを形成する方法、及びそれを用いた自己整列コンタクトを形成する方法を提供する。

【解決手段】 基板上に導電性物質膜、ハードマスク膜及び側壁スペーサを含む導電ライン構造物を形成し、基板の全面に少なくとも導電ライン構造物の高さと同じであるか、またはそれ以上の高さにシリコンゲルマニウム(Si1−XGeX)犠牲層を形成し、犠牲層上にコンタクトホールを限定するフォトレジストパターンを形成した後、犠牲層を乾式エッチングすることで基板を露出させるコンタクトホールを形成し、ポリシリコンを使用してコンタクトホールを埋め込む複数のコンタクトを形成した後に残留する犠牲層を湿式エッチングした後、その領域にシリコン酸化物を満たして第1層間絶縁層を形成する半導体素子の自己整列コンタクトの形成方法。

(もっと読む)

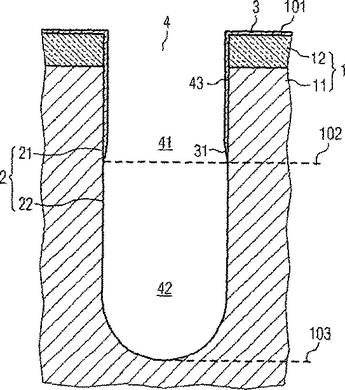

インコンフォーマルな堆積を用いて半導体プロセス技術において基板を垂直にパターニングする方法

典型的には半導体ウェーハである基板(1)の、レリーフ状にパターニングされた基板表面(101)上に、堆積方法(ADL;atomic layer deposition:原子層堆積)を用いて、基板表面(101)に対して傾斜し、および/または垂直である処理表面(2)に、被覆層(3)が提供される。被覆層(3)は、前駆材料の少なくとも1つの処理量の制限によって、および/または堆積方法の時間的制限によって、簡易な方法において、基板表面(101)に対して垂直な方向にパターニングされ、後続のプロセス工程のための機能層あるいはマスクとして形成される。  (もっと読む)

(もっと読む)

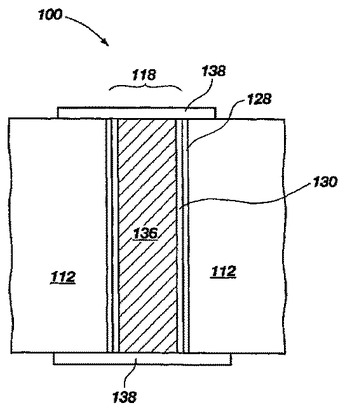

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

多層配線構造の製造方法

【課題】バリアメタル膜の表面に形成される自然酸化膜の膜厚を薄くし、ボイドの発生を防止した多層配線構造の製造方法を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法において、絶縁層に孔部4を形成する工程と、少なくとも孔部の内壁を覆うように、タンタルと窒素を主成分とするバリアメタル膜5を形成する工程と、バリアメタル膜の表面に形成された酸化膜6を除去する工程と、銅を含むめっき液にバリアメタル膜を浸漬してバリアメタル膜上に無電解銅めっき膜7を形成する工程とを含み、バリアメタル膜に含まれる窒素とタンタルの元素組成比(N/Ta)を、0.3以上で、かつ1.5以下とする。

(もっと読む)

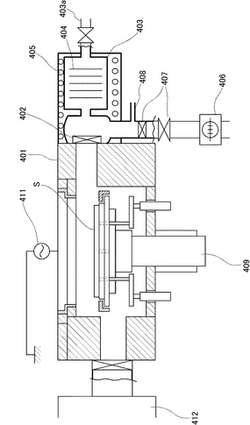

配線構造並びにその形成方法及び装置

【課題】 凹部への埋め込み性が良好で、長期に亘り安定した良好な電気的特性を得ることができ、さらに作製工程を可及的に低減し得る配線構造を提供する。

【解決手段】 Cu板と基板3との温度及び温度差を所定通りに制御しつつ、原料ガスであるCl2 ガスのプラズマによりCu板をエッチングすることによりCu成分とCl2 ガスとの前駆体であるCuClを形成し、この前駆体が基板3に吸着され、その後Cu成分を析出させることによりCuの薄膜を形成する成膜反応と、この成膜反応により形成されたCu膜をCl2 ガスのプラズマでエッチングするエッチング反応とを共存させるとともに、前記成膜反応の速度が前記エッチング反応の速度よりも大きくなるように制御することにより前記凹部3aにその底部から順にCu膜を積層してこの凹部3aにCuを埋め込んだ。

(もっと読む)

多層配線構造の製造方法及びその構造

【課題】 上層配線層と下層配線層とを、アスペクト比の高いビアコンタクトで接続した多層配線構造を提供する。

【解決手段】 多層配線構造のビアコンタクト形成工程が、ビアホールの底面上に触媒層を設け、触媒層上にビアホールの上方に向ってめっき金属層を成長させ、めっき金属層でビアホールを充填する無電解めっき工程からなる。

(もっと読む)

201 - 211 / 211

[ Back to top ]