Fターム[5F033XX36]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 配線修理 (121)

Fターム[5F033XX36]に分類される特許

1 - 20 / 121

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

装置、方法、およびリボン

【課題】フラットパネル修復に、検査切断修復結合ツール及び独立体積修復ツールの2種類が必要である

【解決手段】装置は、統合された検査機能と、材料除去機能と、材料堆積機能とを備え、検査動作、材料除去動作、及び材料堆積動作を同じ光軸に沿って実行する。装置は、部分的に、カメラと、一対のレンズと、1つ又は複数のレーザとを備える。第1のレンズは、検査を受けているターゲット基板上に形成される構造上に光軸に沿ってカメラを合焦させるために使用される。第1のレンズは、検査された構造が材料除去を必要としていると識別される場合、構造上にレーザビームを合焦させて、その構造上に存在する材料を除去するためにも使用される。第2のレンズは、検査された構造が材料堆積を必要としていると識別される場合、レーザビームをリボン上に合焦させて、リボンに形成された埋め込みウェルから流動的複合物を構造に転写するために使用される。

(もっと読む)

偏在率算出方法、半導体装置の製造方法及びプログラム

【課題】レイアウトデータからCu残が発生しやすい品種やレイヤであるか否かを判定することのできる偏在率算出方法を提供する。

【解決手段】CPUは、検証レイヤにおいて所定サイズの検証エリア毎にパターン密度を算出するステップS13と、算出されたパターン密度を複数の密度範囲に分別し、各々の密度範囲に属するパターン密度の分布を示す複数の密度マップMAP0〜MAP7を生成するステップS14とを実行する。また、CPUは、各密度マップMAP0〜MAP7に所定量のプラスシフトを加えるステップS15と、パターン密度の密度差が第1基準値以上となる組み合わせの密度マップMAP0〜MAP7を重ね合わせ、両密度マップで重複した領域を抽出するステップS16とを実行する。CPUは、その抽出した領域の総面積を算出するステップS17と、算出した総面積と第2基準値とを比較するステップS18とを実行する。

(もっと読む)

パターン修正方法

【課題】配線パターンの修正において、修正抵抗を低減することが可能となる、パターン修正方法を提供する。

【解決手段】パターン修正方法は、導電性パターン20の欠陥部21を修正するパターン修正方法であって、導電性インクを塗布することにより第1のインク層31を形成する工程と、第1のインク層31を焼成することにより第1の修正層32を形成する工程と、少なくとも一部が第1の修正層32に重なるように導電性インクを塗布することにより、第2のインク層33を形成する工程と、第2のインク層33を焼成することにより第2の修正層34を形成する工程とを備え、第1の修正層32および第2の修正層34により欠陥部21を挟んで配置される導電性パターン20間の電気的接続が確保される。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

半導体装置のコントラスト画像処理方法、処理装置、及び、処理プログラム

【課題】半導体装置の電位コントラスト像から配線のコントラストを簡便かつ正確に認識し、抽出することのできる半導体装置のコントラスト画像処理方法、処理装置、処理プログラムを提供する。

【解決手段】解析装置から得られた半導体装置のコントラスト像をコントラスト像に合わせて自動的に減色する減色処理と、減色されたコントラスト像に含まれる画素をあらかじめ設定したコントラスト閾値を基準に分類し、複数のコントラストに分別された配線パターンを抽出する配線コントラスト抽出処理と、配線パターンの輪郭部分に含まれるノイズを輪郭部分のシフトにより除去するシフト処理と、を含み、解析装置から得られた半導体装置のコントラスト像に含まれる配線パターンを所定のコントラストに区分して抽出する。

(もっと読む)

電子素子の製造方法および電子素子

【課題】有機絶縁層を有する電子素子の配線短絡を簡素な工程により絶縁することが可能な電子素子の製造方法および電子素子を提供する。

【解決手段】配線層21,22の上に有機絶縁層12を形成したのち、配線層21,22の短絡部23に、有機絶縁層12に対して透過性を持つ波長のレーザ光LBを有機絶縁層12を介して照射、または基板11に対して透過性を持つ波長のレーザ光LBを基板11を介して照射する。レーザ照射領域24では短絡部23が消失して、配線層21と配線層22との間の絶縁が回復する。短絡部23の上下に接する有機絶縁層12または基板11は残されている一方、レーザ照射領域24(短絡部23が消失した部分)には空洞25が生じる。

(もっと読む)

半導体装置の製造方法

【課題】複数の顧客による各々異なるLSIが共同で作製された基板を、守秘性が得られた状態で各々の顧客に提供できるようにする。

【解決手段】特定の顧客への提供対象とするLSIチップ領域331以外の領域が開放した開口部307aを備えるマスクパターン307を形成する。次に、マスクパターン307をマスクとし、開口部307に露出しているLSIチップ領域332をエッチング除去し、ブラインド領域301aを形成する。ブラインド領域301aの形成では、第1配線層302,第2配線層303,および第3配線層304を除去し、これらの下層の一部までを除去する。

(もっと読む)

基板の配線修正方法、基板の配線修正装置及び基板の配線形成装置

【課題】 プリント配線基板等の基板上に描画済の配線パターンの変更を簡易に行ない、生産性を向上すること。

【解決手段】 基板10上に描画済の既設配線を修正する基板10の配線修正装置100であって、第1の既設配線11を設定された切断位置においてレーザにより切断するレーザ切断装置140と、第1の既設配線11における接続予定部と第2の既設配線12における接続予定部とをつなぐ再配線30を描画する配線用インクジェット塗布装置150を有するもの。

(もっと読む)

回路基板の欠陥修正方法、回路基板及び半導体装置

【課題】高密度で微細なパターンの断線を低温プロセスによって修正可能な回路基板の欠陥修正方法を提供する。

【解決手段】基板1上に形成された配線3の断線箇所Dを含む基板1の露出面領域に、光照射によって濡れ性が変化する物質を用いた濡れ性調整層5を成膜する。次の第2工程では、濡れ性調整層5における断線個所Dに対応する部分、またはそれ以外の部分に光を照射する。これにより濡れ性調整層5における断線個所に対応する部分の電極形成液に対する濡れ性を、それ以外の部分よりも高くする。その後断線個所Dに対応する濡れ性調整層5部分上に電極形成液を供給して乾燥させる。これにより、断線個所Dに電極形成液を乾燥させた修正電極パターン7を形成する。

(もっと読む)

回路基板の欠陥修正方法、回路基板及び半導体装置

【課題】低温で処理できる印刷法を用いて、配線の断線による欠陥を修正する場合に、欠陥修正用の導電性材料が不要な部分まで広がることを防止することができる技術を提供する。

【解決手段】本発明に係る回路基板の欠陥修正方法は、基板20上に形成された3本の配線21,22,23のうち、配線22のパターンに生じた断線箇所24の周辺に絶縁性材料を用いてバンク25を形成する工程と、そのバンク25を形成した後で断線箇所24に導電性材料を塗布することにより、当該導電性材料からなる欠陥修正部26を形成する工程とを有する。この方法では、配線22の断線箇所24に導電性材料を塗布したときに、導電性材料の広がりがバンク25によって抑制される。

(もっと読む)

電子部品の欠陥修復装置

【課題】本発明の目的は、液晶ディスプレイを初めとする半導体装置や、その他の電子部品に欠陥が生じたとき、その欠陥箇所を修復して機能を回復させる修復装置を提供することにある。また、本発明の他の目的は、単層又は多層の薄膜をその薄膜の物理的特性を維持したまま他の箇所に転写することにある。

【解決手段】超短パルスレーザーを適宜調整して発生する超短パルスレーザー発生装置と、前記超短パルスレーザー発生装置から照射された超短パルスレーザーを所定の形状に成形するフレキシブル・マスク・パターン・ジェネレーターと、該超短パルスレーザーを集光する光学系と、修復すべき電子部品を載置して位置決めする第1のステージとを含む電子部品の欠陥修復装置。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】35mmデジタル一眼レフ・カメラ用のCMOSイメージ・センサは、チップサイズが非常に大きく、200φウエハ上に20チップ程度しか配置できない。従って、ウエハあたり、ショート欠陥が数個存在しただけで、歩留まりが大きく低下する。そこで、これらの欠陥を一般的なレーザ・トリミング技術により、除去することを検討したが、サブ・ミクロン・オーダの加工は非常に困難であることが判明した。

【解決手段】本願発明は、ピクセル・アレイ、これを横断又は縦断する複数のグローバル配線、および、各ピクセル内に設けられたローカル配線を有する半導体集積回路装置であって、第1のグローバル配線と、第1のピクセル内にあるローカル配線との間のショート不良箇所が、そのローカル配線の機能を実質的に破壊し、前記第1のグローバル配線の機能を実質的に破壊しないように、レーザ・リペア処理された修正処理部を有するものである。

(もっと読む)

欠陥修正装置

【課題】基板上の修正のための照射禁止領域の回路素子や配線上に欠陥が発生した場合に、修正を行うと、正常な部位を含みさらに損傷を与える虞がある。

【解決手段】欠陥修正装置は、参照画像との比較により基板に生じた欠陥を検出する欠陥検出部と、駆動回路素子上や配線上にある欠陥に対して修正の禁止領域(KA)を設定する禁止領域設定部と、禁止領域(KA)に掛かる欠陥部分を非修正領域とし、禁止領域(KA)に関わらない欠陥を修正領域として設定する修正領域設定部と、修正領域のみを修正する修正部とを備える。

(もっと読む)

半導体装置

【課題】微細加工技術の進展に対応可能であって、設計自由度が高く、かつ効率よく容量素子を形成することが可能な半導体装置を提供すること。

【解決手段】本発明に係る半導体装置1は、半導体基板2の上方に形成された配線層M1と、平面視上の形状が粒状に配設され、上方側において配線層M1と接続されるように当該配線層M1から下層方向に延在し、かつ第1電極からなるコンタクトプラグ10(A)と第2電極からなるコンタクトプラグ10(B)とを備え、隣接する第1電極からなるコンタクトプラグ10(A)と、第2電極からなるコンタクトプラグ10(B)間において、容量を形成するようにした容量素子領域Rbを具備する。また、容量電極の取り出し口となる配線層を、異なる配線層により構成する。

(もっと読む)

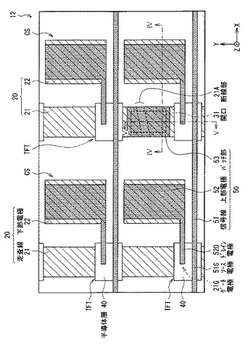

薄膜トランジスタ装置およびその製造方法

【課題】

使用現場で使用者や顧客の要望に応じて、回路システムを形成することのできる薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】

薄膜トランジスタ装置において、TFTにより構成した複数の集積回路ブロック1,2と、これらの集積回路ブロックを相互に接続するための網目状に交差したマトリックス配線3、4、5、6を設ける。相互の集積回路ブロック間の接続は、使用現場で使用者や顧客の要望に応じて導電性材料を印刷等により、マトリックス配線の各々の配線交差部に選択的に設けることにより行い、所望の回路システムを構成する。

(もっと読む)

金属−絶縁体相転移材料を用いた機能要素の形成方法及びこれによって形成された機能要素、並びに機能デバイスの製造方法及びこれによって製造された機能デバイス

【課題】金属−絶縁体相転移材料として二酸化バナジウム(VO2)を用いた機能要素の形成方法及びこれによって形成された機能要素、並びに機能デバイスの製造方法及びこれによって製造された機能デバイスを提供すること。

【解決手段】基板40の面に、金属−絶縁体相転移材料10としてVO2薄膜が形成されており、平行な2つの電極15a、15bがVO2薄膜の面に形成されている。両電極を結ぶ複数の機能要素としての金属配線20a〜20eは、レーザ光源30からのレーザ35がVO2薄膜に走査方向37で走査され、レーザ35によって照射されたVO2薄膜の部分が絶縁相から金属相に相転移して金属化されるにことよって形成される。金属配線が形成された領域の少なくとも一部にレーザを照射し、高温(例えば、100℃)とした後、低温(例えば、室温)に冷却して絶縁体化させて、金属配線が形成された領域の少なくとも一部を消去することができる。

(もっと読む)

レーザ加工装置とその制御方法

【課題】レーザ光の照射部を局所的に真空排気する局所加工部を備え、差動排気により局所加工部を被加工物上に浮上するレーザ加工装置において、被加工物表面の異物をレーザ光照射部との間に挟みこむことを防ぐ。

【解決手段】差動排気によってレーザ照射による局所加工部40を被加工物(基板11)から浮上させるにあたって、その浮上量Dを、圧縮ガス供給部63によるガス供給量と圧縮ガス排気部65によるガス排気量とのバランスを制御することで変化させ、ガス排気量を小さくして浮上量Dを高くした状態で、加工位置間の移動を行う。

(もっと読む)

薄膜トランジスタ基板前駆体及び薄膜トランジスタ基板の製造方法

【課題】液晶表示装置の表示品位の低下を抑制して、薄膜トランジスタの欠陥を修正する。

【解決手段】各画素毎にゲート電極が規定され、互いに平行に延びるように設けられた複数のゲート線11aと、各画素のゲート電極に絶縁膜を介して重なるように島状に設けられた第1半導体層13aと、各画素毎に各ゲート線11aに絶縁膜を介して重なるように島状に設けられた第2半導体層13bと、各画素毎に第1半導体層13aを介してゲート電極の一方の端部に重なるようにソース電極14aaが規定され、各ゲート線11aと交差する方向に互いに平行に延びるように設けられた複数のソース線14aと、各画素毎に第1半導体層13aを介してゲート電極の他方の端部に重なると共にソース電極14aaと対峙するようにドレイン電極14baが規定され、各画素電極にそれぞれ接続するように設けられた複数のドレイン線14bとを備えている。

(もっと読む)

半導体素子の金属構造物再形成方法

【課題】コンタクトプラグ、及び金属配線のような金属構造物に欠陥が発生して再形成工程を処理する場合、コンタクトホールが過度に露出されてホールが大きくなる現象を防止できる金属構造物の再形成方法を提供する。

【解決手段】本発明に従う金属構造物の再形成方法は、コンタクトプラグを含む絶縁層の上に形成された第1金属層、第1金属層の上に形成された金属配線層、金属配線層上に形成された第2金属層を含む金属構造物の再形成方法に関するものであって、第1ウェットエッチング工程を処理して金属配線層の下を除外した第1金属層及び第2金属層を除去するステップと、第2ウェットエッチング工程を処理して金属配線層を除去するステップと、第1平坦化工程を処理して残存した第1金属層及び絶縁層の表面を平坦化するステップと、を含む。

(もっと読む)

1 - 20 / 121

[ Back to top ]