Fターム[5F038BH01]の内容

Fターム[5F038BH01]の下位に属するFターム

抵抗 (916)

キャパシタ、インダクタンス (556)

ダイオード順方向特性 (712)

接合ブレークダウン (639)

バイポーラトランジスタ (448)

MOSトランジスタ (976)

ピンチオフ、JFET (22)

ガードリング (301)

シールド (400)

Fターム[5F038BH01]に分類される特許

61 - 80 / 146

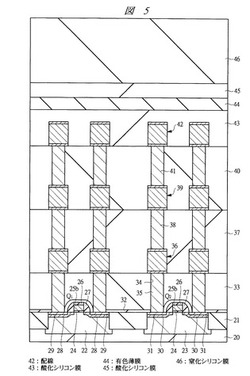

半導体装置およびその製造方法

【課題】半導体装置に記憶された情報のセキュリティ性を向上させる技術を提供する。

【解決手段】半導体基板20上に多層配線層を形成する。そして、多層配線層のうち最上層配線層に配線42を形成する。配線42上に酸化シリコン膜43、有色薄膜44および酸化シリコン膜45を順次形成し、酸化シリコン膜45上に表面保護膜となる窒化シリコン膜46を形成する。すなわち、本発明の特徴は、最上層配線層を構成する配線42と表面保護膜となる窒化シリコン膜46の間に有色薄膜44を形成する。この有色薄膜44は、可視光および特定波長域のレーザ光を減衰させる機能を有し、例えば、酸化コバルトを含有する酸化シリコン膜より形成する。

(もっと読む)

ウエハーレベルパッケージ及びウエハーレベルパッケージを用いた半導体装置の製造方法

【課題】本発明は予備試験(PT)及び最終試験(FT)が実施されるウエハーレベルパッケージ及びウエハーレベルパッケージを用いた半導体装置の製造方法に関し、製造効率の向上及び製造コストの低減を図ることを課題とする。

【解決手段】半導体チップ回路形成領域12内にチップ端子13が形成された半導体ウエハー11と、外部接続端子14が形成されてなる再配線15と、封止樹脂22とを具備するウエハーレベルパッケージにおいて、上記チップ端子13の内、試験実施時に用いられるチップ端子13Aを再配線15により回路領域12の外部位置に引出し、かつ、引き出されたこの再配線15と接続するよう試験端子16を設けると共に、この試験端子16が封止樹脂22から露出するよう構成する。また、回路領域12内にバーンイン試験専用回路32(BIST)を組み込むと共に、このBIST32から再配線15を外部領域18に引き出し、この引き出し位置において再配線15に試験端子16を形成する。

(もっと読む)

半導体集積回路装置

【課題】回路変更を行なわずにノイズレベルを下げる調整やノイズ対策の最適化が可能な半導体集積回路装置を提供する。

【解決手段】電源電圧ライン15およびグランドライン16が接続されたコアロジック回路13と、コントロールゲート19に印加される電圧によりフローティングゲート20に蓄積される電荷量が制御されるフローティングゲート構造の第1MOSトランジスタ11と、上記第1MOSトランジスタ11のフローティングゲート20に連なる延伸部30の一部をゲートとし、そのゲートとソースが電気的に接続された第2MOSトランジスタ12とを備える。上記第2MOSトランジスタ12を電源電圧ライン15とグランドライン16との間に接続する。

(もっと読む)

入力保護回路

【課題】入力端子に負極性のサージ電圧が印加された場合でも内部回路を保護できる入力保護回路を提供する。

【解決手段】入力保護回路21を構成する各回路素子を、SOI基板上にトレンチ分離で形成された領域に形成し、各素子の形成領域を確実に絶縁する。そして、負極性のサージ電圧が入力端子1に印加されると、クランプ回路42Nを構成するツェナーダイオード14が導通してFET13をONさせ、回路グランドから入力端子1に至る電流経路を形成して内部回路3を保護する。

(もっと読む)

集積回路装置及び電子機器

【課題】回路面積の縮小を実現できる集積回路装置、電子機器の提供。

【解決手段】集積回路装置は、データ線を駆動するためのデータドライバブロックと、各制御トランジスタがデータドライバブロックの各出力線に対応して設けられ、各制御トランジスタが共通制御信号により制御される複数の制御トランジスタTC1、TC2と、データ線とデータドライバブロックの出力線QL1、QL2とを電気的に接続するためのデータドライバ用パッドP1、P2が配置されるパッド配置領域を含む。そして制御トランジスタTC1、TC2がパッド配置領域に配置される。

(もっと読む)

化合物半導体スイッチ回路装置

【課題】スイッチMMICにおいて、ソース電極およびドレイン電極が近接して配置される箇所では、高周波信号の漏れが発生し、歪特性が悪い問題があった。

【解決手段】ゲート配線電極を梯子状のパターンとし、スイッチMMICの全てのソース電極−ドレイン電極間に、ゲート配線電極を配置する。また、ゲート配線電極と、ソース電極またはドレイン電極の交差部において、これらの間に比誘電率の大きい窒化膜と、比誘電率の小さいポリイミド、あるいは中空部を配置する。梯子状ゲート電極と容量低減策により2次高調波レベルを低減できる。またドレイン電極−ソース電極間の高周波信号の漏れを防止できるので3次高調波レベルを低減でき、スイッチMMICの歪特性を大幅に向上できる。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】半導体素子の発熱に起因する半導体集積回路装置の温度上昇を低減する。

【解決手段】多層配線構造を備えた半導体集積回路装置において、多層配線構造を構成する接続孔及び金属配線層と同じ導電材料からなり、信号伝送用の接続孔及び金属配線層(領域C参照)とは異なる経路で上層側に延びる熱伝導部33,35,37を備えている(領域A,E,F参照)。領域Aにおいて、完全空乏型SOIトランジスタのゲート動作により発生した熱は、コンタクト層19、メタル配線層M1、ビア層21、メタル配線層M2に伝導され、さらに熱伝導部33を介して最上層のメタル配線層M6まで伝導され、絶縁層17の上面側から放熱される。これにより、半導体集積回路装置の温度上昇を低減することができる。

(もっと読む)

過電圧保護回路を備えた半導体装置

【課題】想定外の過電圧が印加された場合でも集積回路内部の損傷や外部回路の2次的な損傷を回避できる過電圧保護回路を備えた半導体装置を提供すること。

【解決手段】本発明の半導体装置は、被保護回路の端子間に過電圧が印加された際、端子間の素子損傷を防止する過電圧保護回路を備え、前記過電圧保護回路が、第1の設定電圧より低い過電圧が印加された場合に保護動作する第1の過電圧保護回路と、前記第1の設定電圧より高い過電圧が印加された場合に、前記端子間を短絡させ半導体集積回路内部の素子損傷を回避する第2の保護回路とを有する。

(もっと読む)

集積回路装置及び電子機器

【課題】 静電気対策を施したスリムな細長の集積回路装置及びこれを含む電子機器を提供することにある。

【解決手段】 複数のパッド200A,200Bを配列したパッド列220,222と、パッド列の下層に配置され、N列のパッド列の各々のパッドにそれぞれ接続された複数の静電気保護素子D1,D2とを有する。静電気保護素子DI1,DI2の各々は、N列のパッド列220,222の各1個にて構成されるN個のパッド200A,200Bの各々の少なくとも一部をそれぞれ含む領域の下層に配置されて、N個のパッド200A,200Bの一つにそれぞれ接続されている。

(もっと読む)

高出力半導体装置

【課題】サージ耐量を高め易い高出力半導体装置を得ること。

【解決手段】支持基板1上に絶縁層3と半導体層5とがこの順に形成されたSOI基板10と、該SOI基板に形成された複数の横型DMOSトランジスタ30Aとを備え、各横型DMOSトランジスタのソース領域12の周囲にバックゲート領域14a,14bが形成されている高出力半導体装置を作製するにあたり、金属もしくは合金またはバックゲート領域と同じ導電型の不純物拡散領域により、バックゲート領域から絶縁層側に延びる導電部をバックゲート領域の各々に直接接続させて半導体層に形成する。

(もっと読む)

多層配線半導体集積回路、半導体装置

【課題】本発明の目的は、配線層の面積を拡張せずに、隣接配線層間におけるカップリング容量を低減する多層配線半導体集積回路、半導体装置を提供することである。

【解決手段】本発明の実施の形態に係わる多層配線半導体集積回路は、それぞれ信号用配線および電源供給用配線を有する多層配線基板と、当該多層配線基板上に積載されて必要な機能を実現するための半導体回路ブロックとを備えている。そして、多層配線基板は、第1の方向に沿って形成される複数の配線を備える配線層3と、配線層3に隣接して積層され、それぞれ第1の方向と平行とはならない任意の角度を成す第2の方向に沿って形成される複数の配線を備える配線層2と、さらに、配線層2に隣接して積層され、第1の方向と直角を成す方向に沿って形成される複数の配線を備える配線層1とを備えている。

(もっと読む)

犠牲相互接続部を用いたオンチップ相互接続スタック冷却

本発明は、流体冷却チャネルを集積された集積回路デバイス、およびこうした集積回路デバイスを製造する方法に関するものである。この方法は、絶縁層シーケンス内の電気相互接続部の横方向の所望位置、および流体冷却チャネル部の横方向の所望位置に凹部を形成するステップを備えている。この絶縁層シーケンスの凹部内に金属充填物を堆積させて、流体冷却チャネル部内に電気相互接続部および犠牲的充填物を形成する。その後に、この犠牲的金属充填物を、流体冷却チャネル部から選択的に除去する。  (もっと読む)

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】半導体装置の小型化を実現すると同時に半導体装置の動作時の発熱を廃棄することの可能な半導体装置および斯かる半導体装置の製造方法を提供する。

【解決手段】接地面に設けられ、半導体ウエハ102上に配線および電極端子パターン104、106が形成されている半導体装置100において、かかる電極端子パターンのうち、接地面と接続する電極端子パターンが形成されている部位には、かかる部位に設けられた電極端子パターンを貫通するようにして半導体ウエハに導通孔108が形成され、半導体ウエハには、この半導体ウエハの配線および電極端子パターンが形成されている面102aと反対側の面102bから導通孔の底部108aに達するまで、径が導通孔の各底部を包含可能な大きさである孔部110が形成され、かかる孔部には各底部および接地面を電気的に接続する一の導電体112が設けられている。

(もっと読む)

化合物半導体スイッチ回路装置およびその製造方法

【課題】スイッチMMICにおいて、ゲート配線と、ソース配線電極またはドレイン配線電極との交差部では容量が大きく、高周波信号の漏れが発生し、歪特性が悪い問題があった。

【解決手段】ゲート配線上を、比誘電率の大きい窒化膜(膜厚3000Å)と、比誘電率の小さい中空部(厚さ2μm)で被覆し、その上にソース配線電極またはドレイン配線電極を設ける。これにより交差部での容量を低減できる。またゲート電極の一端を延在して曲折部を形成し、曲折部をソース電極−ドレイン電極間に配置する。これによりスイッチMMICの全てのソース電極−ドレイン電極間に、ゲート電極(曲折部)またはゲート配線を配置できる。オフ側FETのゲート電極は高周波信号としてGND電位であるので、ドレイン電極−ソース電極間の高周波信号の漏れを防止でき、交差部の中空部の配置と併せてスイッチMMICの歪特性を大幅に向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子等に起因して発生する熱を効率よく放熱する。

【解決手段】半導体装置は、半導体基板11と、半導体基板に設けられた第1の拡散領域12と、第1の拡散領域12に設けられた半導体素子17と、第1の拡散領域12に設けられ、かつ冷却用の流体が供給される通路14とを含む。

(もっと読む)

半導体集積回路装置

【課題】高集積化及び高信頼性を実現した半導体集積回路装置を提供する。

【解決手段】第1電圧電源で動作するCMOS回路により形成された信号で、上記第1電圧電源よりも高い第2電圧電源に対応した出力信号を形成する出力回路を制御する半導体集積回路装置である。上記CMOS回路のうち、そのラッチアップ状態によって上記出力MOSFETを同時にオン状態にさせる可能性を持つ回路部分のPチャネルMOSFETとNチャネルMOSFETは、絶縁性分離手段により互いに電気的に分離された半導体領域に振り分けて形成する。上記第1回路部分を除く第2回路部分は、PチャネルMOSFETとNチャネルMOSFETとが絶縁性分離手段により電気的に分離された同じ半導体領域内に形成する。

(もっと読む)

半導体装置

【課題】無線チップでは、通信信号から電源電圧を生成するため、強大な通信信号を与えた場合には、無線チップ内部で大電圧を生成し、回路を電気的に破壊してしまう恐れがある。そこで強大な通信信号に対する耐性を備えた無線チップを提供することを課題とする。

【解決手段】無線チップは、電気回路が破壊する電圧、つまり規定電圧値以上の電源電圧に達した場合、電源配線と接地配線とが電気的に短絡する素子を有する。その結果、強大な通信信号に対する耐性を備えた無線チップを提供することができる。

(もっと読む)

半導体装置

【課題】本発明の目的は、静電気に対する保護の向上を図ることができる半導体装置を提供することにある。

【解決手段】半導体装置は、第1の電源系110に属する第1の電源ラインVDD1及び第2の電源ラインVSS1と、第2の電源系112に属する第3の電源ラインVDD2及び第4の電源ラインVSS2と、第2の電源ラインVSS1にソースが接続された第1の電界効果トランジスタ182と、第4の電源ラインVSS2にソースが接続された第2の電界効果トランジスタ192と、第1〜第4の電源ラインVDD1,VSS1,VDD2,VSS2のそれぞれを第1の静電保護素子120−126を介して共通接続する共通ライン200と、電源ラインVSS1,VSS2の少なくとも一方と共通ライン200の間に接続され、かつ少なくとも共通ライン200への方向を順方向とするダイオードとして機能する第2の静電保護素子300,400と、を含む。

(もっと読む)

半導体装置

【課題】WL−CSPアッシング工程にて、再配線パターンに溜まった電荷によって、再配線パターンと半導体基板間における絶縁破壊,内部素子、あるいは絶縁膜の破壊などの発生を防止し得る構成とする。

【解決手段】WL−CSPの再配線により形成された接続配線121,122の一方を端子パッド1,6に接続し、他方をスクライブレーン領域30に引き出した後、配線層55を介してシリコン基板56に接続されているコンタクトポスト123に接続する。これにより端子パッド1,6は、NC端子や静電耐圧の低い入力端子であっても、アッシング工程における電荷がシリコン基板56に流れてチャージされないため、電気ストレスを受けない。スクライブレーン領域30による個片分割後は、接続配線121,122がシリコン基板56と切り離されるため、端子パッド1,6は本来設定された接続端子としての機能を損なわない。

(もっと読む)

半導体装置の製造方法

【課題】優れた信頼性を有するMIM型容量素子の製造方法を提供する。

【解決手段】まず、半導体基板1上に、第1の導電膜11、誘電体膜12、及び第2の導電膜13を順に形成する。そして、第2の導電膜13をエッチングして上部電極13aを形成し、上部電極13a形成後に誘電体膜12をエッチングして容量絶縁膜12aを形成し、容量絶縁膜12a形成後に第1の導電膜11をエッチングして下部電極11aを形成する。以上の工程により形成されたMIM型容量素子1上に層間絶縁膜14が形成され、層間絶縁膜14に上部電極13aに到達するスルーホール15aが形成された時点で。スルーホール15aの底部に露出した上部電極13aに紫外光を照射する。本構成によれば、スルーホール15aの形成過程で上部電極13aに蓄積された電荷を除去することができ、当該電荷により、容量絶縁膜12aの絶縁耐圧が劣化されることを防止できる。

(もっと読む)

61 - 80 / 146

[ Back to top ]