Fターム[5F038BH01]の内容

Fターム[5F038BH01]の下位に属するFターム

抵抗 (916)

キャパシタ、インダクタンス (556)

ダイオード順方向特性 (712)

接合ブレークダウン (639)

バイポーラトランジスタ (448)

MOSトランジスタ (976)

ピンチオフ、JFET (22)

ガードリング (301)

シールド (400)

Fターム[5F038BH01]に分類される特許

81 - 100 / 146

トリガ素子を備えた低容量SCR

選択可能なトリガおよび保持電圧を備えたシリコン整流器半導体デバイスは、トリガ素子(522)を含む。半導体母材(502)中に形成された第1の電導形の第1のウエル領域(504)。第1のウエル領域中に第1の電導形の第1の領域(510)が形成される。第1のウエル領域中に第2の電導形の第2の領域(512)が形成される。半導体母材中に第1のウエル領域に隣接して第2の電導形を有する第2のウエル領域(506)が形成される。第2のウエル領域中に第1の電導形の第3の領域(514)が形成される。第2のウエル領域中に第2の電導形の第4の領域(516)が形成される。トリガ素子は、第1の領域に接続されて、ベース・トリガ電圧およびベース保持電圧を変更されたトリガ電圧および変更された保持電圧に変更する。第1の端子又はパッド(518)は、第2の領域に接続される。第2の端子(520)は、第3の領域、第4の領域およびトリガ素子に接続される。動作時に、第1の端子は、変更されたトリガ電圧が第1の端子に供給されるのに応答して、低インピーダンス状態において第2の端子に電流を流す。  (もっと読む)

(もっと読む)

半導体集積回路の設計方法および半導体集積回路

【課題】

アンテナ基準を満足するMOSFETとダミーのMOS容量素子を形成することにより、アンテナ効果による素子破壊を防止する半導体集積回路の設計方法および半導体集積回路に関する。

【解決手段】

半導体基板4上に形成されたゲート配線層2と、トランジスタ形成領域上の前記ゲート配線層2下部に形成されたゲート酸化膜5と、半導体基板4上の前記ゲート配線層2下部に形成されたダミーゲート酸化膜13とを有し、前記ゲート酸化膜5と前記ダミーゲート酸化膜13を合わせた電荷許容量が、予め設定された値以上であることを特徴とする半導体集積回路である。

(もっと読む)

半導体装置及びその製造方法

【課題】 SOI等の高価な基板を使用することなく、基板ノイズを安価に低減できるようにした半導体装置及びその製造方法を提供する。

【解決手段】 フローティングゾーン法にて作成された500Ωcm以上の抵抗率を持つ高抵抗シリコン基板1と、高抵抗シリコン基板1上に形成されたシリコンエピタキシャル層4と、シリコンエピタキシャル層4上から高抵抗シリコン基板1の内部にかけて設けられたディープ・トレンチ構造体50と、を備え、ディープ・トレンチ構造体50によってアナログ回路部とデジタル回路部とが分離されている。基板表面を伝わるノイズについてはディープ・トレンチ構造体50により、基板の深い部分を伝わるノイズについては基板そのものの抵抗により、それぞれ抑えることができる。

(もっと読む)

半導体集積回路

【課題】 I/O部からのノイズの侵出を低減することができる半導体集積回路を提供する。

【解決手段】 この半導体集積回路1は、半導体基板2の外周に沿って環状に形成されたN型のレトログレードウェル8と、レトログレードウェル8の上層に形成されたPウェル15と、Pウェル15の周囲を囲うようにレトログレードウェルの上層に形成されたNウェル13、21と、半導体基板2に形成されたNウェル23と、NMOSトランジスタ31がPウェル15の中に形成され、PMOSトランジスタ32がNウェル23の中に形成されたI/Oセル7とを具備する。

(もっと読む)

半導体装置

【課題】ヒューズ素子を備えた半導体装置において静電ノイズの影響を抑制する。

【解決手段】スイッチング素子26と、第1及び第2のヒューズ素子22,24とを備え、第1のヒューズ素子22とスイッチング素子26とは直列接続され、その直列回路の両端は共に基準電位(接地電位GND)に保持された基準ラインに接続され、第1のヒューズ素子22とスイッチング素子26との接続点に第2のヒューズ素子24の一端が接続され、第2のヒューズ素子24の他端に制御電圧を印加することによって第1のヒューズ素子22を溶断することができる半導体装置によって上記課題を解決することができる。

(もっと読む)

集積回路装置

【課題】集積回路から発生する熱の蓄積に起因する問題を解決することを課題とする。

【解決手段】一方の面上に集積回路が形成された基板を有している。この基板の他方の面(集積回路が形成されていない側の面)は、凹部が形成されており、一方の面と比較して表面積が大きくなっている。そして、他方の面に形成された凹部には、放熱性材料が充填される、もしくは、少なくとも凹部の表面に放熱性材料を含む膜が形成される。また、このような集積回路装置が多層に設けられていてもよい。

(もっと読む)

半導体装置

【課題】ヒューズ素子を備えた半導体装置において静電ノイズの影響を抑制する。

【解決手段】第1から第3のヒューズ素子22,24,26を備え、第1のヒューズ素子22の第1端子は所定の基準電位Vccに保持された基準ラインに接続され、第1のヒューズ素子22の第2端子は第2のヒューズ素子24の第1端子及び第3のヒューズ素子26の第1端子と接続され、第2のヒューズ素子24の第2端子は第1の電極28に接続され、第3のヒューズ素子26の第2端子は第2の電極30に接続される。これによって、上記課題を解決することができる。

(もっと読む)

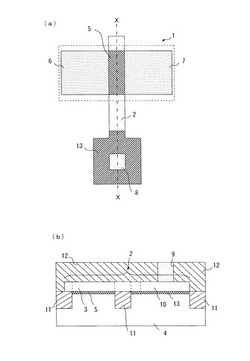

静電気放電保護デバイス

本発明は、少ないデバイス面積で以って、ESD発生電流の放電性能を増強した静電放電(ESD)保護デバイスを提供する。ESD保護デバイスは、第2の半導体型の第1のウエル領域(7)により介挿された、第1の半導体型のソース領域(3)とドレーン領域(4)を含むゲート接地MOSトランジスタ(1)を備える。第1ウエル領域(7)により介挿される、第1の半導体型の第2のウエル領域(6)は、ソース領域(3)とドレーン領域(4)の下方に設けられる。隣接したウエル領域(6、7)とそれぞれ同じ半導体型からなる重度にドーピングされた埋め込み領域(8、9)、がウエル領域(6、7)の下方に設けられる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】電気的にフローティングした配線に蓄積する電荷を、半導体基板に逃がすこと。

【解決手段】第1主面12aを備えた半導体基板12と、第1主面側に設けられたMOSFET14と、MOSFETのゲート電極26およびゲート電極に電気的に接続された配線を含む第1配線構造体36と、第1主面および第1主面に電気的に接続された配線を含む第2配線構造体38と、第1および第2構造体のどちらとも接触し、かつ、第1および第2配線構造体間を接続している、酸化イットリウムからなる非導電性膜16とを備える

(もっと読む)

高速・高周波数デバイスのためのチップ間ESD保護構造体

【課題】 集積回路チップを、静電放電(ESD)又は損傷を与える可能性がある他の電圧変動から保護する構造体、及びこうした構造体を製造する方法を提供すること。

【解決手段】 本発明は、1つ又はそれ以上の直接的なチップ間信号伝送経路を含む、高速、及び高周波数デバイスのための、チップ間の静電放電(ESD)保護構造体に関する。具体的には、本発明は、(1)第1の回路を含む第1のチップと、(2)第2の回路を含む第2のチップと、(3)第1のチップと第2のチップとの間に配置された中間絶縁体層とを含む構造体に関し、第1の回路及び第2の回路が、中間絶縁体層を通して信号を伝送する信号伝送経路を形成する。静電放電(ESD)保護経路が、中間絶縁体層を通して第1のチップと第2のチップとの間の構造体内に形成され、信号伝送経路をESD損傷から保護する。

(もっと読む)

半導体装置

【課題】半導体チップの温度分布を極力均一にする半導体装置を提供する。

【解決手段】半導体チップの中心電力密度を小さく、チップ周辺に向かうに従って電力密度を大きくし、チップ内の温度分布を小さくしたことを特徴とする半導体装置。半導体チップ内に素子のセルを形成しない領域を作成し、その面積密度を調整することにより、半導体チップ内のセル密度を小さく、チップ周辺に向かうに従ってセル密度を大きくし、チップ内の温度分布を小さくしたことを特徴とする半導体装置。半導体チップ内に一様に素子を形成するが、素子の一部については動作しないように配線することにより、半導体チップ内の動作する素子セル密度を小さく、チップ周辺に向かうに従って動作しないセル密度を大きくして、チップ内の温度分布を小さくしたことを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】 隣接する素子への影響を可及的に低減することを可能にする。

【解決手段】 Ge基板2に設けられた空孔6aと、空孔の上面を覆いGeを含む絶縁膜6bと、を備えている。

(もっと読む)

半導体集積回路装置

【課題】 ノイズ除去用の外付けのフィルタなどを不要としながら、耐ノイズマージンを大幅に向上させる。

【解決手段】 半導体集積回路装置に設けられた入力バッファ部14にHi(ネゲート)固定のパワーオンリセット信号が入力されている場合、Hパルスディレイ回路17は、シュミット入力バッファ16から出力された信号を任意の時間遅延してHパルスRCフィルタ回路18に出力する。パワーオンリセット信号に重畳したノイズによってトランジスタPM1がONしても、node5は、抵抗R1〜Rnと静電容量素子C1〜Cnとの回路時定数により、電圧レベルが徐々にしか上昇しないことになり、次段のシュミット入力バッファ19には電圧レベルの変動がないLo信号が出力される。

(もっと読む)

バルク抵抗制御技法

本発明は、ソース領域、ドレイン領域、およびソース領域とドレイン領域の間に配置されたチャネル領域の上に形成されてゲート領域を有する少なくとも1つのインタリーブ・フィンガ(interleaved finger)を含む、ESD保護を可能にするMOSトランジスタ装置を提供する。このトランジスタ装置は、インタリーブ・フィンガのうちの少なくとも1つに形成された少なくとも1つの分離ゲートをさらに含む。この装置は、ソース領域、ドレイン領域、およびゲート領域のうちの少なくとも1つに、ダイオード、MOS、抵抗、キャパシタ、インダクタ、短絡などのうちの少なくとも1つによって結合されたバルク接続部をさらに含むことができる。バルク接続部は、分離ゲートによって分離されることが好ましい。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体素子の性能を十分に引き出すことができる半導体装置を提供する。

【解決手段】 周囲がIGBTセル1001で囲われるように、圧接用ヒートスプレッダ304で圧接される領域の略中央にセンサダイオード302を配設した。圧接用ヒートスプレッダ304がセンサダイオード302および温度センサハーネス303を押圧しないように、IGBT101のエミッタ電極1007に接触する圧接用ヒートスプレッダ304の下面側には溝部305が設けられている。これにより、活性領域301の発熱によるIGBT101の温度変化に対して、センサダイオード302で検出される温度の応答性を向上できるので、センサダイオード302で検出される温度に基づいてIGBT101の温度上昇保護を行う際に、従来の半導体装置のように不必要なマージンをとる必要がなく、IGBT101の性能を十分に引き出すことができる。

(もっと読む)

半導体集積回路

【課題】 複数の回路ブロックにそれぞれ位相をずらしたクロックを供給する半導体集積回路において、各回路ブロックへ供給する各クロックの位相ずれ量を電源ノイズ波形の周期に基づいて設定することで、位相の異なる電源ノイズ波形を干渉させて電源ノイズを低減させる。

【解決手段】 半導体集積回路(IC)は、4つの回路ブロックBL1〜BL4と、各回路ブロックBL1〜BL4へそれぞれ供給する各クロックA〜クロックDの位相を設定する位相設定回路10を有する。位相設定回路10は、ベースクロックをクロックAとして第1の回路ブロックBL1へ供給し、各外部入力端子A,B,Cに供給される各電圧に基づいて各クロックB,C,Dの位相ずれ量(遅延時間)をそれぞれ設定する。

(もっと読む)

静電気放電回路及びこれを有する集積回路

【課題】低いトリガ電圧を有する静電気放電保護回路を提供する。

【解決手段】静電気放電保護回路は、2つのノード間に連結され、ESDイベントが発生する時、第1トランジスタをターンオンさせる連結負荷と、アバランシェ降伏による電流を発生させる第2トランジスタとを含み、アバランシェ降伏による電流によってラッチアップ電流が発生する。

(もっと読む)

レギュレータ

【課題】 小型化を図ることができるともに過電流の検出精度が高いレギュレータを提供する。

【解決手段】 電流供給用端子部T2を有するリードフレーム(不図示)と、電流供給用パッドP2を有するICチップ(不図示)と、電流供給用端子部T2と電流供給用パッドP2とを電気的に接続する電流供給用ワイヤW2とを備え、電流供給用ワイヤW2の両端電圧差に基づいて過電流を検出するコンパレータ5を前記ICチップ内に設けるレギュレータ。

(もっと読む)

半導体集積回路

【課題】ウェルおよび深層ウェルの電位を半導体集積回路の電位と分離して、他の回路が発生するノイズ伝播を抑制する。

【解決手段】P型MOSトランジスタのバルクにはインバータ回路のVDDパッド15と分離したバルク専用パッド17、また、N型MOSトランジスタのバルクにもインバータ回路のVSSパッド16と分離したバルク専用パッド18を設ける。VDDパッド15,VSSパッド16は他の回路とも共通で、他の回路にノイズ発生源がある場合、VDDパッド15,VSSパッド16を経由する。バルク専用パッド17,バルク専用パッド18は、VDDパッド15,VSSパッド16と分離され、また、それぞれのパッドまでの配線に配線抵抗19が存在しており、各MOSトランジスタのバルクに他の回路が発生するノイズが伝播することを抑制できる。

(もっと読む)

半導体装置

【課題】SOI基板を用いた半導体装置の製造時にけるプラズマプロセス中に発生する支持基板の表面・裏面の帯電によって生じる半導体素子の劣化を防止する。

【解決手段】SOI基板50におけるSOI層53に形成されたMOSトランジスタ60と、SOI層53を覆う層間絶縁膜80上に形成され、Via81によってMOSトランジスタ60のゲート電極64又は拡散領域61,62と接続された配線パタン82と、この配線パタン82とSOI基板50の支持基板51との間に接続され、配線パタン82を形成するプラズマプロセスにおいてゲート電極64に対して発生する電荷が所定値を超えたときに、この電荷を支持基板51側へ放出又は遮断する保護回路とを有している。保護回路は、例えば、前記所定値に対応するブレークダウン電圧値をそれぞれ有するPN接合ダイオード71及びNP接合ダイオード72の直列回路により構成されている。

(もっと読む)

81 - 100 / 146

[ Back to top ]