Fターム[5F038EZ13]の内容

Fターム[5F038EZ13]に分類される特許

81 - 100 / 776

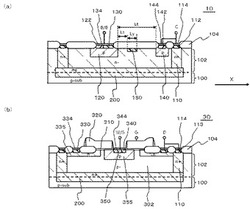

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

抵抗素子および抵抗素子の製造方法

【課題】膜厚のばらつきに起因する抵抗値の変動を抑制し、より高精度な抵抗素子を提供する。

【解決手段】第1膜厚(T1)(H1)で形成され、第1幅(W1)を有する抵抗素子第1部分(2)と、第1膜厚(T1)(H1)で形成され、第1幅(W1)に依存して決定する第2幅(W2)を有する抵抗素子第2部分(3)とを具備する抵抗素子を構成する。ここにおいて、第1幅(W1)と第2幅(W2)との和は一定である。また、抵抗素子第1部分(2)は、抵抗素子第1部分(2)の底面からの高さが第1高さ(H1)となる位置に、抵抗素子第1部分(2)の上面を有する。また、抵抗素子第2部分(3)は、抵抗素子第1部分(2)の底面を含む面からの高さが第1高さ(H1)となる位置に、抵抗素子第2部分(3)の上面を有する。そして、抵抗素子第1部分(2)と抵抗素子第2部分(3)とは、接続部を介して互いに接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

半導体装置

【課題】無線通信によりデータの交信を行う半導体装置において、装置を大型化することなく、アンテナの感度を向上させ、チップをノイズから保護することを課題とする。

【解決手段】コイル状のアンテナと当該コイル状のアンテナに電気的に接続された半導体集積回路とを有する。コイル状のアンテナと重なるように半導体集積回路を配置する。このように、半導体装置内のコイル状のアンテナと半導体集積回路の配置を工夫することで、装置を大型化することなく、アンテナの感度を向上させて、半導体集積回路が動作するために十分な電力を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲート電極を備えるトレンチゲート構成のパワーMISFETにおいて、MISFETの性能向上を図りながら、ゲート絶縁膜の静電破壊を防止することができる技術を提供する。

【解決手段】ダミーゲート電極9aを備えるトレンチゲート構成のパワーMISFETと保護ダイオードとを同一の半導体基板1上に形成する。そして、保護ダイオードをソース電極24とゲート配線25の間に設ける。このような半導体装置の製造方法において、ダミーゲート電極9a用のポリシリコン膜と保護ダイオード用のポリシリコン膜を同時に形成する。また、パワーMISFETのソース領域と保護ダイオードのn+型半導体領域15を同一工程で形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン以外の半導体で形成される半導体素子で使用可能なTEGを有する半導体装置およびその製造方法を提供する。

【解決手段】SBD部2aと、SBD部2aの電気特性を測定するためのTEG部3aと、を備えた半導体装置1aであって、SBD部2aは、n型のSiCドリフト層8と、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第1のショットキー電極13と、を有し、TEG部3aは、SiCドリフト層8の表面9を含む箇所に形成されたp型のイオン注入層18aと、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第2のショットキー電極21aと、第2のショットキー電極21aと電気的に接続され、SiCドリフト層8とは接触しないようにイオン注入層18a上に形成された電極パッド22と、を有する

(もっと読む)

保護装置

【課題】 差動信号ラインに、第1入力端子と第2入力端子を有し、ダイオードにより構成される1パッケージの保護装置を接続する場合、第1入力端子と第2入力端子間のアイソレーションを十分確保し、また、第1入力端子に接続するダイオードと第2入力端子に接続するダイオードの部品ばらつきを抑制する必要がある。また、差動信号ラインに用いる保護装置の場合、部品容量とESD破壊耐量を所望の範囲に収めるようにする必要がある。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域、第2n+型不純物領域、第3n+型不純物領域を設け、第1入力端子に接続する第1n+型不純物領域と、第2入力端子に接続する第3n+型不純物領域との間に、接地端子に接続する第2n+型不純物領域を配置して、横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や耐圧の汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面に互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、これらの周囲に互いに離間する第1p+型不純物領域と第2p+型不純物領域を設け、第1n+型不純物領域とコンタクトし、入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトし、接地端子に電気的に接続する第2電極とを設ける。第1n+型不純物領域および第2n+型不純物領域は140μm以上離間され、それぞれ角丸四角形状でp+型半導体基板の対角線に沿って配置される。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、第1n+型不純物領域とコンタクトする第1導電層と、第1導電層にコンタクトし入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトする第2導電層と、第2導電層にコンタクトし接地端子に電気的に接続する第2電極とを設けて横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】本発明は、大容量化及び小面積化の要請に応えつつ、電圧依存性の低いキャパシタ装置及びその製造方法を提供することを目的とする。

【解決手段】シリコン31、32からなる下部電極30上に、容量絶縁膜40と上部電極50が順次積層形成されたキャパシタ装置であって、

前記下部電極は、互いに導電極性の異なるN型領域20とP型領域10とが所定比率で混在配置されているとともに、前記N型領域の表面が前記P型領域の表面よりも窪んだ凹凸構造を有することを特徴とする。

(もっと読む)

半導体装置

【課題】高い比精度が要求される複数のトランジスタの特性ばらつきを低減する。

【解決手段】本発明の半導体装置は、半導体基板上に配置されたトランジスタTr1と、半導体基板上で見たキャリアのドリフト方向がトランジスタTr1のキャリアのドリフト方向と同じ方向となる向きに配置されたトランジスタTr2と、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51b同士を接続する拡散層51cと、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51bまたはその拡散層同士を接続する拡散層51cの表面に接続され、拡散層51a,51bに給電するためのコンタクトプラグ61と、を備える。

(もっと読む)

半導体装置

【課題】トレンチゲート型パワーMOSFETのゲート電極の微細化に伴って、トレンチ底部の曲率が大きくなり、その部分に電界が集中し、ゲート酸化膜(絶縁膜)の劣化が起きる。このゲート絶縁膜の劣化は、Nチャネル型パワーMOSFETの場合、ゲート側バイアスが負である場合に起こりやすく、Pチャネル型パワーMOSFETの場合、ゲート側バイアスが正である場合に起こりやすい。

【解決手段】本願発明は、絶縁ゲート型パワー系トランジスタ等をチップ内に具備する半導体装置であって、ゲート保護素子は双方向ツェナーダイオードを具備し、前記双方向ツェナーダイオードは、そのゲート側がマイナスバイアスされたときの耐圧と、そのゲート側がプラスバイアスされたときの耐圧とは相互に異なるように、複数の濃度の異なるP型不純物領域(またはP型不純物領域)を有する。

(もっと読む)

半導体装置、およびその製造方法

【課題】従来に比して高いESD耐量性能を有するESD保護回路を備えた半導体装置、およびその製造方法を提供する。

【解決手段】内部回路に用いられる第1の半導体素子と、静電気による内部回路の破壊を抑制するESD保護回路として用いられる第2の半導体素子とを備える半導体装置の製造方法であって、基板に第1の半導体素子および第2の半導体素子各々についての端子領域層を形成する端子領域層形成ステップと、基板上の前記第2の半導体素子の端子領域層を除く領域について結晶欠陥を形成させる処理を施す欠陥形成ステップと、金属膜を第1の半導体素子および第2の半導体素子各々の端子領域層表面に形成する金属膜形成ステップと、金属膜と、第1の半導体素子および第2の半導体素子各々の端子領域層とをシリサイド化するシリサイド化ステップとを含む、半導体装置の製造方法である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】トランジスタが有するしきい値相当分の電圧/電流のロスを低減し、プロセスの簡略化、及び回路構成の簡素化を目的とした整流特性を有する半導体装置(RFID)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFID)を構成する素子に整流回路を設ける。整流回路において、電波を受信するアンテナと整流回路のトランジスタのゲートとドレイン端子との間に、コイルを重ねて配置することで、電波を受信するアンテナとコイルの結合を利用して、ダイオード単体と比較しダイオードとコイルが出力する電圧を大きくし、整流効率を向上させる。

(もっと読む)

半導体装置

【課題】補償容量素子を構成する容量絶縁膜が破壊されることのない半導体装置を提供する。

【解決手段】第1の電圧が供給される第1の電源端子29と、第2の電圧が供給される第2の電源端子23と、容量絶縁膜42と該容量絶縁膜42を挟んで形成される第1及び第2電極とを其々備えており、前記第1及び第2の電源端子間に直列に設けられる複数の補償容量素子4と、奇数番目の前記補償容量素子4と次の偶数番目の前記補償容量素子4とを各々接続する第1の配線層に形成された第1の容量接続配線と、偶数番目の前記補償容量素子4と次の奇数番目の前記補償容量素子4とを各々接続する第2の配線層に形成された第2の容量接続配線と、前記第1及び第2の容量接続配線のいずれか一方に隣接して設けられ、実質的に固定された電圧が供給されるシールド配線5と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】エッチング装置の経時変化や状態変化等によらずトレンチの深さのばらつきを低減することができる半導体装置の製造方法を得る。

【解決手段】まず、所望の深さよりも浅い深さを持つトレンチ16をSi基板10の主面に形成する。次に、トレンチ16の深さを測定する。トレンチ16の底面からSi基板10に酸素イオン18を注入する。この際に、測定したトレンチ16の深さと所望の深さの差に基づいて酸素イオン18の注入エネルギーを調整して、Si基板10の所望の深さに酸素イオン18が注入されるようにする。次に、熱処理を行って酸素イオン18を注入した位置にSiO2膜22を形成する。次に、SiO2膜22をエッチングストッパとして用いて、トレンチ16の底面からSi基板10を更にエッチングしてトレンチ24を形成する。その後、SiO2膜22を除去する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】ガードリングを有する半導体装置の製造安定性を向上させる。

【解決手段】半導体装置100は、素子形成領域101および素子形成領域101の外周を取り囲むガードリング120が設けられたシリコン基板と、シリコン基板上に設けられ、ガードリング120の上部全体を覆う層間絶縁膜を含む。ガードリング120は、シリコン基板の素子形成面の近傍に設けられたNウェル103とNウェルの表層に設けられたN+領域とを含む。Nウェル103の平面形状は、コーナー部119を含む環状であって、層間絶縁膜のNウェル103の上部の領域のうち、コーナー部119の上部以外の領域の全周にわたって、層間絶縁膜を貫通するビアホール105が設けられているとともに、コーナー部119の上部の領域において、ビアホール105が設けられていない。

(もっと読む)

固体撮像装置、および、その製造方法、電子機器

【課題】撮像画像の画像品質、装置の小型化、装置の信頼性、製造効率などの各特性について向上させる。

【解決手段】複数の転送電極31が間を隔てて垂直方向yに並ぶように単一の導電材料層313を加工して形成する。また、第1キャパシタ電極C11および第2キャパシタ電極C21について、転送電極31へ加工される導電材料層313から形成する。

(もっと読む)

81 - 100 / 776

[ Back to top ]