Fターム[5F038EZ13]の内容

Fターム[5F038EZ13]に分類される特許

61 - 80 / 776

半導体装置及びその製造方法

【課題】占有面積の小さい抵抗体を有する半導体装置を提供する。

【解決手段】半導体基板上のフィールド酸化膜の上に導電性多結晶シリコンを形成し、その上を覆う絶縁膜に多結晶シリコン5に達するコンタクトホールを形成する。コンタクトホールの中にはタングステンサイドウォール9、シリコン酸化膜サイドウォール10、抵抗体11があり、抵抗体の上には電極12を配置することで上下方向に縦長の抵抗体11とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

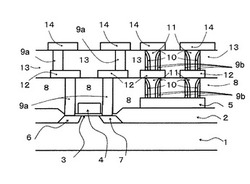

半導体装置およびその製造方法

【課題】同一半導体基板上に、トランジスタ素子、及び、容量素子、及び、抵抗素子を有する半導体装置において、十分な機能を有する容量素子を提供する。

【解決手段】容量素子をアクティブ領域上、抵抗素子を素子分離領域上に同一の多結晶シリコンで形成した後、CMPやエッチバック等で、所望の抵抗体の膜厚になるまで、基板表面を平坦化させながら削る。この時、アクティブ領域と、素子分離領域との高さの違いによって、膜厚の薄い抵抗素子と、膜厚の厚い容量素子の上部電極が形成される。容量素子の上部電極が十分な膜厚を持つので、コンタクトの突き抜けや、高抵抗化に伴う電圧依存性の増加などの特性劣化が防止され、アナログ回路に必要な高抵抗素子とプロセスを共通化することが可能であり、かつ、十分な機能を有する容量素子を製造することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】素子分離領域での電流リークを低減する。

【解決手段】抵抗素子5用の多結晶シリコン膜50の第2領域52にはドーパントがイオン注入されている。抵抗素子6用の多結晶シリコン膜60の第2領域62には窒素等がイオン注入されている。第2領域52,62は第1領域51,61よりも結晶欠陥密度が高い。抵抗素子7用の多結晶シリコン膜70中の結晶欠陥密度はシリサイド膜73付近においてより高い。抵抗素子8用の多結晶シリコン膜80は素子分離絶縁膜3の開口内のシリサイド膜を介して基板2に接している。当該シリサイド膜付近の基板表面2S内の結晶欠陥密度は周辺よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

半導体装置、及びそれを用いた装置

【課題】信頼性を向上させることができる半導体装置,半導体装置を用いた回転電機または車両を提供する。

【解決手段】ショットキ接合と、pn接合を備える半導体装置であって、pn接合は高濃度P型拡散層5とN型拡散層4で形成され、低濃度P型拡散層6と金属電極7により、ショットキ接合が形成され整流領域のpn接合部の降伏電圧を、前記ショットキ接合及びガードリング部Z2のpn接合より低くすることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子について、レイアウト面積の増大を防ぎつつ、周辺の電荷の影響を受けずに安定した抵抗値を得ることができ、しかも、抵抗体に印加できる電位の極性に制限のない半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1上のLOCOS酸化膜3上に形成された抵抗素子10と、を備え、抵抗素子10は、LOCOS酸化膜3上に形成されたシールド用ポリシリコン膜11と、シールド用ポリシリコン膜11上に形成されたシリコン酸化膜13と、シリコン酸化膜13上に形成されたポリシリコン抵抗体15と、ポリシリコン抵抗体15の一方の端部に接合された第1の電極21と、ポリシリコン抵抗体15の他方の端部に接合された第2の電極22と、シールド用ポリシリコン膜11に接合された第3の電極23と、を有し、第1の電極21及び第2の電極22うちの一方が、配線25を介して第3の電極23と電気的に接続されている。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

半導体装置およびその製造方法

【課題】ダミーアクティブ領域の配置に伴うチップ面積の増大を引き起こすことなく、半導体基板の表面の平坦性を向上させる。

【解決手段】ダミーアクティブ領域であるn型埋込み層3の上部には、厚い膜厚を有する高耐圧MISFETのゲート絶縁膜7が形成されており、このゲート絶縁膜7の上部には、内部回路の抵抗素子IRが形成されている。n型埋込み層3と抵抗素子IRとの間に厚いゲート絶縁膜7を介在させることにより、基板1(n型埋込み層3)と抵抗素子IRとの間に形成されるカップリング容量が低減される構造になっている。

(もっと読む)

保護素子及び保護素子を備えた半導体装置

【課題】比較的小さい面積で形成することができ、かつ、素子サイズの微小化が進んでも保護素子として動作させることを可能にする、保護素子を提供する。

【解決手段】半導体基板1に形成された、第1導電型のウェル領域3と、この第1導電型のウェル領域3に隣接して形成された、第2導電型のウェル領域4と、第1導電型のウェル領域3に形成された、第2導電型チャネルのMOSトランジスタと、第1導電型のウェル領域3とMOSトランジスタのソース領域とMOSトランジスタのゲートとに電気的に接続された第1の配線と、MOSトランジスタのドレイン領域と第2導電型のウェル領域4とに電気的に接続された第2の配線とを含む保護素子を構成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

半導体装置製造工程におけるチャージアップ検出方法

【課題】絶縁ゲート型電界効果トランジスタを製造する途中で、絶縁ゲート型電界効果トランジスタに悪影響を与えるチャージアップが生じているのを検出することができる半導体装置製造工程におけるチャージアップ検出方法を提供する。

【解決手段】絶縁体10上の半導体層12に、素子分離領域18によって素子分離された絶縁ゲート型電界効果トランジスタ用の第1の活性層16と検出素子用の第2の活性層16とを形成し、前記第1の活性層と第2の活性層上に第1および第2の絶縁膜22をそれぞれ形成し、少なくとも第1および第2の絶縁膜22上に第1および第2の導体24をそれぞれ形成し、第1および第2の導体24に電荷が供給される処理を行い、その後、第2の活性層16の形状を検出する。

(もっと読む)

DC−DCコンバータ及びその作製方法

【課題】単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ること、及び、DC−DCコンバータの占有面積の増大を抑制する。

【解決手段】入力電圧が印加される入力端子と、入力端子と接続され第1のトランジスタを有する電圧変換回路と、電圧変換回路を制御し珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、入力端子と制御回路との間に設けられ入力電圧を入力電圧より低い電圧である電源電圧に変換する第3のトランジスタとを有し、第1のトランジスタ及び第3のトランジスタは酸化物半導体材料をチャネル形成領域に有するトランジスタであり、第2のトランジスタ、並びに、第1のトランジスタ及び第3のトランジスタは、絶縁膜を介して積層されているDC−DCコンバータ及びその作製に関する。

(もっと読む)

半導体装置の製造方法

【課題】シート抵抗のバラツキの少ない、さらに製造工程を短くすることができる製造方法を提供する。

【解決手段】半導体層が積層した半導体領域に不純物イオンを注入して、抵抗素子を形成する半導体装置の製造方法において、第1の半導体層4上に第2の半導体層5が積層され、第1の半導体層からなる抵抗素子を形成する際、第2の半導体層の厚さを変えることで、第1の半導体層に達する不純物イオンの量を制御し、予め設定されたシート抵抗の抵抗素子を形成する。

(もっと読む)

フリップチップ半導体ダイのパッドレイアウトを形成する半導体素子および方法

【課題】半導体素子を作製する方法を提供する。

【解決手段】主に半導体ダイの周辺領域中に位置する信号パッドと、主に前記信号パッドから半導体ダイの内部領域中に位置する電力パッドおよび接地パッドとを伴う、ダイパッドレイアウトを有する半導体ダイを提供するステップと、前記信号パッド、電力パッド、および接地パッド上に複数のバンプを形成するステップと、基板を提供するステップと、前記基板上に相互接続部位を伴う複数の伝導性トレースを形成するステップであって、前記バンプは、相互接続部位よりも幅広い、ステップと、前記バンプが前記相互接続部位の頂面および側面を覆うように、前記バンプを前記相互接続部位に接着するステップと、前記半導体ダイと基板との間で前記バンプの周囲に封入材を堆積させるステップとを含む、半導体素子を作製する方法。

(もっと読む)

高電圧バイポーラベースESD保護構造

【課題】面積効率の良い高電圧の単極性ESD保護デバイスを提供する。

【解決手段】ESD保護デバイス300は、p型基板303と、基板内に形成され、カソード端子に接続されるn+及びp+コンタクト領域310、312を包含し、第1のpウェル308−1と、基板内に形成され、アノード端子に接続されるp+コンタクト領域311のみを包含する第2の別個のpウェル308−2と、第1及び第2半導体領域を取り囲み且つこれら半導体領域を分離するように基板内に形成された、電気的にフローティングのアイソレーション構造304、306、307−2とを含む。カソード及びアノードの端子に、トリガー電圧レベルを上回る正電圧が印加されると、ESD保護デバイスは、構造を通り抜ける低インピーダンス経路を提供してESD電流を放電するよう、内在サイリスタをスナップバックモードに入らせる。

(もっと読む)

61 - 80 / 776

[ Back to top ]