Fターム[5F038EZ13]の内容

Fターム[5F038EZ13]に分類される特許

141 - 160 / 776

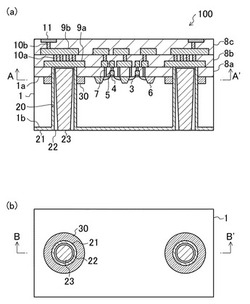

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置の信頼性を向上させる。

【解決手段】半導体基板1は、素子形成面である第1の面1a及びその反対側の第2の面1bを有する。第1の面1aから第2の面1bまで半導体基板1を貫通するように貫通孔20が形成されている。貫通孔20の内壁上に絶縁膜21及びバリア膜22が順次形成されている。絶縁膜21及びバリア膜22が形成された貫通孔20が埋まるように導電部23が形成されている。貫通孔20の周辺に位置する部分の半導体基板1における少なくとも第1の面1a側にゲッタリングサイト30が形成されている。

(もっと読む)

連続ウェルデカップリングコンデンサのためのシステムおよび方法

デカップリングコンデンサは、反対極性のウェル(102、104)内に形成された一対のMOSコンデンサ(106,108)を含む。各MOSコンデンサは、1組のウェル接続部および高ドーズ注入部(110、112、114、116)を有し、これにより、蓄積バイアスまたは空乏バイアス下における高周波性能が可能となる。各MOSコンデンサの上側導体は、他方MOSコンデンサのウェル接続部へと電気的に接続され、論理トランジスタウェルによって連続してバイアスされる。前記MOSコンデンサのウェル接続部および/または高ドーズ注入部は、ドーパント極性について非対称性を示す。 (もっと読む)

保護トランジスタおよび半導体集積回路

【課題】占有面積が小さく、所望の耐圧と熱破壊の防止を両立した保護トランジスタを提供する。

【解決手段】ゲート長方向の一方の側でゲート直下の領域に隣接しているゲート・ドレイン間領域REgdが、ゲート幅方向に互いに隣接する領域として、第1領域REgd1と第2領域REgd2とを有する。第1領域は、ドレイン耐圧が相対的に大きく、第2領域は、ドレイン電極(ドレインコンタクト部に設けられているシリサイド層10D)からの距離が平面視で第1領域より遠く、ドレイン耐圧が相対的に小さい。このため、耐圧が低いゲート・ドレイン間領域REgd2の加熱部分Aからドレインコンタクト部が遠いが、面積は小さく(または拡大しない)構造となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタに適当なしきい値電圧が与えられる一方、抵抗素子はシリコン膜からなる抵抗体層の異常成長を抑制して、シリコン膜の膜厚を安定化する。

【解決手段】半導体装置は、半導体基板10の上部に形成された素子分離領域12によって囲まれた第1の活性領域10a、第1の活性領域の上に形成された第1の高誘電体膜14aを有する第1のゲート絶縁膜27a、及び第1のゲート絶縁膜の上に形成された第1のゲート電極28aとを有する第1導電型の第1のMISトランジスタ1aと、素子分離領域の上に形成された第2の高誘電体膜14x、及び該第2の高誘電体膜の上に形成されたシリコンからなる抵抗体層20xを有する抵抗素子1xとを備えている。第1の高誘電体膜と第2の高誘電体膜とは、互いに同一の高誘電体材料からなり、第1の高誘電体膜は第1の調整用金属を含み、第2の高誘電体膜は第1の調整用金属を含まない。

(もっと読む)

保護素子及び半導体装置

【課題】半導体素子を保護する保護素子を備え、静電破壊が抑制され、信頼性の高い半導体装置を提供する。

【解決手段】半導体装置1は、チャネル層105とキャップ層112とを含む半導体積層体113と、半導体積層体113上に形成された下部電極213と上部電極216とを有する少なくとも1つの半導体素子1Xと、半導体素子1Xと共通の半導体積層体113を有し、半導体素子1Xを保護する少なくとも1つの保護素子1Yとを備えたものである。保護素子1Yは、キャップ層112を厚み方向に貫通するリセス部221と、リセス部221の底面221Bから半導体積層体113内に厚み方向に形成された絶縁領域218Yと、リセス部221を挟んで両側に形成されたキャップ層112に接続された一対のオーミック電極219、220とを備えたものである。

(もっと読む)

トレンチ型絶縁ゲート半導体装置及びその製造方法

【課題】トレンチ型絶縁ゲート半導体素子と多結晶シリコンダイオードを同一チップ上に形成して性能を高める。

【解決手段】本発明では、半導体基板上の半導体層の主面に形成されたトレンチ型絶縁ゲート半導体素子のトレンチ溝の外側には、トレンチ溝に連なる多結晶シリコン層を形成する。また、トレンチ溝の外側には、前記トレンチ溝に連なる多結晶シリコン層とは別の多結晶シリコン層が形成され、この多結晶シリコン層には多結晶シリコンダイオードが形成され、そして、この多結晶シリコンダイオードが形成された多結晶シリコン層の膜厚が、前記トレンチ溝に連なる多結晶シリコン層の膜厚よりも薄くなるように形成することを特徴とする。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】製造効率を向上すると共に、内部回路の保護を的確に行うことを容易に可能にする。

【解決手段】ESD保護素子101の高濃度不純物領域121SH,120DH,122SHを、ゲート電極111G,112Gの下方に形成しない。高濃度不純物領域121SH,120DH,122SHを、半導体基板100の面(xy面)にて、少なくとも低濃度不純物領域121SL,121DL,122DL,122SLを介してゲート電極111G,112Gの側部に位置するように形成する。また、高濃度不純物領域121SH,120DH,122SHを、低濃度不純物領域121SL,121DL,122DL,122SLおよび不純物領域121SM,120DM,122SMよりも深い位置まで形成する。

(もっと読む)

半導体装置、及びその製造方法

【課題】半導体デバイスにおいて、ラッチアップ耐性を維持するとともに、チップ面積を縮小する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、トレンチ2が形成されたシリコン基板(Nウェル8、Pウェル9)と、トレンチ2の側面からシリコン基板表面にかけて、ウェルと同じ導電型で、当該ウェルより高濃度で形成された不純物領域(N型ウェルコンタクト拡散層領域4、P型ウェルコンタクト拡散層領域6)と、を備える。

(もっと読む)

静電気保護素子及びその製造方法

【課題】リーク電流の少ない静電気保護素子を提供する。

【解決手段】半導体基板100nと、半導体基板内に形成され、第1の導電型の不純物が拡散された第1のウェル101と、第1のウェル内に、第1のウェルの一部の領域を挟んで形成され、第2の導電型の不純物が拡散されたコレクタ領域110及びエミッタ領域112と、第1のウェル内に、前記エミッタ領域と分離する第1の分離領域102を挟んで形成され、第1のウェル内に拡散された不純物の濃度よりも高い濃度の、第1の導電型の不純物が拡散されたベース拡散領域114と、前記エミッタ領域下方から前記エミッタ領域と前記ベース拡散領域との間までの第1のウェル内の領域に形成され、第2の導電型の不純物が拡散された拡散領域103aとを備えた静電気保護素子。

(もっと読む)

半導体装置及びその製造方法

【課題】発熱に対して効率的に冷却を行うことができる、半導体装置を提供する。

【解決手段】半導体層の表面に形成された活性領域5,6と、N型の不純物を有する半導体から成るN型ゲート7Nと、P型の不純物を有する半導体から成るP型ゲート7Pと、N型ゲート7N及びP型ゲート7P及び活性領域5,6に接続された第1の金属配線13と、P型ゲート7P及びN型ゲート7Nに接続された第2の金属配線と15、第2の金属配線15に接続され、熱を外部に放出するための放熱部19とを含む冷却機構素子を備えた半導体装置を構成する。

(もっと読む)

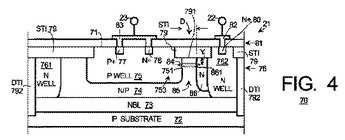

ESD保護デバイスおよび方法

関連するデバイスまたは回路24を保護する静電気放電(ESD)保護クランプ21、21’、70、700は、バイポーラ21、21’、70、700を備える。アバランシェ降伏が、上にある誘電体・半導体界面791から離れ、デバイス70、700のベース領域74、75の部分84,84以内に望ましく起こるように向かうベース75およびコレクタ86領域のドーパントを構成される。例えば、半導体ダイまたはウェハのトランジスタ21、21’、70、700の異なる方位配向のおかげで、ESDトリガ電圧の最大変化(△Vt1)MAXはベース・コレクタ間隔寸法Dの関数である。トリガ電圧一貫性および製造歩留まりが改良される。  (もっと読む)

(もっと読む)

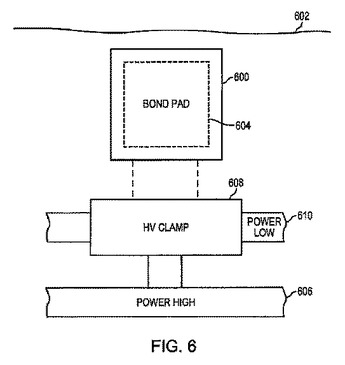

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

半導体装置、高周波集積回路、高周波無線通信システムおよび半導体装置の製造方法

【課題】SOS基板の異方性を低減して半導体装置のデバイス特性の面内均一性を向上する。

【解決手段】絶縁体基板101の主面上にSi層(またはSi基板)100を有する半導体装置10において、絶縁体基板101はサファイア基板101であり、絶縁体基板101の主面はc面である。サファイア基板101において異方性の少ないc面にSi層100を形成するので、Si層100上に形成された半導体装置10のデバイス特性の面内均一性を向上することができる。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】液晶ドライバ等の半導体集積回路装置においては、その形状が極端に細長いため、長手方向にプロセス特性がばらつくと、所望のデバイス特性が得られない。そこで、実製品ウエハにプロセスモニタ用の検査用素子を各種配置して、それらを測定することによって、プロセス特性のばらつきを監視している。しかし、ウエハ内におけるグローバルなプロセスばらつきは、比較的抽出しやすいものの、チップ内の局所的なプロセスばらつきの高精度の抽出は、大幅に検査用素子密度を上げない限り、困難であることが、本願発明者等により明らかにされた。

【解決手段】本願の一つの発明は、半導体集積回路装置の製造方法において、ウエハ上のチップ領域の近傍に複数のテスト素子領域を異なるピッチで配列し、プローブテストにおいて、それらを電気的に計測することにより、プロセスの局所的ばらつきをモニタするものである。

(もっと読む)

トランジスタ型保護素子および半導体集積回路

【課題】保護素子のターンオン電圧を決める制約を少なくする。

【解決手段】半導体基板1、Pウェル2、エミッタ領域5B、第1コレクタ領域6B、第2コレクタ領域8Bおよび抵抗性接続領域9を有する。第1および第2コレクタ領域6B,8Bは、エミッタ領域5Bと所定の距離以上だけ離れ、お互いの間も互いに離れており、その間が抵抗性接続領域9によって接続されている。抵抗性接続領域9は薄膜抵抗層によって代替できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 アバランシェ耐量が高く、保護する高耐圧トランジスタと同製造工程を用いて形成できる高耐圧ESD保護ダイオードを提供する。

【解決手段】 カソード領域8を構成するN型低濃度半導体基板1とアノード領域7を構成するP型低濃度拡散領域14から形成されるPN接合部の基板表面上に、ゲート酸化膜12を形成し、ゲート酸化膜12とフィールド酸化膜4にまたがって設けられたゲート電極13をゲートプラグ28を介してアノード電極20と電気的に接続することを特徴とする構造により、アバランシェ降伏時にPN接合における電界が緩和し、高アバランシェ耐量を得る。またフィールド酸化膜4の長さを変化させることで、耐圧を調整できる。

(もっと読む)

抵抗素子及びその製造方法

【課題】 従来のポリシリコン層を抵抗層とする抵抗素子は、抵抗素子のシート抵抗を例えば10MΩ/□以上に高くしたい場合、所望のシート抵抗が得られない問題があった。この原因は、製造工程中にポリシリコン層上の絶縁膜が帯電することが考えられ、このため設計値より2桁以上も低い値となってしまっていた。また、同一ウエハ内であっても抵抗素子毎に抵抗層のばらつきが大きくなる問題があった。

【解決手段】 ポリシリコン層を抵抗層とする抵抗素子において、抵抗層を被覆する絶縁膜の上に、保護層を設ける。保護層は金属層であり、抵抗素子の配線層や、電極等の金属層と同一金属層で形成できる。保護層は、ポリシリコン層の曲折部が露出するパターンに設ける。また、保護層に固定電位を印加する。固定電位に応じて、異なるシート抵抗が得られる。

(もっと読む)

半導体装置およびDC−DCコンバータ

【課題】半導体装置のソース領域とドレイン領域との間のオン抵抗を低減させる。

【解決手段】第1導電型のソース領域と第1導電型のドレイン領域とが表面に選択的に形成された第2導電型のベース層と、前記ベース層内に設けられ、前記ソース領域から前記ドレイン領域の方向に延在する素子分離層と、前記素子分離層の上側に設けられ、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ベース層の上側の少なくとも一部または前記素子分離層内の少なくとも一部に配置され、前記素子分離層の比誘電率よりも高い比誘電率を有する高誘電体層と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

集積回路構造、及び集積回路の製造方法

【課題】異なるフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、第1装置領域の第1部分と、第2装置領域の第2部分と、を有する半導体基板からなる。第1半導体フィンは半導体基板上にあり、第1フィン高さを有する。第2半導体フィンは半導体基板上にあり、第2フィン高さを有する。第1フィン高さは第2フィン高さより高い。

(もっと読む)

141 - 160 / 776

[ Back to top ]