Fターム[5F044KK16]の内容

ボンディング (23,044) | フェイスダウンボンディング用配線基板 (5,003) | 電極部 (1,724) | バンプ (984)

Fターム[5F044KK16]の下位に属するFターム

Fターム[5F044KK16]に分類される特許

141 - 160 / 234

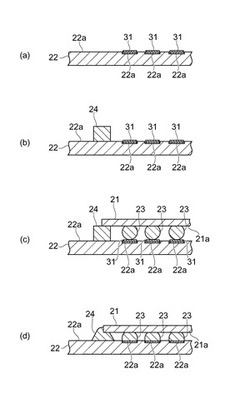

プリント回路板の製造方法、プリント回路板及び補強電子部品

【課題】プリント配線板に対する電子部品の接合強度を効率的に補強することが可能なプリント回路板の製造方法を提供する。

【解決手段】本発明の一実施形態に係るプリント回路板の製造方法は、電子部品21を実装するための実装領域を有するプリント配線板22を準備する準備工程(a)と、準備工程により準備されたプリント配線板22の実装領域に固形接着剤24を搭載する接着剤搭載工程(b)と、電子部品21を接着剤搭載工程を経たプリント配線板22に搭載する工程であって、電子部品21の電極形成面21sと交差する方向に該電極形成面21sを固形接着剤24に重ねて搭載する部品搭載工程(c)と、部品搭載工程を経たプリント配線板22をリフロー加熱する加熱工程(d)とを有する。

(もっと読む)

半導体素子パッケージと、その製造および実装方法

【課題】半導体素子パッケージを、そのソルダーボールを介して外部回路基板に実装する生産工程中に発生しうるシールリング部及び電気的な接続のための接続部における不良を防ぐことのできる半導体素子パッケージと、その製造および実装方法を提供する。

【解決手段】本願による半導体素子パッケージは、半導体素子と、前記半導体素子と対向するように配設される基板アセンブリーと、前記半導体素子と前記基板アセンブリーとを密着シールするソルダーシールリングと、前記基板アセンブリーのソルダーシールリングの外周縁に設けられる多数のソルダーボールと、を備え、前記ソルダーシールリングの融点が前記ソルダーボールの融点よりも高いことを特徴とする。

(もっと読む)

フリップチップ接合方法及び半導体装置の製造方法

【課題】 フリップチップ接合において、封止材内の泡残存を防止可能な半導体装置の製造方法を提供する。

【解決手段】配線基板10の端子面に、接合用金属30の表面の酸化膜を除去する作用を有する封止材用樹脂41を設ける工程と、配線基板10の端子11と半導体チップ20のバンプ21上の接合用金属30とを相対向配置した後、封止材用樹脂41の硬化開始条件を満たさない加熱条件で接合用金属30を溶融した後冷却固化させ、且つ接合用金属30が溶融してから冷却固化するまで一定の荷重を付与するようにして接合する工程と、次いで、硬化開始条件となる所定温度より低く且つ封止材用樹脂41を軟化させる温度条件下で封止材用樹脂41の脱ボイドを行う工程と、その後、前記封止材用樹脂を硬化する工程とを具備するフリップチップ接合方法。

(もっと読む)

ICチップ実装パッケージ

【課題】インナーリード剥がれやテープの波打ちを回避できるICチップ実装パッケージを実現する。

【解決手段】ICチップ実装パッケージ1は、インターポーザ4を介してフィルム基材2とICチップ3とが接続されている。インターポーザ4におけるフィルム基材2側の接続端子は、ICチップ3側の接続端子よりもピッチが大きく形成されている。フィルム基材2にデバイスホール8が設けられており、ICチップ3はデバイスホール8内に配設されている。フィルム基材2におけるインナーリード先端からデバイスホール8の縁までの距離Aは、10μm以上に設定される。

(もっと読む)

ICチップ実装パッケージ、及びこれを備えた画像表示装置

【課題】ICチップとインターポーザ基板との位置決めを効率よく実行できるICチップ(液晶ドライバ)実装パッケージを提供する。

【解決手段】本発明の一実施形態である液晶ドライバ実装パッケージ1は、インターポーザ基板4aを介してフィルム基材2と液晶ドライバ3とが接続している。液晶ドライバ3は、インターポーザ基板4aとの対向面に第1アライメントマーク11を有し、インターポーザ基板4aは、液晶ドライバ3との対向面に第2アライメントマーク12を有している。第1アライメントマーク11と第2アライメントマーク12とを、インターポーザ基板4aの上記対向面に対して垂直方向からみると、互いが、液晶ドライバ3とインターポーザ基板4aを貼り合せる際の貼り合わせ位置として許容できる範囲の距離ほど離間されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 フェースダウン方式で搭載された半導体構成体を有し、且つ、下面側に複数の半田ボールを有する半導体装置において、インターポーザを用いない構造とする。

【解決手段】 ソルダーレジスト等からなる下層絶縁膜1の上面には配線2が設けられている。半導体構成体6は、その突起電極12が配線2にボンディングされていることにより、配線2上にフェースダウン方式により搭載されている。半導体構成体6と配線2を含む下層絶縁膜1との間およびその周囲にはアンダーフィル材13が設けられている。半導体構成体6、アンダーフィル材13および配線2を含む下層絶縁膜1の上面には封止材14が設けられている。配線2の接続パッド部下には半田ボール5が設けられている。この場合、両面配線2構造で上下導通部を有する比較的高価なインターポーザを用いていないため、コストを低減することができ、また薄型化することができる。

(もっと読む)

半導体パッケージ

【課題】簡便に形成でき、基板同士を接合する際に加わる力によって破壊されにくいバンプ構造体を備えた半導体パッケージを提供する。

【解決手段】センサ基板電極5の直下に接続用キャビティ7を設け、バンプ4がセンサ基板電極5を接続用キャビティ7方向に押し曲げてバンプ4とセンサ基板電極5とが接続される構成としたので、製造ばらつきによりバンプ4が所定の高さより上回っていても、所定高さを超えた分が接続用キャビティ7に逃げ、バンプ4からセンサ基板2や窓基板1への応力が低減されて、センサ基板電極5や窓基板電極3やその周辺部位にクラック等の破壊を引き起こすことがない。またセンサ基板電極5を弾性体によって構成したため、弾性力によってセンサ基板電極5がバンプ4側に付勢され、センサ基板電極5とバンプ4とが確実に接続される。

(もっと読む)

フラックスドッティングツール

【課題】ソルダボールが形成されるパッドの表面にフラックスをドッティングするための半導体製造工程のフラックスドッティングツールを提供する。

【解決手段】下方に弾性力を提供する弾性部材を含み、ドッティングしようとするフラックスに接触するフラックスピン100と、フラックスピン100が複数固着されるストッパー200と、ストッパー200が固定されるハウジング300と、フラックスピン100が貫通する結合孔402を有し、フラックスピン100が下方に落ちないようにハウジング300に固定されるカバー400とを含んでなる。

(もっと読む)

半導体装置の製造方法

【課題】 アンダーフィル用樹脂内のボイドの発生を抑制し、信頼性の高いフリップチップ実装を実現した半導体装置の製造方法を提供する。

【解決手段】 本発明に係る半導体装置の製造方法は、半導体チップ20の一方の主面22に2次元状に形成された複数の電極24を、基板30上の対応する導電性領域32、34に接合するステップと、真空雰囲気中で、半導体チップの一方の主面と基板との間にアンダーフィル用樹脂40を供給するステップと、アンダーフィル樹脂40が供給された半導体チップおよび基板を大気中に露出するステップとを有する。

(もっと読む)

電子回路モジュールの製造方法

【課題】回路基板の同一表面上に半田プリコート層および金属めっき層を混在させて形成し、半導体素子およびチップ部品の接合性を容易にすることができる電子回路モジュールの製造方法を提供すること。

【解決手段】本発明の電子回路モジュール1の製造方法は、接続端子3、4の形成工程A、第1の接続端子3への半田プリコート層11の形成工程B、めっき用レジスト膜20による第1の接続端子3の被覆および第2の接続端子4の露出工程C、第2の接続端子4への金属めっき層10の形成工程D、加熱したバンプ6をめっき用レジスト膜20に埋没させて第1の接続端子3に当接させる工程E、バンプ6と第1の接続端子3との接合工程F、および、第2の接続端子4とチップ部品8との接合工程Gを備える。

(もっと読む)

半導体装置

【課題】アンダーフィル樹脂の注入性を向上させ、形成されるフィレットをより小さくすることができる半導体装置を提供する。

【解決手段】チップ1の周縁部にバンプより小さなチップ側ダミーバンプ4を形成し基板2にフリップチップ実装することにより、ダミーバンプ4と基板2の間の隙間とダミーバンプ4間の間隙が小さくできる。このため、この間隙により発生する毛細管現象で、アンダーフィル樹脂の注入がし易くなり、塗布量を少なくできる。

(もっと読む)

配線基板及びそれを用いた半導体装置ならびにその製造方法

【課題】配線基板にコネクタを装着した場合に、コネクタの導電パッドと配線基板の端子とを確実に接触させ、固定できる配線基板を提供する。

【解決手段】絶縁性基材2と、絶縁性基材2の表面に形成された導体配線3と、導体配線3の長手方向を横切って導体配線3の両側の絶縁性基材上2の領域に亘り形成された第1の突起電極4と、絶縁性基材2の表面に形成され、導体配線3と接続された端子5と、端子5の表面に形成された第2の突起電極6aとを備える。第2の突起電極6aに、端子5の表面が露出されるように形成された開口部7aを備える。

(もっと読む)

素子搭載用基板、半導体モジュールおよび携帯機器

【課題】ハンドリング性を向上できるとともに接続信頼性を確保できる素子搭載用基板を提供する。

【解決手段】素子搭載用基板100は、基材1に設けられたパッド電極4と、パッド電極4の上面部の少なくとも一部に開口部5を有するように基材1を覆う絶縁層6と、パッド電極4の上の開口部5内に設けられた融着層7と、を備え、融着層7の表面が開口部5の上端よりも低いことを特徴とした。

(もっと読む)

マウントするために半導体構造体を準備するプロセス

【課題】マウントのために半導体構造体を準備するプロセスを提供すること。

【解決手段】支持体70にマウントするために半導体構造体30を準備するプロセスが開示される。この方法は、支持材料110が、半導体構造体30内に形成された表面によって定められるボイド50を実質的に充填するようにし、支持材料110が、支持体70にマウントされるとき、半導体構造体30を支持するために十分に固化するようにする、ステップを含む。

(もっと読む)

半田ボールおよびその製造方法

【課題】半田付けの際にコアの溶融を防止できると共に、機械的な衝撃や熱応力がかかった場合でも、コアが半田から剥離しにくい半田ボールおよびその製造方法を提供する。

【解決手段】結晶粒3が間隙を有した状態で集合した多孔質構造からなるコア2と、該コアの表面を被覆するとともに該結晶粒3の間隙の内部まで含浸した半田7とを有することで、コア2と半田7が強固に密着し、機械的な衝撃や熱応力がかかった場合でも、半田7がコア2から剥離しにくい半田ボール1となる。

(もっと読む)

接合用基板と基板の接合方法と半導体装置

【課題】 半導体装置を配線基板に実装するに際して、電極同士のフリップチップ接合と、半導体装置と配線基板との樹脂封着を同時に一括して確実に行う。

【解決手段】 突出して並設された電極を有する下側基板1と上側基板2とが対向して該電極同士が接合される接合用基板100であって、該電極10、20は、柱状をなす金属製のバンプからなり、溝状隙間3を介して封止樹脂からなる樹脂層11、21に周りを取り囲まれているように接合用基板100を構成する。

(もっと読む)

ホールセンサ搭載基板

【課題】半田を使用しない小型のアイリス用のホールセンサ搭載基板を提供する。

【解決手段】GaAsからなるホール素子ベアチップ3を直接フレキシブル基板1に搭載して、そのホール素子ベアチップ3をシリコーンゴム6などで樹脂封止したものである。

(もっと読む)

実装構造体、電気光学装置及び電子機器

【課題】電子部品の端子間、及び電極間における短絡防止を図ることが可能な実装構造体等を提供する。

【解決手段】実装構造体は、基板と、基板上に設けられた電極と、導電性粒子を有し、少なくとも電極を覆う位置に設けられた接着剤と、電極に対応する位置に設けられ導電性粒子を介して電極に電気的に接続される端子を有し、接着剤を通じて基板上に実装された電子部品と、を備え、電極、導電性粒子及び端子のうち少なくとも1つは磁性を有する。これにより、その製造過程において、導電性粒子は、その磁力の働きによって電極と端子の間に集まる。その結果、導電性粒子を通じて電極と端子の電気的な接続を確実なものとすることができる。また、これにより、隣接する電極間及び隣接する端子間には導電性粒子が殆ど存在しなくなり、隣接する電極間及び隣接する端子間等にて短絡が生じるのを防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】低誘電率膜の破壊と鉛フリー半田からなるバンプの破壊を両方とも防ぐことができる半導体装置を得る。

【解決手段】低誘電率膜を含む半導体チップと、鉛フリー半田からなるバンプとを有する半導体パッケージと、半導体パッケージがバンプを介してフリップチップ接合された配線基板と、半導体パッケージと配線基板の間に充填されたアンダーフィル樹脂とを備え、アンダーフィル樹脂は、ガラス転移温度が125℃以上であり、かつ125℃での熱膨張係数が40ppm/℃未満であり、かつ25℃での弾性率が9GPa未満である。

(もっと読む)

素子、素子の製造方法、基板、基板の製造方法、実装構造体、実装方法、発光ダイオードディスプレイ、発光ダイオードバックライトおよび電子機器

【課題】基板上に素子を実装する場合に、基板上の配線と素子とを確実に電気的に接続することができ、しかもバンプのさらなる微細化、多ピン接続が可能な実装構造体および実装方法を提供する。

【解決手段】配線基板10の配線12上に弾性体からなる凸部13の少なくとも先端部の表面が導電膜14で被覆された構造の突起部15を少なくとも一つ形成する。素子20上にバンプ22を形成する。配線基板10上に接着剤30を塗布し、この接着剤30に素子20を仮実装する。素子20を配線基板10に対して加圧することにより、配線基板10上の突起部15の少なくとも先端部を素子20のバンプ22に埋没させる。その後、接着剤30を硬化させ、素子20と配線基板10とを接着固定する。

(もっと読む)

141 - 160 / 234

[ Back to top ]