Fターム[5F044QQ02]の内容

ボンディング (23,044) | ワイヤレスボンディング用半導体チップ (2,288) | バンプ電極 (1,821) | 形状・配置 (453)

Fターム[5F044QQ02]に分類される特許

61 - 80 / 453

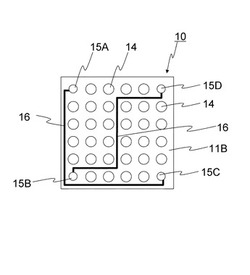

半導体パッケージ、配線基板、及びリフロー炉

【課題】複数の金属ボール端子を備えた半導体パッケージをリフロー法により配線基板に実装する際に、金属ボール端子の溶融状態を正確に把握する。

【解決手段】複数の金属ボール端子のうち四隅の金属ボール端子15A〜15Dはその他の金属ボール端子14よりも相対的に径が小さい導通検出用の金属ボール端子であり、導通検出用の金属ボール端子15A〜15Dの径が式(X)を充足し、互いに対角にある2個の導通検出用の金属ボール端子15Aと15C、15Bと15Dが配線16を介して接続されている。

d2≧d1−x・・・(X)

(上記式中、d1は導通検出用ではない金属ボール端子の径、d2は導通検出用の金属ボール端子の径、xは配線基板上に半導体パッケージを載置した時点に対する金属ボール端子の溶融後の半導体パッケージの沈み込み量を各々示す。)

(もっと読む)

電子部品の実装方法、電子部品の製造方法および電子部品、電子部品の製造装置

【課題】加熱時に電子部品に反りが発生した場合でも、電子部品の電極をプリント基板の電極に確実に接合することができる電子部品の実装方法、電子部品の製造方法および電子部品、電子部品の製造装置を提供する。

【解決手段】電子部品1は、電子部品1を形成する複数の電極3a〜3eが格子状に配列された基板本体2を備え、複数の電極3a〜3eのうち、基板本体2の反りが大きくなる外側の位置には、所定の高さを有する電極3a及び電極3eを有し、基板本体2の反りが小さくなる中央の位置には、加圧ヘッド4による加圧により外側の電極3a、3eよりも半田ボールの高さが低く潰された電極3b、3c、3dを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体パッケージを配線基板にフリップチップ接合した半導体装置において、接合部での電極間短絡と応力集中を防止し、リワークが容易な構成とする半導体装置及びその製造方法を提供する。

【解決手段】半導体パッケージ11を配線基板21にフリップチップ接合した半導体装置1において、半導体パッケージと配線基板を接合する突起電極30を有し、突起電極は、はんだ電極32と、はんだ電極を被覆する熱収縮モールド31を含む。

(もっと読む)

マクロピンハイブリッド相互接続アレイ及びその製造方法

【課題】局所歪みが少なく、今日製造者が利用できる従来の取り付け方法に適合可能であるインターポーザにCZT及び/又はCdTeを相互接続するための構造を提供すること。

【解決手段】マクロピンハイブリッド相互接続アレイ(10)は、結晶アノードアレイ(18)及びセラミック基板(14)を備える。アレイ(18)及び基板(14)は、大きい高さ対幅のアスペクト比を有する相互接続(12)幾何形状を用いて共に接合される。相互接続(12)を結晶アノードアレイ(18)に固定する継手は、無はんだである。

(もっと読む)

電子部品、電子機器及びそれらの製造方法

【課題】先アンダーフィル方式のフリップチップボンディングにおいて、接続不良が少ない電子部品を提供する。

【解決手段】電子部品20の基板21上に形成されたフリップチップボンディング用の突起電極24の上面に形成された窪み26と、窪み26に埋め込まれたフラックス25と、突起電極24の外側の基板21上に形成され、突起電極24を突起電極24上面まで埋め込む接着材22とを有する。ボンディングの際にフラックスが蒸発して接合面の気圧が上昇し、溶融した接合樹脂の接合面への侵入が防止される。このため、接合面に絶縁性接着材の皮膜が形成されず接続不良を生じない。

(もっと読む)

半導体装置の構造および製造方法

【課題】挟ピッチかつ高い接続信頼性を確保した簡易な構造の半導体装置、および製造方法を提供する。

【解決手段】半導体素子1の電極端子1b上に突起状電極1aを形成する。突起状電極1aよりも大きくし、位置を合わせた転写用の金型4に、粘着層5を供給し半田粒子3を付与する。金型4と半導体素子1の対向する位置を合わせ、加熱・加圧して半田粒子3を突起状電極1a上に付与、金型4を引き剥がして半導体素子1を個片化する。半導体素子1の突起状電極1aに対向して回路基板2の電極端子2aの位置を合わせて、加熱、荷重し半導体素子1を回路基板2上へ搭載する。半導体素子1の端部の回路基板2との距離が最も大きな電極同士でも、微細半田が鼓状に伸びて接合し平行度の悪化を吸収する。端部電極の熱応力集中を微小半田接合体(半田接合部3c)が受けて、電極直下の脆弱な絶縁膜の熱応力を低減して剥離や亀裂を防ぎ、高い接続信頼性を確保する。

(もっと読む)

半導体装置及びその製造方法

【課題】超音波接合する場合に、半導体チップに設けられたバンプの位置にかかわらず、全てのバンプが確実に接合されるようにし、全てのバンプにおいて十分な接合強度が得られるようにする。

【解決手段】半導体装置の製造方法を、複数のバンプ1(1A,1B)を有する半導体チップ2を形成する工程と、半導体チップ2の複数のバンプ1と実装基板の表面電極とを超音波接合する工程とを含むものとし、半導体チップ形成工程において、超音波接合する際に超音波振動方向に直交する端辺となる半導体チップ2の端辺の近傍領域5Aに設けられる第1バンプ1Aの径が端辺近傍領域5A以外の領域5Bに設けられる第2バンプ1Bの径よりも大きくなっている半導体チップ2を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、各バンプの先端位置、即ち、各バンプの突出量がばらついていても、実装基板に接合した場合に、全てのバンプにおいて十分な接合強度が得られるようにする。

【解決手段】半導体装置を、半導体素子3と、半導体素子3の表面側に位置し、半導体素子3の裏面3Aとの間の距離が第1の距離である第1バンプ形成面4(4E)上に形成された第1バンプ1(1E)と、半導体素子3の表面側に位置し、半導体素子3の裏面3Aとの間の距離が第1の距離よりも長い第2の距離である第2バンプ形成面4(4A)上に形成され、第1バンプ1(1E)よりも径が大きい第2バンプ1(1A)とを備えるものとする。

(もっと読む)

電子部品の実装構造体および電子部品の製造方法

【課題】アウトガスによる影響を防止することで電子部品特性の低下を防止可能な、電子部品の実装構造体、及び電子部品の製造方法を提供する。

【解決手段】接続電極33,34を有する基材3に電子部品1を実装する電子部品1の実装構造体2である。電子部品1は、所定の機能を有する機能片11と、機能片11に電気的に接続される導電部を含む被覆膜25,26により表面が覆われ、凹部を有する樹脂突起部24と、凹部に配置された接着材27,28を有する。接着材27,28は、被覆膜25,26における導電部を接続電極33,34に導電接触させた状態に電子部品1を前記基材3に実装する。

(もっと読む)

半導体チップの実装方法

【課題】高密度実装では占有面積の低減と低背化がキーとなっている。半導体デバイスを積層化した構造は高密度実装に適しているが、強度確保のための樹脂インターポーザの厚さ、上下のデバイスを電気接続する導電ボールの大きさ、ワイヤボンディングのための空間確保などにより、低背化が制限されていた。このための半導体デバイスを低背化して実装可能とする技術を提供する。

【解決手段】樹脂よりもヤング率が大きい半導体インターポーザの採用、電気接続を複数の微小な金属塊13から成る導電路20で形成、フリップチップ構成の採用などにより、低背化が達成された。また、前記金属塊の形状、大きさ、配置などを最適化することにより、積層化プロセスが容易になった。

(もっと読む)

半導体デバイスの実装方法

【課題】半導体デバイスを積層化した構造で、低背化が可能な手段を提供する。

【解決手段】半導体デバイス10の導電体12に複数の微小な金属塊13を形成、樹脂よりもヤング率が大きい半導体インターポーザ15の導電体17に複数の微小な金属塊18を形成しフリップチップ接続することで、導電体同士が微少な金属塊で接続されることになり低背化が達成された。また、積層化プロセスが容易になるように、前記金属塊の形状、大きさ、配置などを最適化した。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】歩留まりを低下させることなく、複数の半導体装置を一括形成することが可能な方法を提供すること。

【解決手段】支持板19上に金属膜21を形成する工程と、この金属膜21上に、係合部を有する複数の接続プラグ18を形成する工程と、それぞれの接続プラグ18の係合部内に、複数の半導体チップ13にそれぞれ設けられた各突起電極17を挿入し、かつ接触させることにより固定するとともに、複数の半導体チップ13を絶縁樹脂15−1で覆う工程と、少なくとも突起電極17を接続プラグの係合部内に挿入、接触させた後に、絶縁樹脂15−1を硬化させる工程と、少なくとも金属膜21をエッチングすることにより、接続プラグ18に電気的に接続された配線パターン16を形成する工程と、配線パターン16の一部に電気的に接続されるとともに、配線パターン16の他の部分とはソルダーレジスト膜14により絶縁されるように半田ボール12を形成する工程と、それぞれの半導体チップ13の周囲およびその上方の絶縁樹脂15−1を切断する工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体パッケージにおいて長期接続信頼性を向上させ、エレクトロマイグレーション耐性を改善する。

【解決手段】半導体素子1の電極パッドと基板21上の電極パッド20とをはんだボールによって接続する。はんだボールは、金属製コア部11と、金属製コア部11の周囲に設けられ、前記コア部11よりも剛性が低く融点が低いはんだ部10とで構成されている。はんだボールを半導体素子1にリフローによって接続する。その後、半田ボールが付いた半導体素子1と基板21を超音波にて接続し、基板21側において、金属コア11と電極20を直接接続する。これによって熱ストレスの少ない、かつ、抵抗の小さい接続を可能とする。

(もっと読む)

電極、電子部品及び基板

【課題】電極本体と電子部品又は基板との接合面積の低下を抑制できる電極、電子部品及び基板の提供を課題とする。

【解決手段】本発明は、電子部品12にはんだ付けされて設けられ、電子部品12が基板13に実装される際に、基板12にはんだ付けされる電極10である。この電極10は、電子部品12及び基板12にはんだ付けされる柱状の電極本体11を有している。電極本体11が電子部品12又は基板13にはんだ付けされる際に、電極本体11の接合面11a,11bと電子部品12又は基板13との間におけるはんだ14内に発生する空気溜まり15内の空気15aを排出する空気排出手段としての溝20を備えている。

(もっと読む)

半導体集積回路装置

【課題】フリップチップ構造を有する半導体集積回路装置において、パッドからチップ内部素子へ加わる応力の影響に起因するタイミング信頼性の劣化を低コストで防止する。

【解決手段】フリップチップ構造を有する半導体集積回路装置において、応力の影響を受ける半導体チップ101の外周列におけるパッド102の構造及び配置位置等について、応力の影響に起因するLSIの動作不具合が発生しにくいように予めレイアウトする。

(もっと読む)

半導体デバイス実装体とその製造方法

【課題】半導体デバイスを基板に実装した後に熱負荷が加えられても位置ずれが生じない半導体デバイス実装体を提供する。

【解決手段】基板2には3つの電極4a,4b,4cが設けられており、光半導体素子3には、基板2の電極4a,4b,4cと対向する位置に電極5a,5b,5cが設けられている。シリコン基板2の電極4a,4bと光半導体素子3の電極5a,5bは金製のスタッドバンプ7によって接合されており、シリコン基板2の電極4cと光半導体素子3の電極5cは、半田6によって接合されている。スタッドバンプ7は予めシリコン基板2の電極4a,4bに設けられていたものであり、このスタッドバンプ7の先部が、光半導体素子3の金メッキされた電極5a,5bに固相接合されている。

(もっと読む)

3次元半導体集積回路の製造方法及び3次元半導体集積回路

【課題】エッジ配線を用いた3次元半導体集積回路の製造方法を提供する。

【解決手段】3次元半導体集積回路の製造方法は、第1の半導体チップ10の少なくとも一つのエッジを含む表面にインクジェット機構30を用いて第1の配線14を形成する工程と、第2の半導体チップ20の少なくとも一つのエッジを含む表面にインクジェット機構30を用いて第2の配線24を形成する工程と、第1及び第2の配線14,24の位置に基づき第1の半導体チップ10と第2の半導体チップ20とを積層することにより、第1の配線14と第2の配線24とを導通させる工程と、を含む。

(もっと読む)

3次元でパッケージされた集積回路に対するダイ間結合の間の静電放電ダメージへの感受性の低減

本発明は、電子集積回路パッケージの製作、より具体的には3次元でパッケージされた集積回路を製造する際の静電放電ダメージの軽減に関する。一実施形態では、第2層ダイが第1層ダイと接触して配置されるとき、第2層ダイおよび第1層ダイ上の他の信号導電バンプおよびパワー導電バンプが電気的に接触する前に、第2層の基板と電気的に結合された第2層の周辺部付近の導電バンプが、第1層の基板と電気的に結合された第1層の対応する導電バンプと接触する。  (もっと読む)

(もっと読む)

圧電デバイス及び圧電デバイスの製造方法

【課題】小型化かつ、接続信頼性の向上を図った圧電デバイス及び圧電デバイスの製造方

法を提供することを目的としている。

【解決手段】本発明の圧電デバイス10は、接続用電極パッド64を備えた圧電振動片6

0と、前記接続用電極パッド64と電気的に接続すると共に前記圧電振動片60を支持す

る電極パターン50を備えた半導体デバイス40とを備え、前記電極パターン50は一方

の端部を前記半導体デバイス40のパッドと接続させ、他方の端部を前記接続用電極パッ

ド64と接続させ、前記一方の端部と前記他方の端部の間に前記半導体デバイス40の一

方の主面43から離反する方向に立ち上がる屈曲部52を形成し、前記一方の主面43と

前記電極パターン50の間の屈曲部52に樹脂を形成したことを特徴としている。

(もっと読む)

半導体装置および半導体装置の接続体

【課題】突起電極を高くすることなくその径を大きくとることができ、かつ、突起電極間や突起電極と半導体基板上の半導体回路との絶縁を確保することができる半導体装置、および、この半導体装置が接合された接続体を提供すること。

【解決手段】半導体基板1上に形成された複数の外部接続電極2と、前記外部接続電極2の一部を開口部4から露出させて形成されたパッシベーション膜3と、前記パッシベーション膜3の前記開口部4上に形成された下地電極5と、前記下地電極5上に形成されたはんだ突起電極6とを備え、前記はんだ突起電極6の表面が、前記半導体基板1の表面から略同じ高さに位置する平坦面を形成し、前記はんだ突起電極6の周囲を囲むように形成された枠状樹脂膜7が、前記パッシベーション膜3上に形成された面状樹脂膜8と一体化されている。

(もっと読む)

61 - 80 / 453

[ Back to top ]