Fターム[5F044RR19]の内容

ボンディング (23,044) | ワイヤレスボンディング関連事項 (2,154) | 容器・封止 (1,675) | 封止方法 (545)

Fターム[5F044RR19]に分類される特許

281 - 300 / 545

液状封止樹脂組成物及びそれを用いた半導体装置の製造方法

【課題】 フリップチップパッケージの端子接合と封止をリフロー加熱により一括に行うことができ、高接続信頼を有する液状封止樹脂組成物及びそれを用いた半導体装置の製造方法を提供する。

【解決手段】 リフロー加熱によりフリップチップパッケージの端子接合と封止を同時に行うことができる液状封止樹脂組成物において、リフロー加熱が半田の融点よりも低い温度のリフロー予備加熱温度と半田の融点よりも高い温度のリフロー本加熱温度を有し、前記液状封止樹脂組成物の粘弾性測定における粘度が、リフロー予備加熱時の温度範囲で1Pa・s以下で、リフロー本加熱時のピーク温度でのゲルタイムが30s以下である液状封止樹脂組成物。

(もっと読む)

電子部品の実装方法及び実装装置

【課題】 弾性体を用いた熱圧着の利点を活かしながら、ボイドの発生を最小限に抑え、接続不良の発生を大幅に低減することが可能な電子部品の実装方法及び実装装置を提供する。

【解決手段】 配線基板11上に接着剤(例えば異方導電性接着フィルム13)を介して電子部品(ICチップ12)を配置し、弾性体からなる圧着部4を備えた熱圧着ヘッド2により電子部品であるICチップ12を加圧するとともに、異方導電性接着フィルム13を加熱し、ICチップ12を配線基板11に熱圧着する。この時、異方導電性接着フィルム13の温度が異方導電性接着フィルム13に含まれる結着樹脂13aの硬化開始温度Kに到達する前に、熱圧着ヘッド2による加圧力が所定の圧力(ボイドを追い出すのに必要な圧力)に到達するように設定する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子を回路基板に実装する際に、半導体素子と回路基板の間の接着層を、回路基板に向かって十分に裾が拡がった形状に形成する。

【解決手段】半導体装置の製造方法は、半導体素子(13)を実装する回路基板(11)上の、前記半導体素子の実装位置の外周にあらかじめ第1の接着層(12)を形成しておく。また、前記半導体素子の実装面に、あらかじめ第2の接着層(15)を形成しておく。前記半導体素子を前記回路基板上に配置し、前記第1の接着層と前記第2の接着層とを溶融・一体化してフィレット(16)を形成する。

(もっと読む)

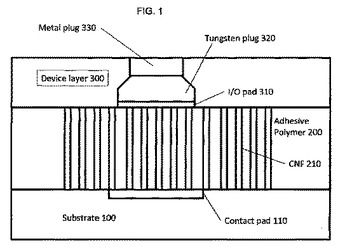

ナノ構造体による隣接層の接続および接合

2つの導電面または導電層と、これら2つの導電面または導電層の間に電気的または熱的接続部を生成するように2つの導電面または導電層に接合されたナノ構造体アセンブリとを備える装置、およびその製造方法。  (もっと読む)

(もっと読む)

電子部品の実装装置及び実装方法

【課題】所謂アンダーフィル樹脂の先入れを行う電子部品の実装工程において、当該樹脂中に残存するボイドの低減を可能とする実装装置或いは実装方法を提供する。

【解決手段】チップを保持しZ軸に駆動可能な電子部品保持手段と、基板を支持するXYテーブルとを有する実装装置に対して、該XYテーブル上に上面が開放され下面が当該テーブルに繋がり基板支持領域を区画する略箱状の隔壁、該XYテーブルとは独立してZ軸に駆動可能であって該隔壁の開放部を閉鎖する蓋部材、及び電子部品保持手段、XYテーブル、隔壁及び蓋部材によって構成される空間の圧力を制御する圧力制御手段を付与する。

(もっと読む)

半導体装置及びその製造方法

【課題】積層配置される半導体素子に於ける突出部に対して、ワイヤボンディング時に生じる撓みを抑制するとともに、半導体装置として大形化を招くことのない支持部材を有する、半導体装置及びその製造方法を提供することを目的とする。

【解決手段】上記の課題を解決するため、本発明によって提供される半導体装置は、電極端子が配設された支持基体と、支持基体上に搭載された中間部材と、一部が中間部材により支持されて、支持基体上に配設された半導体素子と、半導体素子の電極端子に対応して、支持基体上あるいは前記中間部材上に配設された凸状部材とを具備し、半導体素子の電極端子と前記支持基体上の電極端子が、ボンディングワイヤにより接続されてなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の信頼性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】配線基板3と、配線基板3にフェースダウンで取り付けられた半導体チップ1と、配線基板3と半導体チップ1との間にある接着剤5と、配線基板3と半導体チップ1の側面とに接する樹脂層15と、を備え、樹脂層15に含まれる不純物(Cl-)濃度は2mg/L以下である。このような構成であれば、接着剤5に水分が直接付着することを防ぐことができ、また、湿度により樹脂層15から溶け出す不純物量を少なくすることができる。これにより、水分及び不純物がボイドを伝って半導体装置の内部へ入り込むことを防ぐことができる。

(もっと読む)

半導体チップの実装方法及び半導体装置

【課題】簡単な構成でありながら半導体チップを所定の湾曲形状にした状態で基板に取り付ける。

【解決手段】リジット基板13の相対する一対の縁13a,13bに沿って、径サイズが異なる3種類のバンプ11a〜11cをライン状に配列して接合する。縁13aの中心部に径サイズが最も小さいバンプ11cが縁13aに沿って2個並列され、これらの外側にバンプ11bが、更にその外側に最も径サイズが大きいバンプ11aが配置され、縁13aに沿って合計6個のバンプ11a〜11cが配列される。縁13bについても縁13aと同様にバンプ11a〜11cが配列される。リジット基板13の上方から可撓性を有する固体撮像素子12を被せ、固体撮像素子12の中央部に圧縮空気を吹きつけて凸状に湾曲させながら、固体撮像素子12の電極をバンプ11a〜11cに接合し、半導体装置10を得る。

(もっと読む)

回路部材の実装方法

【課題】使用する熱硬化型接続材料の硬化温度の高低に関わらず、ICチップ等の回路部材を実装後の基板の反り変形を十分に抑制できると共に、十分に高い接続信頼性を有する回路接続体を製造可能な回路部材実装方法を提供すること。

【解決手段】本発明に係る回路部材実装方法は、基板1とこの基板1に実装される回路部材3との間に熱硬化型接続材料2を介在させた後、加熱しながら基板1と回路部材3とを圧着することによって、熱硬化型接続材料2を硬化させ、基板1の電極1aと回路部材3の電極3aが電気的に接続されるように基板1と回路部材3とを接着する熱圧着工程と、この熱圧着工程を経て得られた回路接続体を再び加熱する再加熱工程とを備える。

(もっと読む)

異方性導電材料、接続構造体及びその製造方法

【課題】ICチップやフレキシブル配線を配線基板に異方性導電材料を介して接続する際に、各バンプ間やライン状端子間で導通抵抗を相違させないような異方性導電材料を提供する。

【解決手段】導電性粒子が絶縁性バインダに分散されてなる異方性導電材料は、最低溶融粘度[η0]が1.0×102〜1.0×106mPa・secであり、且つ以下の式(1)を満足する。

1<[η1]/[η0]≦3 (1)

式(1)において、[η0]は異方性導電材料の最低溶融粘度であり、[η1]は最低溶融粘度を示す温度T0より30℃低い温度T1における溶融粘度である。

(もっと読む)

プラズマ処理装置及び半導体装置の製造方法

【課題】半導体チップ等の素子を短時間で効率よくプラズマ処理する。

【解決手段】プラズマ洗浄装置1は、真空チャンバ11と、真空チャンバ11にガスを供給するガス導入口13と、真空チャンバ11からガスを排出するガス排出口15と、真空チャンバ11の内部に配置され、半導体チップ19を載置する下部電極23と、下部電極23の上部に配置され、ガス導入口13から供給されたガスに対し半導体チップ19の上部空間を遮蔽するとともに、ガス導入口13によって供給されるガスを半導体チップ19に誘導する品種対応治具17とを備える。

(もっと読む)

電子部品の実装方法及び回路基板

【課題】 ノンフローアンダーフィル工法において、アンダーフィルの偏りを低減することができ、絶縁樹脂の充填不足や絶縁樹脂のはみ出しによる外観の悪化を低減することができる電子部品の実装方法を提案する。

【解決手段】 回路基板1は、ガラス−エポキシ、紙−フェノール等の樹脂、またはセラミック等で構成された基材2上に、半導体装置の端子と導電接続される銅等の導電金属で構成された接続パッド4と、接続パッド4とその他の配線導体以外の、基材2上を被覆するレジスト膜3が形成されている。そして、この回路基板1上の、半導体装置の外形を示す点線6よりも内側部分の略中央に略円形の凹凸部5が形成されている。

(もっと読む)

液状エポキシ樹脂組成物及び半導体装置

【課題】 樹脂成分の低揮発化による封止樹脂中に発生するボイドの対策、半導体チップと半導体チップを接合する構造(COC構造)において半田接続性が良好で信頼性、作業性に優れ、半導体装置の製造工程が簡略化可能な半導体封止用液状エポキシ樹脂組成物及び該組成物で封止された半導体装置を提供する。

【解決手段】(A)液状ナフタレン型エポキシ樹脂又は液状ジシクロペンタジエン型エポキシ樹脂の1種又は2種以上から選択される液状エポキシ樹脂を70〜100質量%含有する液状エポキシ樹脂、(B)3,3’,4,4’−ベンゾフェノンテトラカルボン酸二無水物を30〜80質量%以上含有する酸無水物硬化剤、(C)無機質充填剤を含有してなる液状エポキシ樹脂組成物、更には(D)フラックス剤を含有してなる液状エポキシ樹脂組成物により達成される。

(もっと読む)

フリップチップパッケージの製造方法

【課題】本発明は、ウエハーに溶液状態の異方性導電接着剤(ACA)および非導電性接着剤(NCA)を2重層に直接コーティングすることによってフリップチップパッケージを製造することができるウエハーレベルフリップチップパッケージの製造方法を提供する。

【解決手段】(a)非はんだバンプが形成されたウエハーの上部に絶縁高分子樹脂、硬化剤および有機溶媒を含む非導電性混合溶液を塗布・乾燥して非導電層を形成する工程と、(b)前記非導電層の上部に絶縁高分子樹脂、硬化剤、有機溶媒および導電性粒子を包含する導電性混合溶液を塗布・乾燥して異方性導電層を形成する工程と、(c)前記非導電層および異方性導電層が形成されたウエハーをダイシングして個別の半導体チップを製造する工程と、(d)前記半導体チップを基板上の電極と整列してフリップチップ接続する工程とを含めてなるフリップチップパッケージの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】先ダイシング法と、フリップチップボンディングを採用した実装プロセスとを連続して行うことが可能であり、製造プロセスの簡素化と、製品中にボイドが無く信頼性の向上に寄与しうる半導体装置の製造方法を提供する。

【解決手段】回路表面に接着フィルム3が接着され、かつ該回路毎に区画する溝6が形成されてなるウエハ1の回路表面側に表面保護シートを貼着する工程、上記ウエハの裏面研削をすることで個々のチップへの分割を行う工程、個別のチップを接着フィルムとともにピックアップし接着フィルムを介して、チップ搭載用基板にダイボンドする工程、およびダイボンドされた接着フィルム付きチップを加熱しチップ搭載用基板に固着する工程を含み、かつ接着フィルムをウエハに接着した後、チップをチップ搭載用基板に固着するまでの段階で、接着フィルムを含む積層体を、常圧に対し0.05MPa以上の静圧により加圧する工程を1回以上含む。

(もっと読む)

半導体装置実装構造体およびその製造方法ならびに半導体装置の剥離方法

【課題】耐衝撃性と量産性に優れ、かつリペア、リワークが容易で、リペア後の回路基板上に接着剤などの残渣が残らず、リペア時の応力も極力かからない半導体装置実装構造体およびその製造方法ならびに半導体装置の剥離方法を提供する。

【解決手段】一方の主面11aに電極部11bを配列した半導体装置11と、半導体装置11の電極部11bとはんだバンプ12により電気的に接続される基板電極部13aを有する回路基板13とを備え、半導体装置11の少なくとも側面11cの一部と、回路基板13とが硬化性樹脂14により接着固定され、硬化性樹脂14と回路基板13との界面領域14aの少なくとも一部に熱膨張性粒子15が混入されている。

(もっと読む)

半導体装置のアンダーフィルの充填方法

【課題】 半導体チップのファインピッチ化に対応し、アンダーフィル用樹脂内のボイドの発生を極力削減し、信頼性の高いフリップチップ実装を実現した半導体装置の製造方法を提供する。

【解決手段】 半導体チップの一面に2次元的に配列された複数の電極を、基板上の対応する導電性領域に接合するステップと、半導体チップの一面と基板との間に液状化されたアンダーフィル用樹脂を注入するステップと、一定の圧力下においてアンダーフィル用樹脂をガラス転移温度以上の温度で溶融しキュアするステップとを有する。これにより、アンダーフィル用樹脂内のボイドを消滅させる。

(もっと読む)

電子部品

【課題】素子としてのICチップが容器に強く接続され、さらに、ICチップの下部及び周辺に充填、硬化され、形成された樹脂がその後の工程にて、加熱冷却される際にICにかかる応力を低減し、動作異常並びに接続不良を削減した電子部品を提供する。

【解決手段】容器のキャビティ内に、該キャビティの底面に素子と該素子の周囲に配置される熱硬化性樹脂とを収容した電子部品であって、前記キャビティは、その開口部よりも下方位置であって且つ前記素子の下面の高さ位置よりも高い位置に前記底面と対向する対向面を有しており、前記キャビティ内の残部空間であって、前記対向面の高さ位置よりも高い位置から前記底面の間に前記熱硬化性樹脂が充填されていることを特徴とする電子部品。

(もっと読む)

シート状エポキシ樹脂組成物およびそれを用いた半導体装置

【課題】半導体素子と配線回路基板および接続用電極に生ずる応力の緩和効果に優れたシート状エポキシ樹脂組成物を提供する。

【解決手段】半導体素子3に設けられた接続用電極部2と配線回路基板1に設けられた回路電極部4とを対向させた状態で上記配線回路基板1上に半導体素子3が搭載された半導体装置における、上記配線回路基板1と半導体素子3との空隙を樹脂封止するためのシート状エポキシ樹脂組成物6であり、下記の(A)〜(C)成分を含有する。(A)エポキシ樹脂。(B)フェノール樹脂。(C)シリコーン変性ポリイミド樹脂。

(もっと読む)

電子素子の実装方法

【課題】ダイシング時およびフリップチップ実装時のアライメントマークの認識が良好な電子デバイス用接着組成物を用いた電気的接続信頼性の高い電子素子の実装方法を提供する。

【解決手段】電子素子上に形成されたバンプと実装回路基板上に形成された電極パッドとを接触接続する電子素子の実装方法であって、少なくとも(A)バンプ形成面に光線透過率70%以上100%以下の電子デバイス用接着層が形成された複数の電子素子を有する電子デバイス基板をダイシングにより個片化する工程、(B)電子デバイス用接着層が形成された電子素子を所定の温度で実装回路基板上の電極パッドに圧着し、バンプと電極パッドとの電気的接続を行う仮圧着工程および(C)電子デバイス用接着層を硬化させる本圧着工程を有する電子素子の実装方法。

(もっと読む)

281 - 300 / 545

[ Back to top ]