Fターム[5F045AB18]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 3−5族 (4,971) | 4元混晶 (505)

Fターム[5F045AB18]に分類される特許

121 - 140 / 505

低リークGANMOSFET

エンハンスメント・モードGaN MOSFET(100)が、AlGaN(又はInAlGaN)障壁層(118)上のSiO2/Si3N4ゲート絶縁層(124)を用いて形成される。SiO2/Si3N4ゲート絶縁層(124)のSi3N4部分(120)は、ゲート絶縁層(124)と障壁層(118)との間の接合での界面準位の形成を低減させ、SiO2/Si3N4ゲート絶縁層(124)のSiO2部分(122)は、漏れ電流を著しく低減させる。

(もっと読む)

(もっと読む)

導電性III族窒化物結晶の製造方法、導電性III族窒化物基板の製造方法及び導電性III族窒化物基板

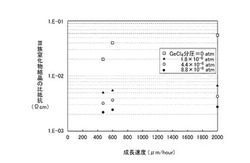

【課題】十分な導電性を付与したIII族窒化物結晶を短時間で成長可能とする。

【解決手段】III族のハロゲン化物ガスとNH3ガスを用いてIII族窒化物結晶を下地基板上に450μm/hourよりも大きく2mm/hour以下の範囲の成長速度で成長する場合において、ドーピング原料としてGeCl4を用いることによりIII族窒化物結晶

中にGeをドーピングし、III族窒化物結晶の比抵抗が1×10−3Ωcm以上1×10

−2Ωcm以下となるようにする。

(もっと読む)

窒化物半導体素子

【課題】クラックの発生を防ぎ、かつ層厚の均一性が高く、表面が平坦な窒化物半導体の多層膜を備え、高い歩留まりで電流リークのない窒化物半導体素子を提供することである。

【解決手段】窒化物半導体素子は、窒化物半導体基板の表面に形成された又は窒化物半導体基板以外の基板上に成長した窒化物半導体層の表面に形成された凹状の掘り込み領域102を含む加工基板100と、加工基板100上に最初に成膜される窒化物半導体下地層103を含む、窒化物半導体の多層膜からなる窒化物半導体多層膜101とを備え、掘り込み領域102の間隔が、0.1mm以上であり、掘り込み領域102の上端の側壁面に対する法線と、掘り込み領域102以外の表面に対する法線とのなす角が60°よりも大きく、窒化物半導体下地層103が、GaNを組成に含む化合物である構成とする。

(もっと読む)

半導体装置とその製造方法

【課題】 気相成長の際のマストランスポートを抑制する技術を提供する。

【解決手段】 表層部にトレンチ42が形成されている窒化物の半導体下地層10のトレンチ42内に、窒化物の半導体成長層を気相成長させる気相成長工程を備えている。トレンチ42に露出する半導体下地層10の表面8aの少なくとも一部が、InxAlyGa(1-x-y)N (0≦x≦1,0.00001≦y≦0.01,0<1-x-y≦1)で示されるAlドープ窒化物である。

(もっと読む)

窒化物系化合物半導体基板の製造方法及び窒化物系化合物半導体自立基板

【課題】反り返りがなく、面内のオフ角のばらつきが小さな窒化物系化合物半導体層を再現性よく成長させることができる窒化物系化合物半導体基板の製造方法、及び半導体デバイスの作製に好適な窒化物系化合物半導体自立基板を提供する。

【解決手段】成長用基板上に窒化物系化合物半導体層をエピタキシャル成長させる窒化物系化合物半導体基板の製造方法において、成長用基板として、(011)面を≒[010]方向に0〜2°(0°を除く)のオフ角で傾斜させた主面を有する希土類ペロブスカイト基板を用いる。

(もっと読む)

エピタキシャル膜および発光素子

【課題】留まりを向上するエピタキシャル膜および発光素子を提供する。

【解決手段】エピタキシャル膜30は、基板32と、基板32上に形成された第1導電型クラッド層と、第1導電型クラッド層上に形成された活性層35と、活性層35上に形成された第2導電型クラッド層とを備えている。第1および第2導電型クラッド層の少なくとも一方がInxAlyGa(1-x-y)N層(0<x<1、0<y<1、0<x+y<1)であり、厚みのばらつきが6%以内である。

(もっと読む)

半導体基板上のラージエリアガリウム窒化物又は他の窒化物ベース構造のための応力補償

基板(102)の上に、基板に対する圧縮応力を有する応力補償スタック(104)を形成すること(402)を含む方法。この方法は、基板の上に、基板に対する引っ張り応力を有する1つ又は複数のIII族窒化物アイランド(106)を形成すること(406)も含む。この方法は更に、応力補償スタックからの圧縮応力を用いて、1つ又は複数のIII族窒化物アイランドからの引っ張り応力を少なくとも部分的に相殺すること(408)を含む。応力補償スタックを形成することは、基板の上に1つ又は複数の酸化物層(202,206)と1つ又は複数の窒化物層(204)を形成することを含む。1つ又は複数の酸化物層は圧縮応力を有し得、1つ又は複数の窒化物層は引っ張り応力を有し得、酸化物層と窒化物層とが共同で圧縮応力を有し得る。酸化物層及び窒化物層の厚みは、所望の量の応力補償を提供するように選択され得る。

(もっと読む)

(もっと読む)

結晶の製造方法および発光素子の製造方法

【課題】InxAlyGa(1-x-y)N結晶(0≦x<1、0≦y<1、0<x+y≦1)の厚みを均一にし、かつ成長速度を向上する結晶の製造方法および発光素子の製造方法を提供する。

【解決手段】InAlGaN結晶を成長する工程では、基板20の主表面20aに垂直な方向において主表面に近い側に位置する第1のガス供給部11aからV族元素の原料を含む第1原料ガスG1を基板20の主表面20a上に供給するとともに、基板20の主表面20aに垂直な方向において第1のガス供給部11aより主表面20aから遠い側に位置する第2のガス供給部11bから、複数のIII族元素の原料である有機金属を含む第2原料ガスG2を基板20の主表面20a上に供給し、第1原料ガスG1の流速を第2原料ガスG2の流速の0.5以上0.8以下にし、反応容器3内の圧力を20kPa以上60kPa未満にする。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.7×10-3以下であり、主表面の面方位が、結晶基板のc軸を含む面から[0001]方向に−10°以上10°以下の傾斜角を有する。

(もっと読む)

半導体発光素子の製造方法

【課題】基板上に、面内と周縁部の膜厚の均一な塗布膜を形成することを目的とする。

【解決手段】単結晶ウエハ1と半導体層4と、その間の結晶格子の不整合を緩和するバッファ層3を備えた半導体基板の製造方法であって、前記単結晶ウエハの外周端部1aを被覆材2で被覆した後、前記バッファ層3を前記単結晶ウエハ1の一面側に形成する工程と、前記被覆材2を取り除いた後、前記半導体層4を前記バッファ層3上の一面側に形成すると共に、前記単結晶ウエハ1の外周端部1aから前記半導体層4の外周部4bにかけて前記半導体層4の構成材料からなる堆積物4aを堆積させる工程と、前記半導体層4上に塗布液をスピンコート法により塗布する工程と、を具備してなることを特徴とする半導体基板の製造方法を提供する。

(もっと読む)

気相成長方法及び気相成長装置

【課題】異なる組成の半導体層のそれぞれを、高面内均一性及び高再現性で形成できる気相成長方法及び気相成長装置を提供する。

【解決手段】反応室に接続された複数のガス供給管の前記反応室内の複数の出口からIII族原料ガスとV族原料ガスとを前記反応室内に供給して前記反応室内に配置された基板上に窒化物系半導体層を成膜する気相成長方法であって、III族原料ガスとV族原料ガスとを互いに異なる出口から基板に向けて供給して、III族中におけるAl組成比が10原子パーセント以上の窒化物系半導体を含む第1半導体層を成長させる工程と、III族原料ガスとV族原料ガスとを混合して同じ出口から基板に向けて供給して、III族中におけるAl組成比が10原子パーセント未満の窒化物系半導体を含む第2半導体層を成長させる工程と、を備えた気相成長方法を提供する。

(もっと読む)

半導体基板及び半導体発光素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性が、半導体素子の寸法相当において向上した半導体基板を提供し、更には、この半導体基板を基礎として、特性の高性能化された半導体発光素子、半導体素子を提供する。

【解決手段】基板11と、この基板11上に積層された窒化物系III−V族化合物半導体単結晶層12と、基板11と窒化物系III−V族化合物半導体単結晶層12との間に設けられた、不純物元素を5x1017cm-3以上2x1019cm-3以下含有する層10とを備える。

(もっと読む)

発光半導体素子のための成長方法

複数の前駆体及びインジウム表面賦活剤を用いて1つ以上のn型層またはp型層を多重量子井戸(MQW)サブアセンブリに重ねて形成するため、MQWサブアセンブリが低温気相成長プロセスにかけられる、光電発光半導体素子を作製する方法が提供される。前駆体及びインジウム表面賦活剤は1つ以上のキャリアガスを用いてそれぞれの流量で気相成長プロセスに導入され、キャリアガスの少なくとも1つはH2を含む。インジウム表面賦活剤は低温気相成長プロセス中に形成されるp型層の結晶品質を向上させるに十分な量のインジウムを含み、それぞれの前駆体の流量及びキャリアガスのH2含有量はn型層またはp型層内のインジウム表面賦活剤からのインジウムのモル分率をほぼ1%未満に維持するように選ばれる。別の実施形態において、低温気相成長プロセスは低温TGにおいて実行され、ここで、TG≦TB±5%であり、TBはMQW障壁層成長温度である。他の実施形態も開示され、特許請求される。  (もっと読む)

(もっと読む)

半導体発光装置および半導体発光装置の製造方法

【課題】個々の半導体発光装置を区画する素子分割溝を形成することによって表出した半導体膜の側面の所定位置で終端している保護膜を安定的に形成することにより、高い歩留りを確保する。

【解決手段】成長用基板の上に半導体膜20を形成し、半導体膜20に成長用基板に達する素子分割溝を形成し、素子分割溝を形成することによって表出した半導体膜20の側面を部分的に覆い且つ成長用基板から離間している保護膜50を形成する。素子分割溝を形成する工程は、エッチングによる表出面の半導体膜20の主面に対する傾斜角が第1の傾斜角を有するように半導体膜20をエッチングする第1エッチング工程と、第1エッチング工程の後に、エッチングによる表出面の半導体膜20に対する傾斜角が第1の傾斜角よりも大きい第2の傾斜角を有するように半導体膜20をエッチングして傾斜角が異なる表出面を形成する第2エッチング工程と、を含む。

(もっと読む)

化合物半導体基板とその製造方法

【課題】AlGaInP化合物半導体の成長温度を高くすることなく、低い酸素原子濃度を有し、表面欠陥の小突起が発生しにくいAlGaInP化合物半導体の製造方法、およびそれにより得られるAlGaInP化合物半導体基板を提供する。

【解決手段】筐体の内部に配置された反応炉の内部で化合物半導体基板を製造する方法であって、前記筐体の内部を酸素濃度が45ppm以下の雰囲気に保ったまま、ベース基板を筐体の内部であって反応炉の外部から、反応炉の内部に移動し、前記ベース基板を前記反応炉の内部に配置する段階(1)と、前記反応炉の内部に配置されたベース基板の上に化合物半導体を700℃以下でエピタキシャル成長させる段階(2)とを含む化合物半導体基板の製造方法。

(もっと読む)

窒化物半導体素子の製造方法

本発明は、窒化物半導体素子の製造方法に関する。本発明の窒化物半導体素子の製造方法は、第1支持基板上に窒化ガリウムエピ層を形成する段階と、前記窒化ガリウムエピ層上に第2支持基板を形成する段階と、前記第1支持基板を除いた残りの領域の表面にパッシベーション層を形成する段階と、前記パッシベーション層をマスクとして前記第1支持基板をエッチングする段階と、前記パッシベーション層を除去して前記第2支持基板および前記窒化ガリウムエピ層を露出させる段階とを含む。 (もっと読む)

III族窒化物半導体発光素子を作製する方法、III族窒化物半導体素子のための電極を形成する方法、及びIII族窒化物半導体素子

【課題】III族窒化物の露出エリアを絶縁膜の開口に対して良好な位置制御性で形成できる、III族窒化物半導体発光素子を作製する方法を提供する。

【解決手段】コンタクト層27及びクラッド層25を含むIII族窒化物半導体領域29をマスク35aを用いてエッチングして、III族窒化物領域33c及びエピタキシャル領域29bを形成する。次いで、マスク35a、パターン形成されたIII族窒化物リフトオフ層31a及びパターン形成されたIII族窒化物半導体領域33c上に絶縁膜39を成長する。絶縁膜39は、マスク35a上に成膜される第1の部分39aと、パターン形成されたIII族窒化物半導体領域33c上に成膜される第2の部分39bとを含む。引き続き、パターン形成されたIII族窒化物リフトオフ層31aを絶縁膜39に対してエッチャントを用いて選択的に除去して、リフトオフ法により、開口39cを有する絶縁膜39bを形成する。

(もっと読む)

エピタキシャル基板の製造方法およびエピタキシャル基板

【課題】成膜に用いる原料ガス同士の気相反応を抑制し、均一な成膜速度で均一な膜厚のエピタキシャル膜を形成するためのエピタキシャル基板の製造方法を提供する。

【解決手段】InAlGaNエピタキシャル膜を形成する工程(S20)において、基板15に近いほうから順に配置された、窒素ガスとV族元素ガスとが混合された第1の混合ガスを流す第1ガスライン10と、窒素ガスとIII族元素ガスとが混合された第2の混合ガスを流す第2ガスライン20と、サブフロー窒素ガスを流す第3ガスライン30から、基板の主表面に対向する領域へガスを流す。InAlGaNエピタキシャル膜を形成する工程(S20)における、基板15が配置される反応室内50の圧力は15kPa以上25kPa以下であり、第2の混合ガス中に含まれる窒素ガスの流速が3.25m/s以上3.35m/s以下である。

(もっと読む)

気相成長装置

【課題】デポ膜の剥がれを防止し、生産性向上させることができるMOCVD装置を提供する。

【解決手段】基反応炉10内に基板12を保持するサセプタ14が設けられ、導入部18から、原料ガスを反応炉10内に導入することにより基板12上にAlxGayInzN(ただしx+y+z=1)膜をMOCVD法によってエピタキシャル成長させる気相成長装置において、基板12と対向するように反応炉10の内壁に取り付けられている天板30(防着板)の基板12側の表面に、GaN膜とAlN膜が交互に積層された多層膜32を形成する。

(もっと読む)

窒化物半導体デバイス

【課題】 ウエハ−プロセスで基板の上に製造された素子単位をチップ分離する際に研磨、切断などの工程を減らすことができ、基板を繰り返し使用できる窒化物半導体デバイス作製方法によって作製したデバイスを提供する。

【解決手段】 閉曲線をなす結晶成長速度の遅い欠陥の集合した欠陥集合領域Hと結晶成長速度の速い低欠陥の領域ZYの位置が予め決まっている窒化物半導体欠陥位置制御基板Sを用い、低欠陥領域ZYにデバイスの内部が、欠陥集合領域Hに境界線が来るように窒化ガリウム基板の上に窒化物半導体層(上層部B)をエピタキシャル成長させ、レーザ照射或いは機械的手段で欠陥位置制御基板Sと成長層(上層部B)を上下方向横方向に同時分離し、基板は繰り返し使用する。作製されたデバイスは端面が成長によるファセットで形成されている。

(もっと読む)

121 - 140 / 505

[ Back to top ]