Fターム[5F045AD10]の内容

気相成長(金属層を除く) (114,827) | 成膜条件−成膜温度 (8,040) | 600≦T<700℃ (701)

Fターム[5F045AD10]に分類される特許

121 - 140 / 701

化合物半導体基板の製造方法及び化合物半導体基板

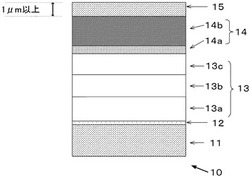

【課題】従来の化合物半導体基板に比べて反りが小さく、これによって割れにくく、またハンドリングが容易であるという化合物半導体基板の製造方法を提供する。

【解決手段】少なくとも、GaAs基板11上に発光層13をエピタキシャル成長させる工程と、該発光層の前記GaAs基板と反対側となる片方の主表面(第一主面)にp型GaP窓層14を気相成長させる工程とを有する化合物半導体基板の製造方法において、前記p型GaP窓層を気相成長させた後に、該p型GaP窓層の表面上に厚さ1μm以上のGaAs層15を気相成長させることを特徴とする化合物半導体基板の製造方法。

(もっと読む)

エピタキシャルウエーハの製造方法

【課題】p型層を形成する際に混入するSiによって発生する順方向電圧(Vf)の不良を従来より低減させ、順方向電圧が良好なエピタキシャルウエーハの製造方法を提供する。

【解決手段】少なくとも、化合物半導体からなる基板上に、ハイドライド気相成長法によってp型層をエピタキシャル成長させる工程を有するエピタキシャルウエーハの製造方法であって、前記p型層をエピタキシャル成長を開始する前の前記基板の昇温時に、p型ドーパントガスを前記p型層のエピタキシャル成長時より多く流すことを特徴とするエピタキシャルウエーハの製造方法。

(もっと読む)

半導体発光素子と、その製造方法およびランプ、電子機器、機械装置

【課題】発光層の結晶性に起因する不良が生じにくく、かつ、高い出力の得られる半導体発光素子および半導体発光素子の製造方法を提供する。

【解決手段】第一有機金属化学気相成長装置において、基板上に第一n型半導体層を積層する第一工程と、第二有機金属化学気相成長装置において前記第一n型半導体層上に、第二n型半導体層と、障壁層およびGa1−yInyN(0.07<y<0.30)なる組成の井戸層からなる発光層と、p型半導体層と、を順次積層する第二工程とを具備し、前記第二工程において、前記障壁層を第一の成長温度T1で成長させた後に、前記第一の成長温度T1よりも高温の第二の成長温度T2に昇温して前記障壁層を成長させ、さらに、前記第二の成長温度T2よりも低温の前記第三の成長温度T3に降温して前記障壁層の成長を続けることを特徴とする半導体発光素子の製造方法を採用する。

(もっと読む)

化合物半導体膜気相成長用サセプタおよび化合物半導体膜の形成方法

【課題】基板の端部近傍から作製する素子、例えば発光素子の発光波長が長波長にならず、基板中心部から作製する発光素子との違いを小さくすることができる、基板中心部と基板周辺部から作製する素子の特性差を小さくすることができる化合物半導体膜の気相成長に好適な化合物半導体膜気相成長用サセプタを提供する。

【解決手段】化合物半導体膜の気相成長の際に基板を支持するサセプタであって、該サセプタは、前記基板が配置されるザグリ部を少なくとも1つ以上備え、該ザグリ部は、底部底面がすり鉢状に湾曲しており、該湾曲部の凹部の最大深さが250〜500μmとなっているものであることを特徴とする化合物半導体膜気相成長用サセプタ。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】従来のCVD法の欠点とALD法の欠点を改善し、薄膜化の要求に応えるとともに、高い成膜速度を実現する。

【解決手段】CVD反応が生じる条件下でそれ単独で固体となる第1元素を含むガスを供給して基板上に第1元素を含む第1の層を形成する工程と、それ単独では固体とならない第2元素を含むガスを供給して第1の層を改質して第1元素および第2元素を含む第2の層を形成する工程と、を1サイクルとしてこのサイクルを1回以上行い、所定膜厚の第1元素および第2元素を含む薄膜を形成する。

(もっと読む)

半導体装置の製造方法、基板処理方法及び基板処理装置

【課題】低誘電率、低エッチングレート、高絶縁性の特性を備える絶縁膜を形成する。

【解決手段】基板を収容した処理容器内にCVD反応が生じる条件下で所定元素含有ガスを供給することで、基板上に所定元素含有層を形成する工程と、処理容器内に炭素含有ガスを供給することで、所定元素含有層の上に炭素含有層を形成して所定元素および炭素を含む層を形成する工程と、処理容器内に窒素含有ガスを供給することで、所定元素および炭素を含む層を窒化して炭窒化層を形成する工程と、を1セットとしてこのセットを所定回数行うことで所定厚さの炭窒化層を形成する工程と、処理容器内に酸素含有ガスを供給することで、所定厚さの炭窒化層を酸化して酸炭窒化層を形成する工程と、を1サイクルとして、このサイクルを所定回数行うことで、基板上に所定膜厚の酸炭窒化膜を形成する工程を有する。

(もっと読む)

AlGaInP系半導体発光素子用エピタキシャルウェハ及びその製造方法

【課題】AlGaInP系半導体発光素子用エピタキシャルウェハ表面平坦度およびダイオードチップを製造する際の発光強度の歩留まりを向上できるAlGaInP系半導体発光素子用エピタキシャルウェハを提供する。

【解決手段】N型GaAs基板2上に、N型AlGaInP系クラッド層4、AlGaInP系活性層5、P型AlGaInP系クラッド層6、及びGaPからなる電流拡散層7を有するAlGaInP系半導体発光素子用エピタキシャルウェハ1において、電流拡散層7が、P型AlGaInP系クラッド層6上に形成されたV/III比が1以上100以下の低V/III比部分8と、低V/III比部分上に形成されたV/III比が100以上500以下の高V/III比部分9とからなるものである。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】クリーニングガスに一酸化窒素ガスを添加して処理室内のドライクリーニングを行う際、その取り扱いを容易にし、制御性よくクリーニングの性能を向上させる。

【解決手段】基板を処理する処理容器201と、該処理容器内にフッ素原子を含むガスと一酸化窒素ガスとを事前に混合させて供給する第1のクリーニングガス供給系232hと、第1のクリーニングガス供給系とは別に設けられ、処理容器内にフッ素原子を含むガスを供給する第2のクリーニングガス供給系232eと、を有する基板処理装置として、前記第1のクリーニングガスと、前記第2のクリーニングガスと、を処理容器201内で混合してドライクリーニングを行う。

(もっと読む)

光電変換素子及びその製造方法

【課題】光電変換効率を向上させることが可能な光電変換素子及びその製造方法を提供する。

【解決手段】低温で成長させることにより作製した第1窒化ガリウム層と、該第1窒化ガリウム層の表面に形成された窒化インジウム量子ドットと、を有する光電変換素子、及び、低温で成長させることにより窒化ガリウム層を形成する第1工程と、該第1工程によって形成された窒化ガリウム層の表面に窒化インジウム量子ドットを形成する第2工程と、を有する、光電変換素子の製造方法とする。

(もっと読む)

半導体膜の改良された堆積方法

【課題】均一性の高いSi又はSiGeを基板表面上に堆積する方法を提供する。

【解決手段】化学気相成長プロセスにおいて、輸送量制限領域又はその近傍で、薄膜の堆積を行うことを可能にする化学前駆体を利用する。このプロセスによれば、堆積速度が大きく、さらに組成的にも厚み的にも、通常の化学前駆体を用いて調整した膜より均一な膜を生成することができる。好ましい実施の形態では、トリシランを使用して、トランジスタゲート電極などの様々な用途で半導体産業において有用なSi含有薄膜を堆積する。

(もっと読む)

高品質の緩和シリコンゲルマニウム層の製造方法

【課題】半導体材料上のSi1−xGex層の堆積中、パーティクル生成を最小限化する方法を提供する。

【解決手段】Si前駆体と、分解温度がゲルマンより高いGe前駆体とを含む雰囲気中に基板を設けるステップ、および最終Ge含有量が約0.15より大きくかつパーティクル密度が約0.3パーティクル/cm2より小さいSi1−xGex層を前記基板上に堆積するステップを含む。

(もっと読む)

気相成長装置

【課題】基板上に成長結晶層の膜厚均一性を向上させることができ、歩留まりが高い気相成長装置を提供する。

【解決手段】基板15を支持する底面サセプタ部14aと、サセプタ14a,bの上面に沿って流れる材料ガス流を供給するノズル11と、を含む。サセプタ14a,bは、それぞれが基板と同一材料からなる、底面サセプタ部14aの上面に基板に嵌合する凹状の基板保持部を画定する外周サセプタ部14bとサセプタ14a,bの裏面を画定する底面サセプタ部14aとから構成されていること、外周サセプタ部14bは、基板15の上面と同一平面となる基板保持部を囲む上面を有しかつ、基板保持部を囲む上面が基板の上面の結晶面方位と同一の結晶面方位を有する。

(もっと読む)

半導体素子用エピタキシャル基板および半導体素子

【課題】InAlN/GaNヘテロ構造を有し、かつオーミックコンタクト特性の優れた半導体素子用のエピタキシャル基板を提供する。

【解決手段】半導体素子用エピタキシャル基板10Aが、下地基板1と、GaNからなるチャネル層3と、AlNからなるスペーサ層4と、III族元素としてInとAlとGaとを含む障壁層5と、を備え、障壁層が、InxAl1-xN(0<x<1)からなるマトリックス層にGa原子がドープされ、障壁層のGa原子の濃度が1.2×1020cm-3以下であるようにする。

(もっと読む)

基板保持具、縦型熱処理装置および熱処理方法

【課題】被処理基板が反っていても水平に保持することができ、被処理基板の位置ずれや反り量のばらつきを吸収することができるようにすることである。

【解決手段】左右一対の前側支柱26と、左右一対の後側支柱27とを有し、これら前側支柱26および後側支柱27に被処理基板wを前方から挿入可能で且つ上下方向に所定の間隔で保持可能な複数の溝28,29を形成してなる基板保持具9において、前側支柱26の前記溝28上の支持面28aを前後方向の中心線c1に対して接近すべく斜め前方に延長させ、互いに接近した前側支柱26の支持面28aの先端における被処理基板wの支持点30,30間の寸法X2を、前記後側支柱27の支持面29aの先端における被処理基板wの支持点31,31間の寸法Y2と同じにした。

(もっと読む)

導電性III族窒化物単結晶基板の製造方法

【課題】所望の比抵抗を有する導電性III族窒化物単結晶基板を低コストで製造することができる導電性III族窒化物単結晶基板の製造方法を提供する。

【解決手段】導電性III族窒化物単結晶基板の製造方法は、GaClガス、NH3ガス、及びN2又はArにより所定の濃度に希釈されたSiH2Cl2ガスをGaN単結晶基板に供給し、450μm/hourより大きく2mm/hour以下の範囲の成長速度でGaN単結晶基板上にGaN単結晶を成長させると共に、SiH2Cl2ガスが所定の濃度に希釈されたことによるNH3ガスとの反応の抑制により、GaN単結晶の比抵抗が1×10−3Ωcm以上1×10−2Ωcm以下となるようにSiH2Cl2ガスに含まれるSiがGaN単結晶にドーピングされることを含む。

(もっと読む)

基板処埋装置及び半導体装置の製造方法

【課題】薄膜を成膜するときの膜厚の均一性を良好にする。

【解決手段】基板処理装置は、反応管6と、反応管6内で基板を回転させる回転機構20と、処理ガスを反応管6に供給するガス供給系と、反応管6内の雰囲気を排気する排気系と、制御部60と、を備える。ガス供給系は、ガス供給配管51と、ガス供給配管51を開閉するバルブ2と、を有し、排気系は、排気管40と、排気管40を開閉する排気バルブと、を有する。制御部60が排気バルブを閉じるとともにバルブ2を開くことで、反応管6内の排気を止めた状態でガス供給配管51から処理ガスを反応管6に供給する。処理ガスを周期的に反応管6に供給する際、制御部60がガス供給系の供給周期及び回転機構20の回転周期を制御し、処理ガスが基板に対して先に供給される時の基板の周縁箇所と、その次に供給される時の基板の周縁箇所とが異なる。

(もっと読む)

GaN系半導体エピタキシャル基板の製造方法

【課題】反りのない優れた結晶性を有するGaN系半導体をエピタキシャル成長させることができるGaN系半導体エピタキシャル基板の製造方法を提供する。

【解決手段】希土類ペロブスカイト基板上11に、AlNからなる低温保護層12を成長させ、この低温保護層12上に、Alの組成x1が0.40≦x1≦0.45のAlx1Ga1−x1Nからなる第1AlGaN系半導体層を成長させる。そして、前記第1AlGaN系半導体層上に、Alの組成x2が0≦x2≦0.45のAlx2Ga1−x2Nからなる第2AlGaN系半導体層以降の成長層を積層させて、組成勾配層13,14とする。

(もっと読む)

GaN系半導体エピタキシャル基板の製造方法

【課題】異種基板上にGaN系半導体を成長させることにより発生する貫通転位を低減し、低転位密度(例えば、105/cm2以下)のGaN系半導体をエピタキシャル成長させることができるGaN系半導体エピタキシャル基板の製造方法を提供する。

【解決手段】異種材料からなる成長用基板(例えばNGO基板)上にGaN系半導体をエピタキシャル成長させる際に、成長用基板上に、第1GaN系半導体層をエピタキシャル成長させ(第1工程)、第1GaN系半導体層における転位発生部分にエッチピットを形成し(第2工程)、エッチピットにSi3N4膜を選択的に形成し(第3工程)、Si3N4膜上に第2GaN系半導体層をエピタキシャル成長させる(第4工程)。

(もっと読む)

III−V族化合物半導体の気相成長方法

【課題】ウェーハ面内全域にて凹凸加工された構造を埋め込み成長可能であり、かつ、凹凸形状によらない安定した埋め込み平坦化が可能なIII−V族化合物半導体の気相成長方法を提供する。

【解決手段】III−V族化合物半導体基板の表面に形成された規則的な凹凸を有する四元系III−V族化合物半導体層の上に、有機金属気相成長法を用いて、上記凹凸の熱変形を抑制する保護膜となるIII−V族化合物半導体層を、第一の成長温度で所定の膜厚となるまでエピタキシャル成長させた後、上記第一の成長温度よりも高い第二の成長温度で連続して同一組成の半導体層を、トータルの厚さが上記凹凸の高さよりも大きくなるまで成長させるようにした。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】中間層としてGe結晶を用いる場合の化合物半導体へのGe原子の混入を抑制する。

【解決手段】ベース基板と、ベース基板上に形成された第1結晶層と、第1結晶層を被覆する第2結晶層と、第2結晶層に接して形成された第3結晶層とを備え、第1結晶層が、ベース基板における第1結晶層と接する面と面方位が等しい第1結晶面、及び、第1結晶面と異なる面方位を有する第2結晶面を有し、第2結晶層が、第1結晶面と面方位が等しい第3結晶面、及び、第2結晶面と面方位が等しい第4結晶面を有し、第3結晶層が、第3結晶面及び第4結晶面のそれぞれの少なくとも一部に接しており、第1結晶面に接する領域における第2結晶層の厚みに対する第2結晶面に接する領域における第2結晶層の厚みの比が、第3結晶面に接する領域における第3結晶層の厚みに対する第4結晶面に接する領域における第3結晶層の厚みの比よりも大きい半導体基板を提供する。

(もっと読む)

121 - 140 / 701

[ Back to top ]