Fターム[5F045AF12]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 基板の形状、構造、大きさ、厚み等 (845) | 基板表面の状態(面粗さ、ステップ等) (699)

Fターム[5F045AF12]の下位に属するFターム

結晶方位(面方位)オリフラ、ノッチ (341)

膜形成の核を被成膜面上に有するもの (67)

Fターム[5F045AF12]に分類される特許

101 - 120 / 291

CdTe系半導体基板の製造方法及びCdTe系半導体基板

【課題】良質なエピタキシャル結晶を成長可能なエピタキシャル成長用のCdTe系半導体基板の製造方法及びCdTe系半導体基板を提供する。

【解決手段】所定の半導体をエピタキシャル成長させるためのCdTe系半導体基板の製造方法において、基板表面を鏡面研磨した後又はエッチングした後、24時間以内に非酸化性ガス雰囲気中で保管する。これにより、原子間力顕微鏡で基板表面を観察したときに10μm×10μmの視野範囲内に高さ5nm以上の突起が観察されないCdTe系半導体基板が実現される。

(もっと読む)

III族窒化物半導体積層構造体

【課題】高度の結晶性を有し、特に直径100mm以上の大型基板を用いる場合でも全面均一に平坦なAlN結晶膜シード層を用いることにより、結晶性の良いGaN系薄膜を得、信頼性の高い高輝度のLED素子等を得る。

【解決手段】サファイア基板上にシード層としてスパッター法で堆積されたAlN結晶膜を有し、該シード層上にIII族窒化物半導体からなる、n型半導体層、発光層およびp型半導体層を積層してなるIII族窒化物半導体積層構造体において、該シード層のAlN結晶膜中の酸素含有量が0.1原子%以上5原子%以下であり、AlN結晶膜は結晶粒界の間隔が200nm以上であり、かつ最終p型半導体層であるp−コンタクト層のロッキングカーブ半値幅が(0002)面と(10−10)面でそれぞれ60arcsec以下および250arcsec以下であることを特徴とするIII族窒化物半導体積層構造体。

(もっと読む)

引張膜のための応力管理

クラッキングする傾向を減少させた、間隙充填酸化ケイ素層の形成が記載される。堆積は、トレンチの充填を容易にする、流動可能なシリコン含有層の形成を含む。高い基板温度における後続の処理が、従来技術の方法に従って形成された流動可能な膜よりも、誘電体膜中のクラッキングを少なくする。間隙充填酸化ケイ素層の形成に先立って堆積された圧縮性ライナ層が記載され、後続して堆積される膜がクラックする傾向を減少する。流動可能なシリコン含有層の後に堆積される圧縮性キャッピング層も、クラッキングを減少させるように決定された。圧縮性ライナ層および圧縮性キャッピング層は、単独でまたは組み合わせて使用され、クラッキングを減少させ、多くの場合クラッキングをなくすことができる。開示した実施形態の圧縮性キャッピング層は、下にある窒化ケイ素の層を酸化ケイ素層に変換できることが、さらに確定されている。 (もっと読む)

化合物単結晶およびその製造方法

【課題】半導体素子への適用が可能な低欠陥密度の化合物半導体結晶基板、およびその製造方法を提供する。

【解決手段】立方晶{001}面を表面とする単結晶基板上に、エピタキシャル成長により2種類の元素A、Bからなる化合物単結晶を成長させる化合物単結晶の製造方法において、反位相領域境界面ならびに元素AおよびBに起因する積層欠陥を、表面に平行な<110>方向にそれぞれ等価に生じさせながら化合物単結晶を成長させる工程(I)と、工程(I)において生じた元素Aに起因する積層欠陥を、反位相領域境界面と会合消滅させる工程(II)と、工程(I)において生じた元素Bに起因する積層欠陥を、自己消滅させる工程(III)と、反位相領域境界を完全に会合消滅させる工程(IV)と、を有し、工程(IV)は、工程(II)および(III)と並行して、又は、工程(II)および(III)の後に行う。

(もっと読む)

III族窒化物半導体の製造方法

【課題】a面またはc面サファイア基板上に、平坦性、結晶性に優れたc面GaNを成長させること。

【解決手段】c面を主面とするサファイア基板の表面に、複数の正六角柱の凸部1をハニカム状に配列したパターンの凹凸形状をドライエッチングにより形成した。凸部1は、側面がm面である正六角柱状の凸部を、その正六角柱の中心軸1bの回りに反時計回りに15°回転させたものである。したがって、凸部1の側面1aは、低指数面であるa面やm面ではない高指数面である。次に、凹凸形状を施した側のサファイア基板上にスパッタ法によってAlNからなるバッファ層を形成し、バッファ層を介してMOCVD法によってc面を主面とするGaN層を形成した。これにより、結晶性、平坦性に優れたGaN層が得られる。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法およびシリコンエピタキシャルウェーハ

【課題】用いるシリコン単結晶基板の導電型や添加元素に関わらず、ミスフィット転位の発生を抑制したシリコンエピタキシャルウェーハおよびその製造方法を提供する。

【解決手段】少なくとも、シリコン単結晶基板2と、該シリコン単結晶基板2の主表面上に気相成長によって形成されたシリコン単結晶薄膜3とからなるシリコンエピタキシャルウェーハ1であって、前記シリコン単結晶基板2の格子歪み量εを((X線回析法で測定した前記シリコン単結晶基板2の格子定数―真性シリコンの格子定数)/真性シリコンの格子定数の絶対値)とし、前記シリコン単結晶薄膜3の厚さをtμmとした時、t<(5.0×10−4)×ε―1.1を満たすものであることを特徴とするシリコンエピタキシャルウェーハ。

(もっと読む)

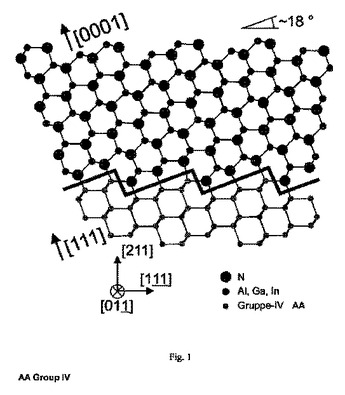

半極性ウルツ鉱型III族窒化物をベースとする半導体層、及び当該窒化物をベースとする半導体部材

III族窒化物層は、電子工学及び電子光学の分野で適用範囲が広い。このような層の成長は通常、サファイア、SiC、近年ではSi(111)のような基板上で行われる。この際に得られる層は通常、成長方向において極性、及び/又はC軸配向性である。電子光学における多くの適用にとって、またSAWにおける音響的な適用でも、非極性、又は半極性III族窒化物層の成長は、関心の対象であり、また必要とされている。本方法により、極性が低減されたIII族窒化物層の容易かつ安価な成長が、事前に基板を三次元構造化することなく、可能になる。  (もっと読む)

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、クラックの発生を防止し、表面平坦性が良好な窒化物半導体成長層を形成し、電流リークパスやダメージの無い半導体素子及びその製造方法を提案することを目的とする。

【解決手段】本発明は、凹部からなる掘り込み領域を備えた加工基板において、丘の両端部双方にSiO2壁を形成し、丘表面の上面成長部からマイグレーションにより窒化物半導体薄膜の原料となる原子・分子が掘り込み領域内に移動して窒化物半導体薄膜を形成することを抑制することで、表面平坦性が良好な窒化物半導体成長層が形成でき、歩留まり良く半導体素子を製造できる。

(もっと読む)

III族窒化物半導体結晶の製造方法、およびIII族窒化物半導体基板

【課題】テラスエッジ部上の結晶欠陥を低減し、かつ表面平坦性に優れたm面GaN結晶を製造すること。

【解決手段】a面サファイア基板10表面には、長手方向をm軸方向とする帯状の凹部11が、ストライプ状に配置されて複数形成されている。凹部11は、サファイア基板10の主面に平行な底面11aと、向かい合う2つの側面11bで構成されている。側面11bは平面状である。テラス10aの幅xは20μm以下、凹部11の底面11aの幅yは15μm以下、凹部11の深さzは50nm以上、サファイア基板10の主面に対して凹部11の側面11bのなす角度θは50〜90°、である。このサファイア基板10上に結晶成長させたm面GaNは、結晶欠陥が少なく結晶性に優れ、かつ表面平坦性に優れている。

(もっと読む)

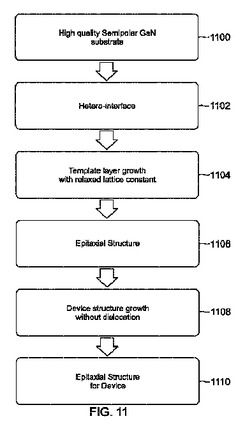

ヘテロ界面にミスフィット転位を有する部分的または完全に緩和された合金上の半極性窒化物ベースの素子

ヘテロ界面周辺のミスフィット転位を空間的に制限することによって、緩和された格子定数を有する、転位のない高品質テンプレート。これは、高In組成の素子のためのテンプレート層として使用することができる。具体的には、本発明は、高品質InGaNテンプレート(In組成は、約5〜10%である)を調製し、別様に可能であるよりも非常に高いIn組成のInGaN量子井戸(QW)(または多重量子井戸(MQW))を、これらのテンプレート上に成長させることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体素子構造を構成する半導体層の成長用基板として、該半導体層と同種の半導体材料を用いる場合に、半導体層を成長した後の露光時に認識可能なアライメントマークを形成できるようにする。

【解決手段】アライメントマーク検出用光源に対して透明な材料からなる基板101の上に、該基板101と異なる屈折率を有する材料からなる第2のアライメントマーク120を形成する。続いて、基板101の上に、活性層105を含むGaN系エピタキシャル層を第2のアライメントマーク120を埋め込むように成長する。続いて、第2のアライメントマーク120を参照しながら、GaN系エピタキシャル層に対する露光の位置合わせを行う。

(もっと読む)

窒化物半導体素子の製造方法

【課題】クラックの発生が防止されるとともに、表面平坦性が良好な窒化物半導体成長層が形成される窒化物半導体素子の製造方法を提供する。

【解決手段】窒化物半導体素子の製造方法は、凹部からなる掘り込み領域を備えた加工基板に窒化物半導体薄膜を積層し、凹部の断面積に対して、凹部に埋め込まれた窒化物半導体薄膜の占める断面積の割合を0.8以下とする。このことにより、クラックを防止し、表面平坦性が良好な窒化物半導体成長層が形成できる。

(もっと読む)

半導体ウェハの製造方法

【課題】半導体ウェハの裏面の定義されたかつ有利な特性を有する半導体ウェハを提供すること

【解決手段】a) シリコン棒をウェハに切断することにより半導体ウェハを準備する工程、b) 前記半導体ウェハのエッジを丸めることで、前記半導体ウェハは前面及び裏面が平坦な面とエッジ領域で丸められかつ傾斜する面とを有する工程、c) 前記半導体ウェハの前面及び裏面を研磨し、前記前面の研磨は、研磨パッド中に固定された砥粒を有していない研磨パッドを使用する化学機械的研磨を有し、前記半導体ウェハの裏面の研磨は、それぞれ研磨パッド中に結合された研磨材料を有する研磨パッドを使用してかつ前記半導体ウェハの裏面に研磨圧力を加える3つの工程で行い、第1の工程では、固体を有していない研磨剤を前記研磨パッドと前記半導体ウェハの裏面との間に導入し、第2及び第3の工程では研磨材料を有する研磨剤を導入し、第1の及び第2の工程の8〜15psiの研磨圧力を、第3の工程では0.5〜5psiに低下させる工程を有する半導体ウェハの製造方法

(もっと読む)

半導体ウエハの製造方法及び半導体ウエハ

【課題】格子不整合系基板を使用しながら、高品質な単結晶窒化物半導体の結晶成長を実現する半導体ウエハの製造方法を提供する。

【解決手段】半導体基板101の表面にグラフェン層110を設ける工程と、グラフェン層110の炭素原子の配列を示すハニカム構造の中心に、単結晶半導体層の結晶を構成する一の元素を吸着させる工程と、この一の元素に前記結晶を構成する当該元素とは異なる他の元素を結合させ、前記結晶の第1層114を形成する工程と、前記第1層の表面にさらに所定の層数の前記結晶半導体層を結晶成長する工程を備える。

(もっと読む)

窒化物半導体ウェハ、窒化物半導体発光素子および窒化物半導体発光素子の製造方法

【課題】素子特性および歩留まりを向上させることが可能な窒化物半導体発光素子を提供する。

【解決手段】この窒化物半導体レーザ素子150(窒化物半導体発光素子)は、結晶成長面1aを有し、結晶成長面1aから厚み方向に掘り込まれた掘り込み領域3と、掘り込まれていない領域である非掘り込み領域4とを含むn型GaN基板1と、掘り込み領域3に形成され、窒化物半導体の結晶成長を抑制する成長抑制膜5と、n型GaN基板1の結晶成長面1a上に形成されたn型クラッド層11を含む半導体素子層10とを備えている。上記掘り込み領域3は、凹部2を含んでおり、上記成長抑制膜5は、凹部2内における結晶成長面1aより低い位置に形成されている。

(もっと読む)

高品質ホモエピタキシ用微傾斜窒化ガリウム基板

【課題】III−V族窒化物系超小型電子および光電子デバイスの作製におけるホモエピタキシャル蒸着に有用に用いられる微傾斜窒化ガリウム基板を提供する。

【解決手段】<0001>方向から、

方向または

方向に主に向かって約0.2〜約10度の範囲のオフカット角度でオフカットされた(0001)表面を含むGaN基板。表面が50×50μm2AFM走査により測定された1nm未満のRMS粗さと、3E6cm−2未満の転位密度とを有する。この基板はオフカットスライスおよびラッピングまたは微傾斜へテロエピタキシャル基板上の成長により形成する。

(もっと読む)

窒化ガリウム半導体構造体の製造方法、半導体構造体の製造方法および半導体構造体

【課題】層をマスクする必要がない、および/または、窒化ガリウムの成長プロセスを中断する必要がない窒化ガリウム半導体構造体の製造方法を提供する。

【解決手段】非窒化ガリウム柱100aを含み、それらの間に溝100bを規定する基板100であって、その非窒化ガリウム柱100aは非窒化ガリウム側壁100cおよび非窒化ガリウム頂部100dを含み、溝100bは非窒化ガリウム底100eを含むものを用いる。この基板100上に第1の温度で窒化ガリウムを成長させる。次に、第1の温度より高い第2の温度で基板100上に窒化ガリウムの成長を続ける。

(もっと読む)

立方晶型窒化物半導体ウェハ及びその製造方法、並びに立方晶型窒化物半導体自立基板の製造方法

【課題】実用的な発光効率を有する緑色発光デバイスを実現可能な立方晶型窒化物半導体ウェハ及びその製造方法、並びに立方晶型窒化物半導体自立基板の製造方法を提供する。

【解決手段】立方晶の種結晶基板1の表面に、窒化物半導体2が成長しにくい材料で覆い且つ周期的に又はランダムに種結晶基板1の表面が露出した開口部4を有するマスク3を形成し、マスク3の開口部4から窒化物半導体2を成長し、種結晶基板1と局所的に接触した連続膜とした窒化物半導体2を形成する。

(もっと読む)

窒化物半導体ウェハ、窒化物半導体素子および窒化物半導体素子の製造方法

【課題】EL発光パターンを改善することにより、発光効率を向上させることが可能な窒化物半導体素子を提供する。

【解決手段】この窒化物半導体レーザ素子100(窒化物半導体素子)は、m面に対してa軸方向にオフ角度を有する面を成長主面10aとするn型GaN基板10と、n型GaN基板10の成長主面10a上に形成された窒化物半導体層20とを備えている。上記n型GaN基板10は、成長主面10aから厚み方向に掘り込まれた凹部2(掘り込み領域3)と、掘り込まれていない領域である非掘り込み領域4とを含んでいる。また、n型GaN基板10上に形成された窒化物半導体層20は、凹部2(掘り込み領域3)に近づくにしたがって層厚が傾斜的に減少する層厚傾斜領域5と、層厚変動の非常に小さい発光部形成領域6とを有している。そして、上記発光部形成領域6にリッジ部28が形成されている。

(もっと読む)

おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法

【課題】おもて面と裏面とを有するシリコン単結晶基板及び前記おもて面上に堆積されたSiGeの層を含んでなるウェーハを製造する方法。

【解決手段】本方法は、次の順序で工程:前記シリコン単結晶基板のおもて面及び裏面を同時に研磨する工程;応力補償層を前記シリコン単結晶基板の裏面上に堆積させる工程;前記シリコン単結晶基板のおもて面を研磨する工程;前記裏面上に堆積された応力補償層を有する前記シリコン単結晶基板を洗浄する工程;及びSiGeの完全に又は部分的に緩和された層を前記シリコン単結晶基板の前記おもて面上に堆積させる工程を含んでなる。

(もっと読む)

101 - 120 / 291

[ Back to top ]