Fターム[5F045AF12]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 基板の形状、構造、大きさ、厚み等 (845) | 基板表面の状態(面粗さ、ステップ等) (699)

Fターム[5F045AF12]の下位に属するFターム

結晶方位(面方位)オリフラ、ノッチ (341)

膜形成の核を被成膜面上に有するもの (67)

Fターム[5F045AF12]に分類される特許

21 - 40 / 291

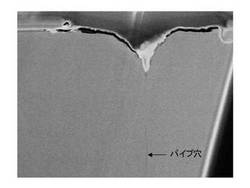

窒化物半導体発光素子およびその製造方法

【課題】静電耐圧が高い窒化物半導体発光素子を歩留まりが高く製造する窒化物半導体発光素子の製造方法を提供する。

【解決手段】本発明の窒化物半導体発光素子は、成長用基板と、該成長用基板上に形成されたn型窒化物半導体層と、該n型窒化物半導体層上に形成された発光層と、該発光層上に形成されたp型窒化物半導体層とを有し、n型窒化物半導体層の発光層と接する側の表面から基板に向けて略垂直に延び、直径が2nm〜200nmであるパイプ穴を5000個/cm2以下有することを特徴とする。

(もっと読む)

半導体発光素子、窒化物半導体層成長用基板及び窒化物半導体ウェーハ

【課題】高効率の半導体発光素子、窒化物半導体層成長用基板及び窒化物半導体ウェーハを提供する。

【解決手段】実施形態によれば、第1導電形の層を含む第1半導体層と、第2導電形の層を含む第2半導体層と、第1半導体層と第2半導体層との間に設けられた発光層と、を備えた半導体発光素子が提供される。第1半導体層は、発光層とは反対の側の第1主面に設けられた複数の構造体を有する。複数の構造体のそれぞれは凹部、または、凸部である。複数の構造体のうちのいずれかである第1の構造体の形状の重心と、複数の構造体のうちで第1の構造体に最も近い第2の構造体の形状の重心と、は、第2軸上に並ぶ。凹部の深さをhbとし、凹部の底部の第2軸に沿った幅をrbとし、凸部の第2軸に沿った幅をRbとしたとき、rb/(2・hb)≦0.7、及び、rb/Rb<1を満たす。

(もっと読む)

半導体発光素子、窒化物半導体層、及び、窒化物半導体層の形成方法

【課題】低転位密度と良好な表面平坦性とを両立した、高効率な半導体発光素子、窒化物半導体層、及び、窒化物半導体層の形成方法を提供する。

【解決手段】実施形態によれば、下地層と、第1半導体層と、発光層と、第2半導体層と、を備えた半導体発光素子が提供される。発光層は下地層と第1半導体層との間に設けられる。第2半導体層は下地層と発光層との間に設けられる。下地層は、第2半導体層の側の第1主面と、第1主面とは反対側の第2主面と、を有する。下地層は、第2主面に設けられ、凹部と側部と凸部とを有する凹凸を有する。凸部に繋がる転位の少なくともいずれかは、側部に繋がる。凸部に繋がる転位のうちで第1主面に到達する転位の割合は、凹部に繋がる転位のうちで第1主面に到達する転位の割合よりも低い。第1主面のうちで凹部と重なる領域に繋がる転位は、凹部に繋がる転位よりも少ない。

(もっと読む)

発光ダイオード用基板及び発光ダイオード

【課題】高い光取出し効率を実現でき、かつ、製造が容易で低コストな発光ダイオード用基板及び発光ダイオードを提供する。

【解決手段】表面sに発光層7を含む半導体層3が形成される発光ダイオード用基板であって、サファイア基板からなり、表面sには、発光層7が発光する光を乱反射するランダムに配置された凹凸が形成され、かつ、凹凸は結晶方位を反映して形成されており、凹凸の高さが1μm以上5μm以下であり、表面のX線回折ロッキングカーブ半値幅が60秒以下である。

(もっと読む)

半導体発光素子用基板の製造方法及びそれを用いた半導体発光素子

【課題】基板に凹凸を形成した発光素子、その基板において、好適な特性を有するものを提供する。

【解決手段】基板10の第1主面上に、半導体20の発光構造を有する半導体発光素子100において、前記基板10の第1主面に、基板凸部11を有し、該凸部の底面14が上面13より断面幅広であり、若しくは基板面において底面14内に上面13が内包されており、該底面14の形状が略多角形状であり、該上面13が略円形状若しくは前記底面14の構成辺より多い構成辺の略多角形状である。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】異種材料の基板上に形成した平坦かつ薄い半導体基板であって、異種材料の基板からの剥離が容易な半導体基板、半導体装置及びそれらの製造方法を提供すること。

【解決手段】本発明によると、第1の面に所定の間隔で配置した複数の半球状の凸部を有する基板と、前記基板の第1の面に形成した第1の半導体層と、を有することを特徴とする半導体基板が提供される。また、前記複数の半球状の凸部の表面積の合計と前記第1の面との比は1以上である。

(もっと読む)

ミスカットバルク基板上にエピタキシャルプロセスを行う方法およびシステム

【課題】m方向に向かうミスカットが少なくとも0.35度であるc面表面を用いて、Ga面c面(Al、Ga、In)N基板上に(Al、Ga、In)N薄膜を形成する方法を提供する。

【解決手段】前記平滑な(Al、Ga、In)N薄膜624上に、発光素子を形成する。前記平滑な表面上に作製された素子は、向上した性能を示す。

(もっと読む)

エピタキシャル構造体及びその製造方法

【課題】本発明は、エピタキシャル構造体及びその製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つのエピタキシャル成長面を有する基板を提供する第一ステップと、前記基板のエピタキシャル成長面の上に複数の空隙を含むカーボンナノチューブ層を懸架するように配置する第二ステップと、前記基板のエピタキシャル成長面にエピタキシャル層を成長させて、前記カーボンナノチューブ層を包む第三ステップと、を含む。

(もっと読む)

半導体デバイスおよび方法

【課題】光照射に適合した、少なくとも1つの電位障壁、又は表面障壁を持つ半導体デバイスの製造または処理に関し、高い絶縁破壊電圧と、大電流で低いキヤリア密度を有するデバイスの製造方法を提供する。

【解決手段】a)基板1を用意するステップと、b)第1エピタキシャル半導体層3を基板1の上に設けるステップと、c)1次元または2次元の繰り返しパターンを形成するステップと、を含み、パターンの各部分が、0.1〜50の範囲のアスペクト比を有するようにした方法を開示する。対応する半導体デバイス、電子回路および装置も開示している。

(もっと読む)

エピタキシャル構造体の製造方法

【課題】簡単な製造方法を有し、コストが低く、高品質のエピタキシャル構造体の製造方法を提供する。

【解決手段】エピタキシャル構造体の製造方法は、少なくとも一つの結晶面を有する基板100を提供する第一ステップと、前記基板100の結晶面101に複数の空隙を含むカーボンナノチューブ層102を配置し、前記基板100の結晶面101の一部を前記カーボンナノチューブ層102の複数の空隙によって露出させる第二ステップと、前記基板100の結晶面101にエピタキシャル層104を成長させ、前記カーボンナノチューブ層102を覆う第三ステップと、前記カーボンナノチューブ層102を除去する第四ステップと、を含む。

(もっと読む)

エピタキシャル構造体の製造方法

【課題】本発明は、エピタキシャル構造体の製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つの結晶面を有する基板を提供する第一ステップと、前記基板の結晶面に複数の空隙を含むカーボンナノチューブ層を配置し、前記基板の結晶面の一部を前記カーボンナノチューブ層の複数の空隙によって露出させる第二ステップと、前記基板の結晶面にエピタキシャル層を成長させ、前記カーボンナノチューブ層を覆う第三ステップと、前記基板及び前記カーボンナノチューブ層を除去する第四ステップと、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明の実施形態は、表面に凹凸を加工した基板上に、低転位で均一な窒化物半導体層を形成できる半導体装置およびその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、主面上に凹凸構造が設けられた基板と、前記主面の全面に設けられ、p型不純物およびn型不純物の少なくともいずれかがドープされた、多結晶および非晶質の少なくともいずれかである窒化物層と、前記窒化物層の上に設けられた窒化物半導体層と、を備える。

(もっと読む)

半導体バルク結晶および半導体バルク結晶の製造方法

【課題】格子定数が下地基板と略等しい乃至同一の単結晶の化合物半導体結晶をエピタキシャル成長させるに当たり、当該化合物半導体結晶をクラックフリーのものとして大面積のエピタキシャル半導体基板を提供すること。

【解決手段】半導体バルク結晶の製造に際し、下地基板と化合物半導体単結晶との間に、下地基板と化合物半導体単結晶とが直接接する態様で空洞を形成したり、下地基板の主面に凹凸を形成し、さらに、化合物半導体単結晶のエピタキシャル成長方向に直交する結晶軸の下地基板の格子定数a1と化合物半導体単結晶の格子定数a2の差の比率である格子不整合度(2|a1−a2|/[a1+a2])を1×10-3以下とした。上記空洞や凹凸によりエピタキシャル成長途中におけるクラックの発生を抑制することができ、大面積のクラックフリーのエピタキシャル半導体バルク結晶を提供することができる。

(もっと読む)

III−V族発光デバイスを成長させるための基板

【課題】特性および信頼性を低下させることなくIII−V族発光デバイスを成長させるための基板を提供すること。

【解決手段】ホストおよび該ホストに接合されたシード層を含む基板が準備され、次いで、n型領域およびp型領域の間に配置された発光層を含む半導体構造が、前記シード層上に成長される。幾つかの実施形態では、接合層が、前記ホストを前記シード層に結合させる。シード層は、前記シード層に形成される転位によって、または前記シード層と前記接合層の間、即ちこれら二つの層間の界面での滑りによって半導体構造における歪みが解除されるように、前記半導体構造における歪みの緩和のための臨界圧力よりも薄くすることができる。幾つかの実施形態において、前記ホストは、前記接合層をエッチング除去することにより前記半導体構造およびシード層から分離されてよい。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】 基板表面や対向面の状態によらず、形成するシリコン膜の表面の平坦性を向上させる。

【解決手段】 基板が収容される処理室と、処理室内に少なくともシリコン含有ガスを供給するシリコン含有ガス供給系と、処理室内に少なくともホウ素含有ガスを供給するホウ素含有ガス供給系と、基板が収容された処理室内にホウ素含有ガス供給系からホウ素含有ガスを供給させ、基板の表面を、ホウ素元素が堆積された表面或いはホウ素元素により終端された表面に改質させた後、シリコン含有ガス供給系からシリコン含有ガスを供給させると共に、ホウ素含有ガス供給系からホウ素含有ガスを供給させ、改質された基板の表面上にシリコン膜を形成するよう制御する制御部と、を備える。

(もっと読む)

複数の非極性発光セルを有する発光素子

【課題】複数の非極性発光セルを有する発光素子及びその製造方法を提供すること。

【解決手段】この方法は、上部表面がr面、a面またはm面を有するサファイアまたは炭化珪素の第1の基板を用意することを含む。第1の基板は、その上部表面上にストライプ状の成長防止パターンを有し、また成長防止パターン間に側壁がc面であるリセス領域を有する。リセス領域を有する基板上に窒化物半導体層が成長され、窒化物半導体層をパターニングし、互いに分離された発光セルが形成される。これにより、優れた結晶品質の非極性発光セルを有する発光素子が提供される。

(もっと読む)

窒化物半導体構造

【課題】原子レベルで平坦な表面またはヘテロ界面を有する窒化物半導体構造を提供する。

【解決手段】窒化物半導体基板101は、(11−20)面を主方位面とするGaNであり、らせん成分を含む貫通転位104の密度は1×105cm−2であった。該基板上に複数の開口部103(1辺が20ミクロンの正方形)を有するマスク材102(酸化シリコン薄膜、厚さ100nm)が形成されている。該開口部には、n型GaN層106a、アンドープAlN層106b、アンドープGaN層106c、アンドープAlN層106d、および、n型GaN層106eが順次形成されている。様々な条件下で貫通転位104の密度と開口部103の面積との関係を検討すると、貫通転位密度がNcm−2である場合、各開口部103の面積が1/Ncm2以下であれば各開口部103内に形成した窒化物半導体多層薄膜の少なくとも一つの界面が平坦になることを見出した。

(もっと読む)

窒化物半導体の積層構造およびその製造方法並びに窒化物半導体装置

【課題】窒化物半導体積層体の結晶欠陥密度が低減可能な窒化物半導体の積層構造およびその製造方法並びに窒化物半導体装置を提供する。

【解決手段】窒化物半導体の積層構造は、基板10、第1バッファ層12、第1結晶層14、第2バッファ層16、第2結晶層20とを備える。基板10には、段差部10dが形成されている。第1バッファ層12は、InAlGaNを含み、段差下面10bと段差側面10cとを覆う。第1結晶層14は、前記第1バッファ層12の上に設けられ、InAlGaNを含み、前記基板10の上面10aよりも上方に設けられた上面14aを有する。第2バッファ層16は、InAlGaNを含み、前記第1結晶層14の前記上面14aと前記基板10の前記上面10aとを連続して覆う。第2結晶層20は、前記第2バッファ層16を覆い、InAlGaNを含み、前記第1の面20aを有する。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】面取り部の形状を再成形するとともに、裏面クラウンを完全に除去し、平坦性に優れた、パーティクルのほとんど無いエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】表裏の主面と該主面の外周の面取り部とからなるシリコン単結晶基板上にエピタキシャル層を成長させることによりエピタキシャルウェーハを製造する方法において、前記シリコン単結晶基板の前記裏面側の主面全面と前記裏面側の面取り部に裏面酸化膜を形成する工程と、該裏面酸化膜を形成したシリコン単結晶基板の表面側の主面上に、40μm以上の膜厚のエピタキシャル層を成長させる工程と、該エピタキシャル層表面に保護酸化膜を形成する工程と、該保護酸化膜を形成したシリコン単結晶基板の面取り部を研削及び研磨する工程と、その後、前記保護酸化膜を除去して、仕上げの洗浄を行う工程とを含むエピタキシャルウェーハの製造方法。

(もっと読む)

トレンチ埋め込みエピタキシャル成長条件の最適化方法

【課題】トレンチ埋め込みエピタキシャル成長の制御パラメータを変更した際にエピタキシャルの成長反応の変化傾向を簡便に知ることができ、結果として、最適な成長条件を簡便に見つけ出すことが可能な、トレンチ埋め込みエピタキシャル成長条件の最適化方法を提供する。

【解決手段】シリコンソースガスにエッチングガスを混合した混合ガスを原料ガスとし、この原料ガスをH2キャリアガスで流通させることにより、シリコン基板表面に形成したトレンチ内部にエピタキシャル層を成長させてトレンチ内部をエピタキシャル層で埋め込む工程を含む半導体基板の製造方法における、トレンチ内部をエピタキシャル層で埋め込む際のエピタキシャル成長の最適条件を求める方法であって、ある特定のアスペクト比のトレンチ内部を埋め込む際のエピタキシャル成長の最適条件をエピタキシャル成長速度のH2キャリアガスの流量依存性により求めることを特徴とする。

(もっと読む)

21 - 40 / 291

[ Back to top ]