Fターム[5F045AF12]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 基板の形状、構造、大きさ、厚み等 (845) | 基板表面の状態(面粗さ、ステップ等) (699)

Fターム[5F045AF12]の下位に属するFターム

結晶方位(面方位)オリフラ、ノッチ (341)

膜形成の核を被成膜面上に有するもの (67)

Fターム[5F045AF12]に分類される特許

81 - 100 / 291

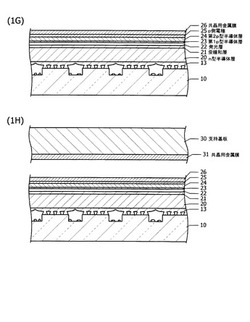

半導体素子の製造方法

【課題】 成長用基板の上に形成する半導体層が薄くても、再現性よく半導体層から成長用基板を分離する方法が望まれる。

【解決手段】 表面に凹凸が形成された成長用基板の、該表面の凸部の上面に離散的に分布し、化合物半導体からなる複数の支柱を形成する。支柱によって成長用基板の上に支えられ、化合物半導体からなる半導体層を形成する。半導体層の上に、支持基板を接着する。成長用基板を半導体層から分離する。

(もっと読む)

エピタキシャルウエハの製造方法

【課題】 半導体ウエハの端面に角張った形状の結晶層を成長させることなく、半導体ウエハ上に厚い単結晶層を成長させることができる技術を提供する。

【解決手段】 半導体ウエハ10上に単結晶層30が形成されたエピタキシャルウエハの製造方法であって、平坦な上面12と、平坦な下面14と、上面12と下面14を接続する端面16を有する半導体ウエハ10の端面16上に、アモルファス層20を形成するアモルファス層形成工程と、アモルファス層形成工程後に、半導体ウエハ10の上面12上に、80μm以上の厚みを有する単結晶層30を気相成長させる単結晶層形成工程を有する。

(もっと読む)

エピタキシャル成長用基板、窒化物系化合物半導体基板及び窒化物系化合物半導体自立基板

【課題】エピタキシャル成長用基板上に直接GaN系半導体厚膜層を成長させるGaN系半導体基板の製造方法により、GaN系半導体基板を生産性よく製造できる技術を提供する。

【解決手段】900℃〜1050℃の成長温度で窒化物系化合物半導体層を直接エピタキシャル成長させる際に、成長温度までの昇温プロセスにおいて表面粗さが10nmを超えて劣化しないエピタキシャル成長用基板を用いる。

具体的には、1200℃以上1400℃以下で5〜20時間保持するインゴットアニール処理を施されたNGO基板を用いる。

(もっと読む)

NGO基板、窒化物系化合物半導体基板の製造方法、窒化物系化合物半導体基板及び窒化物系化合物半導体自立基板

【課題】低温保護層の成長プロセスを省略でき、GaN系半導体基板の製造コストを低減できるとともに、低温保護層の品質のばらつきによる影響を排除できる窒化物系化合物半導体基板の製造方法を提供する。

【解決手段】平均表面粗さが0.2〜10nmに制御された成長用基板上に、窒化物系化合物半導体層をエピタキシャル成長させる。例えば、成長用基板をエピタキシャル成長装置に投入した後、成長用基板の平均表面粗さが0.2〜10nmとなるようにアニール処理を施す。

(もっと読む)

半導体装置の製造方法

【課題】サファイア基板上に高品質なIII族窒化物を結晶成長させ、高品質な半導体装置を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】直接窒化されたサファイア基板2上のAlN層にラジカル源5から窒素ラジカル又は窒素イオンを含む気体を所定時間照射する。その後、成長させるIII族窒化物の構成元素からなるターゲット3aに窒素雰囲気中でパルスレーザ光を照射するPLD(パルスレーザ堆積)法によってIII族窒化物を結晶成長させることにより、極めて高品質なN極性結晶を得ることができる。

(もっと読む)

結晶成長方法

【課題】凹凸を有する基板上に均一な結晶を成長させる結晶成長方法を提供する。

【解決手段】凹凸が設けられた主面を有する基板の前記主面に窒化物半導体の結晶を成長させる結晶成長方法であって、前記主面に、GaxAl1−xN(0.1≦x<0.5)を含み、厚さが20ナノメートル以上50ナノメートル以下のバッファ層を、0.1マイクロメートル/時以下の速度で堆積し、前記バッファ層の上に、前記バッファ層の堆積における前記基板の温度よりも高い温度で、窒化物半導体を含む結晶を成長させる。このように、バッファ層の堆積レートRtとバッファ層の平均の厚さTを適切に管理することにより、バッファ層の上に形成された窒化物半導体結晶の表面モフォロジーの良好な平坦性が実現できるとともに、結晶欠陥であるピット発生数Npをきわめて小さくすることができる。

(もっと読む)

窒化物半導体単結晶の製造方法

【課題】成長途中に生じる凹部を縮小させ、バルク状でかつ結晶性の高い窒化物半導体単結晶体の製造方法を提供する。

【解決手段】気相成長法による窒化物半導体単結晶の製造方法であって、種基板1との界面の裏側に主面および凹部を有する第1の窒化物半導体単結晶部2を前記種基板1上に成長させる工程と、前記凹部内にマスク4を設ける工程と、前記マスク4を覆うように前記第1の窒化物半導体結晶部2上に第2の窒化物半導体結晶部を成長させる工程と、を具備する。

(もっと読む)

窒化物半導体薄膜および窒化物半導体規則混晶ならびにその成長方法

【課題】従来よりも原子レベルで平坦な表面を有する窒化物半導体薄膜及びその成長方法を提供すること。

【解決手段】ミスカットを有するGaN基板101のステップフロー成長(第1の成長工程)により制限領域102内に形成されたテラス202に、第1の成長工程よりも大きな供給量でTMG又はTEGを供給する。これにより、テラス202の上にGaNの2次元核301が発生するが(図3(a)参照)、発生する2次元核301の個数が1個以上100個以下発生するだけの時間だけこの第2の成長工程を行う。次に、TMG又はTEGの供給量を、第2の成長工程よりも小さくする(第3の成長工程)。これにより、複数の2次元核301が横方向成長して1分子層の厚さの連続的なGaN薄膜302となる(図3(b)参照)。第2と第3の工程を交互に繰り返すことにより、2分子層以上の厚さのGaN薄膜303を成長することも可能である(図3(c)参照)。

(もっと読む)

N極性を有する発光ダイオードおよび関連する製造方法

N極性を有する発光ダイオード(「LED」)および関連する製造方法が本明細書に開示される。一実施形態では、基板材料を有する基板上に発光ダイオードを形成するための方法は、基板の表面上に基板材料の窒化産物を形成することなく、基板の表面に少なくとも近接して、窒素リッチな環境を形成することを含む。本方法はまた、窒素リッチな環境を有する基板の表面上に、窒素極性を有するLED構造を形成することを含む。 (もっと読む)

半導体基板、その製造方法、半導体デバイス及びその製造方法

【課題】異種材料の基板上で平坦かつ剥離が容易なGaN基板を低コストで製造することを可能にする製造方法を提供するとともに、そのGaN基板を用いて製造するLEDやレーザダイオード等の半導体デバイスの低コスト化、性能向上や長寿命化を実現することである。

【解決手段】本発明の半導体基板は、基板と、前記基板上に形成された第1の半導体層と、前記第1の半導体層上の一部領域に形成されたマスクと、前記第1の半導体層及び前記マスク上に当該マスクと交差する方向に所定のパターン形状で形成された金属性材料層と、前記第1の半導体層上及び前記金属性材料層上に形成された第2の半導体層と、前記金属性材料層より下層部分の前記第1の半導体層に形成された空洞と、を有する。

(もっと読む)

半導体発光素子

【課題】半導体層における応力を緩和し低動作電圧で高発光効率の半導体発光素子を提供する。

【解決手段】窒化物半導体を含むn型半導体層と、窒化物半導体を含むp型半導体層と、n型半導体層とp型半導体層との間に設けられ、互いに積層され、GaNを含む複数の障壁層と、複数の障壁層のそれぞれの間に設けられ、第1In組成比のInGaNを含む井戸層と、を有する発光部と、n型半導体層と発光部との間に設けられ、互いに積層され、GaNを含む複数の第1層と、複数の第1層のそれぞれの間に設けられ、第1In組成比の0.6倍以上で第1In組成比よりも低い第2In組成比のInGaNを含む第2層と、を有する多層構造体と、多層構造体と発光部との間に設けられ、Aly1Ga1−y1N(0<y1≦0.01)を含む第3層を含むn側中間層と、を備えたことを特徴とする半導体発光素子が提供される。

(もっと読む)

窒化ガリウム基板の製造方法

【課題】本発明の実施例は、窒化ガリウム基板の製造方法に関する。

【解決手段】実施例による窒化ガリウム基板の製造方法は、基板上にエッチング防止層を形成するステップと、前記エッチング防止層上に第1窒化ガリウム層を形成するステップと、シラン(silane)ガスで前記第1窒化ガリウム層を一部エッチングするステップと、前記エッチングされた第1窒化ガリウム層上に第2窒化ガリウム層を形成するステップと、前記第2窒化ガリウム層上に第3窒化ガリウム層を形成するステップと、を含む。

(もっと読む)

半導体デバイスの製造方法および半導体基板

【課題】ハンドリング時やデバイスプロセス時に基板の欠けや割れが発生し難い半導体デバイスの製造方法を提供する。

【解決手段】エッジ部が面取りされた半導体基板1の少なくとも表面および表面側の前記エッジ部を覆うように保護層2を形成する保護層形成工程と、この保護層形成工程の後に、半導体基板1の表面に形成された保護層2の一部の領域を除去する工程とを含む。保護層2は、半導体基板1の裏面および裏面側のエッジ部も覆うように形成する。

(もっと読む)

半導体発光素子及びその製造方法

【課題】 凹凸を有する基板上に形成する膜の表面が平坦になるまでの成長時間を短縮することが可能な半導体発光素子を提供する。

【解決手段】 コランダム構造のc面基板の表面に複数の凸部が形成されている。この表面に、Ga及びNを含むIII−V族半導体からなり、基板表面よりも平坦な下地膜が配置されている。下地膜の上に、Ga及びNを含む発光構造が配置されている。下地膜のa軸方向とのなす角度が15°未満の方向を第1方向とし、それと直交する方向を第2方向とする。凸部は、第1方向及び第2方向に規則的に配列している。凸部の各々は、m軸方向とのなす角度が15°未満の第1の辺と、a軸方向とのなす角度が15°未満の第2の辺とを有する。第1方向に隣り合う2つの凸部の相互に対向する第1の辺は平行であり、第2方向に隣り合う2つの凸部の相互に対向する第2の辺は平行である。対向する第2の辺のm軸方向の間隔は、対向する第1の辺のa軸方向の間隔よりも広い。

(もっと読む)

光電変換装置用の微結晶シリコン膜および光電変換装置

【課題】基板からの剥離を有効に抑制することができる半導体膜およびその半導体膜を含む光電変換装置を提供する。

【解決手段】基板の表面上に形成された結晶質を含む半導体膜であって、半導体膜の表面の中心を含む中心領域と、中心領域の周囲に位置する周縁領域とを有し、該半導体膜の周縁領域における結晶化率が中心領域における結晶化率よりも高い半導体膜およびその半導体膜を含む光電変換装置である。

(もっと読む)

シリコンウェーハ及びエピタキシャルウェーハ、並びにそれらの製造方法

【課題】シリコンウェーハにおける微細ダメージの直接的な抑制によって、ミリセックアニールによる熱応力にも耐えうる機械的強度を有するシリコンウェーハ及びエピタキシャルウェーハ、並びにそれらの製造方法を提供する。

【解決手段】本発明のシリコンウェーハの製造方法は、両面を鏡面研磨したシリコンウェーハ(10)の端面を含む表面全体に、膜厚が10nm以上の酸化膜(20)を形成する工程と、該酸化膜(20)を除去して表面に存在する微細ダメージを低減する工程とを含む。また、本発明のエピタキシャルウェーハの製造方法は、両面を鏡面研磨したシリコンウェーハ(10)の端面を含む表面全体に、膜厚が8nm以上の酸化膜(20)を形成する工程と、該酸化膜(20)を除去して表面に存在する微細ダメージを低減する工程と、酸化膜(20)を除去したシリコンウェーハの表面に、エピタキシャル層(30)を形成する工程とを含む。

(もっと読む)

シリコンオンインシュレータウェハを処理する方法

ハンドルウェハ、シリコン層、及び上記ハンドルウェハと上記シリコン層との間の誘電体層を含むシリコン−オン−インシュレータ構造上においてエピタキシャル層をエッチング及び/又は析出させる方法を提供する。当該シリコン層は、当該構造の外表面を規定する劈開された表面を有する。その後、エッチング反応が速度論的に制限されるように炉の温度を制御しつつ上記劈開された表面をエッチングする。その後、上記劈開された表面の析出速度が速度論的に制限されるように炉の温度を制御しつつ上記ウェハ上にエピタキシャル層を析出させる。  (もっと読む)

(もっと読む)

基板、テンプレート基板、半導体発光素子、半導体発光素子の製造方法、半導体発光素子を用いた照明装置および電子機器

【課題】発光ダイオードの光取り出し効率を向上できる基板を提供する。

【解決手段】半導体発光素子LCは、一方の面に複数の六角錐状の凸部110bが設けられた基板110と、凸部110bが設けられた面に接触するように設けられた下地層130と、下地層130に接触して設けられるn型半導体層140と、n型半導体層140に接触して設けられる発光層150と、発光層150に接触して設けられるp型半導体層160とを備えている。凸部110bは、半導体発光素子LC内において、横方向および斜め方向に向かう光を散乱し、半導体発光素子LCからの光取り出し効率を向上させる。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.7×10-3以下であり、主表面の面方位が、結晶基板のc軸を含む面から[0001]方向に−10°以上10°以下の傾斜角を有する。

(もっと読む)

III族窒化物結晶半導体基板の製造方法、及びIII族窒化物結晶半導体基板

【課題】III族窒化物結晶半導体基板の裏面を簡単にかつ均一に粗化することができるIII族窒化物結晶半導体基板の製造方法を提供する。

【解決手段】III族窒化物結晶半導体基板の製造方法において、1)III族窒化物結晶のN面を研削及び/又は研磨する工程と、2)該N面に不揮発性有機物を付着させた後にエッチングを行う裏面処理工程とを含む。これにより、III族窒化物結晶半導体基板はN面に多角錐が均一に形成され、その高さもおおよそ揃っており、マクロ的に見るとN面が均一に粗化されるので、III族窒化物結晶半導体基板上にエピタキシャル層を成長させる際の基板とサセプタと密着度が良好で、温度分布が均一になりやすく、エピタキシャル層を均一に成長させることができる。

(もっと読む)

81 - 100 / 291

[ Back to top ]