Fターム[5F048AB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | メモリ (1,087)

Fターム[5F048AB01]に分類される特許

101 - 120 / 1,087

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体集積回路装置

【課題】I/O用バルク部とコアロジック用SOI部が混載されたバルク&SOIハイブリッド型CMISデバイスでは、閾値電圧制御の最適化のため多数のゲートスタックを用いる必要があり、プロセス及び構造が複雑になるという問題がある。

【解決手段】本願発明は、High−kゲート絶縁膜およびメタルゲート電極を有するSOI型半導体CMISFET集積回路装置において、いずれかのバックゲート半導体領域に不純物を導入することにより、対応する部分のMISFETの閾値電圧を調整するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体基板の作製方法

【課題】半導体基板の欠陥を低減する。また、歩留まり高く欠陥の少ない半導体基板を作製する。また、歩留まり高く半導体装置を作製する。

【解決手段】支持基板に酸化絶縁層を介して半導体層を設け、該半導体層の端部における、支持基板及び酸化絶縁層の密着性を高めた後、半導体層の表面の絶縁層を除去し、半導体層にレーザ光を照射して、平坦化された半導体層を得る。半導体層の端部において、支持基板及び酸化絶縁層の密着性を高めるために、半導体層の表面から、レーザ光を照射する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置及びその製造方法

【課題】活性領域におけるイオン濃度のばらつきを抑制すること。

【解決手段】半導体装置の製造方法は、半導体基板にイオンを注入するための第1開口を有し、第1層ウェルを形成するための第1マスクを半導体基板上に形成する工程と、第1マスクを用いて半導体基板に第1イオンを注入して、第1領域及び第2領域を有する第1層ウェルを形成する工程と、半導体基板にイオンを注入するための第2開口を有し、第2層ウェルを形成するための第2マスクを半導体基板上に形成する工程と、第2マスクを用いて半導体基板に第2イオンを注入して、第1層ウェルより下方に位置する第2層ウェルを形成する工程と、を含む。第1領域を第2領域より第1層ウェルの外縁寄りに形成する。第1イオンを注入する際に、第1マスクの第1内壁面で反射した第1イオンを第1領域に供給する。第2イオンを注入する際に、第2マスクの第2内壁面で反射した第2イオンを第2領域に供給する。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

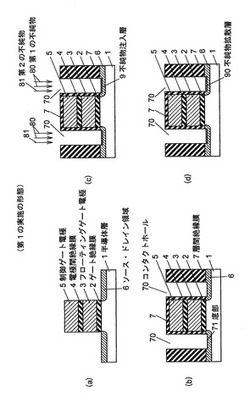

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極GE2の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極GE2側に位置する側壁部において、第1の斜面と、第1の斜面と交差する第2の斜面と、を有する。このように、溝g2の形状をΣ形状とすることで、pチャネル型電界効果トランジスタのチャネル領域に加わる圧縮歪みを大きくすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置

【課題】 制御端子が浮遊状態になると、予期しないリーク電流などにより電極に電荷が蓄積され、電極の電位が変動し、スイッチが誤動作してしまう可能性がある。

【解決手段】 クーロン力により湾曲させることで第1の信号電極と第2の信号電極とを接触または分離することが可能な架橋部と、前記架橋部を制御するための制御端子とを有するスイッチ素子と、前記制御端子に接続された第1の不揮発性半導体素子と、前記制御端子および前記第1の不揮発性半導体素子に接続された第2の不揮発性半導体素子とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域をライン上に形成することで、コンタクト領域のばらつきを抑制し、リセスゲート電極を用いて隣接するトランジスタ間の分離を行う構造を提供する。

【解決手段】半導体基板中に第1の方向に延在して形成される素子分離領域で分離された活性領域と、第1の方向と交差する第2の方向に延在し、素子分離領域及び活性領域に連通する溝内に形成されたリセスゲート電極と。リセスゲート電極で分断された活性領域であって、リセスゲート電極の底面より浅い領域に形成されるMOSトランジスタのソース/ドレイン領域とを備えた半導体装置であって、リセスゲート電極は、MOSトランジスタのゲート電極を構成する制御ゲート電極162tと、第1の方向に隣接するMOSトランジスタを素子分離する補助ゲート電極162iで構成される。

(もっと読む)

半導体装置

【課題】バイアス切替の前後でドレイン電流の大きさが変化しない縦型トランジスタを実現する。

【解決手段】半導体装置1は、第1の下部拡散層6A、第1の上部拡散層7A、及び第1のゲート電極9Aを有する第1の縦型トランジスタ4Aと、第2の下部拡散層6B、第2の上部拡散層7B、及び第2のゲート電極9Bを有する第2の縦型トランジスタ4Bと、第1及び第2のゲート電極9A,9Bに接続されるゲート配線と、第1の下部拡散層6A及び第2の上部拡散層7Bに接続される第1の配線W1と、第1の上部拡散層7A及び第2の下部拡散層6Bに接続される第2の配線W2とを備える。

(もっと読む)

101 - 120 / 1,087

[ Back to top ]