Fターム[5F048AB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | メモリ (1,087)

Fターム[5F048AB01]に分類される特許

141 - 160 / 1,087

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

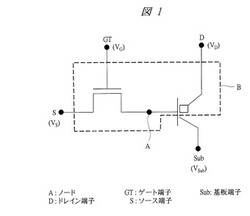

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】LSI中の高耐圧MOSFETを含む高耐圧回路は、純粋な内部回路と異なり、外部との関係で動作電圧が高い状態で固定されているため、通常のように、低電圧化による微細化が適用できない。このため、内部回路部の低電圧化に伴って、ますます、チップ内の占有面積を肥大化させる結果となっている。この問題について、本願発明者等が、各種の対策について評価したところによると、CMOSFET回路構成およびデバイス構成との適合性等の問題がネックとなっていることが明らかとなった。

【解決手段】本願発明は、各チャネル表面に波状起伏が設けられたNチャネル型およびPチャネル型MISFETを有する半導体集積回路装置において、Pチャネル型MISFETのチャネル表面に設けられた波状起伏に比べて、Nチャネル型MISFETのチャネル表面に設けられた波状起伏のピッチを狭くしたものである。

(もっと読む)

半導体装置の製造方法

【課題】高さのばらつきが低減された埋め込みビット線を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板内にビット線とワード線を有する半導体装置の製造方法において、半導体基板をエッチングして第1の方向に延在する第1の溝を形成することによって、複数の第1の半導体ピラーを形成する工程と、第1の半導体ピラーの側面の一部に拡散層を形成する工程と、隣接する前記第1の半導体ピラー間の前記第1の溝に、拡散層に接続するビット線を形成する工程と、第1の半導体ピラーと前記ビット線を覆う第1の絶縁膜を形成する工程と、第1の半導体ピラーの少なくとも一部が露出するように前記第1の絶縁膜に、第1の方向に直交する第2の方向に延在する第2の溝を形成する工程と、露出した第1の半導体ピラー上にエピタキシャル層を成長させて第2の半導体ピラーを形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程を追加せずに、アライメントマークの形成領域におけるゲート電極膜の残渣を低減する。

【解決手段】半導体装置の製造方法は、アライメントマーク10を有する第1領域R1と、抵抗体40が形成される第2領域R2と、ゲート電極15が形成される第3領域R3と、を主面1aに有する基板の主面1a上に、金属材料を含有するゲート電極膜11を形成する工程を有する。更に、第1及び第2領域R1、R2のゲート電極膜11を等方性エッチングにより除去する工程を有する。更に、ゲート電極膜11を除去した第2領域R2と、第3領域R3と、に導電膜(ポリシリコン膜13)を成膜する工程を有する。更に、導電膜を成膜する工程の後に、基板の主面1a上にフォトレジスト膜を形成し、アライメントマーク10をアライメントに用いて所定のパターンをフォトレジスト膜に転写する工程を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

パルス変換回路

【課題】回路面積を低減する。

【解決手段】第1の信号が入力され、第2の信号を出力する論理回路を具備し、論理回路は、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧に設定するか否かを制御するP型トランジスタと、エンハンスメント型であり、閾値電圧の絶対値がP型トランジスタより大きく、ゲートに第1の信号が入力され、ゲートの電圧に応じて第2の信号の電圧を第1の電圧より高い第2の電圧に設定するか否かを制御するN型トランジスタと、を備え、P型トランジスタは、チャネルが形成され、第14族の元素を含有する半導体層を含み、N型トランジスタは、チャネルが形成され、キャリア濃度が1×1014/cm3未満である酸化物半導体層を含む。

(もっと読む)

半導体装置

【課題】ラッチ回路を有する半導体装置におけるデータの破壊を抑制する。

【解決手段】ラッチ回路に含まれる第1トランジスタP4と、ラッチ回路に含まれ、第1トランジスタP4と共通のウェル40内に形成された、第1トランジスタP4と同じ導電型の第2トランジスタP1と、第1トランジスタP4と第2トランジスタP1との間に設けられ、ウェル40を電源に接続するウェルコンタクトWCと、を備える。第1トランジスタP4側のウェル40内で発生した電荷は、ウェルコンタクトWCに流れるため、第1トランジスタP4におけるソフトエラーの影響が、第2トランジスタP1に伝搬することを抑制することができる。これにより、ラッチ回路内における2箇所のノードにおいて、同時に論理の反転が生じることを抑制することができるため、データの破壊を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

半導体装置及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第2導電型のソース領域、第2導電型のドレイン領域、及び、第1導電型のボディ領域と、第2ゲート絶縁膜と、第2ゲート電極と、を含む第2トランジスターと、を具備し、第1トランジスターの第2導電型のボディ領域は、第2トランジスターの第2導電型のソース領域及び第2導電型のドレイン領域の内の一方に接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル領域のトランジスタにおけるソース/ドレイン電極上の半導体層同士の接触による短絡を防止しつつ、周辺回路領域のトランジスタにおけるせり上げソース/ドレイン領域を含むソース/ドレイン電極の高濃度不純物層の接合深さの均一性を図り、短チャネル効果を抑制する。

【解決手段】メモリセル領域における隣接するトランジスタ間で半導体層同士が接触しない膜厚にエピタキシャル成長させ、その際、周辺回路領域の素子分離2のみを後退させて露出した基板面からもエピタキシャル成長半導体層10を成長させることで、周辺回路領域の半導体層のファセットFが活性領域外に形成されるようにし、その後、周辺回路領域に高濃度不純物層11用のイオン注入を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法

【課題】複数のスタンダードセルを有する半導体装置のチップ面積をさらに小さくする。

【解決手段】半導体装置SD1は第1および第2スタンダードセルSC1,SC2を備える。第1スタンダードセルSC1は、拡散領域An11、拡散領域An11に対向する機能素子領域FE1、および金属層MT11を有する。第2スタンダードセルSC2は、拡散領域An11に連続する拡散領域An21、拡散領域An21に対向する機能素子領域FE2、ならびに拡散領域An21および機能素子領域FE2の間に形成された拡散領域CR21を有する。金属層MT11および機能素子領域FE2は、拡散領域An11、拡散領域An21、および拡散領域CR21通して電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】FEOLにおいても半導体装置のチャージングを効果的に抑制できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に、被保護素子のゲート絶縁膜となる第1の絶縁膜122を形成する工程(a)と、保護素子部302において第1の絶縁膜122の少なくとも一部を除去する工程(b)と、工程(b)よりも後に、被保護素子部301において第1の絶縁膜122の表面を窒化する工程(c)と、工程(c)よりも後に、被保護素子部301及び保護素子部302の上に跨るように導電膜を選択的に形成することにより、互いに接続された被保護素子のゲート電極141及び保護素子の電極142を形成する工程(d)とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

半導体装置

【課題】最小加工寸法がフィン幅となるFinFETの構造において、極めて制御が困難なリング形状の加工を不要として、加工ばらつきに起因する特性ばらつきの小さなユニットセルを提供する。

【解決手段】ユニットセルは、半導体基板1上に形成された開ループ構造のゲート電極Gと、前記ゲート電極Gの内方となる領域にフィン状に形成されたドレイン領域2と、前記ゲート電極Gの外方となる領域に形成されたフィン状のソース領域3とを有する。前記ドレイン領域2の上にはドレインコンタクト2aが形成され、前記ソース領域3上にはソースコンタクト3aが形成される。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

141 - 160 / 1,087

[ Back to top ]