Fターム[5F048AB01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 用途 (4,368) | メモリ (1,087)

Fターム[5F048AB01]に分類される特許

61 - 80 / 1,087

半導体装置

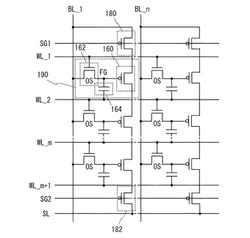

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、単位面積あたりの記憶容量を増加させる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体装置

【課題】動作速度の低下を抑制しつつ、消費電力を低減する。

【解決手段】第1の半導体領域の上に絶縁領域を有し、且つ絶縁領域の上に第2の半導体領域を有する基板に設けられた第1の電界効果トランジスタと、基板の上に設けられた絶縁層と、絶縁層の一平面に設けられ、酸化物半導体層を含む第2の電界効果トランジスタと、第2の電界効果トランジスタのソース及びドレインと同一工程により形成され、第1の電界効果トランジスタの閾値電圧を制御するための電圧が供給される制御端子と、を備える。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体デバイスのための非対称スペーサ構造体を形成する方法

【課題】 デバイスのゲートとソースとの間の低い直列抵抗を維持し、同時に、ゲートからドレインへの過剰なオーバーラップによって形成される悪影響を最小限にするFETデバイスの製造を可能にする。

【解決手段】半導体基板の上に少なくとも1対の隣接して離間配置された、オフセット・スペーサ114を備えるゲート構造体102の上にスペーサ層132を形成するステップであって、ゲート構造体は、スペーサ層がゲート構造体間の領域で第1の厚さで形成され、その他の場所で第2の厚さで形成されるように離間配置され、第2の厚さは第1の厚さより厚い、ステップと、1対の隣接して離間配置されたゲート構造体のオフセット・スペーサに隣接して非対称スペーサ構造体124a、bを形成するようにスペーサ層をエッチングするステップとを含み、非対称スペーサ構造体は、ソース及びドレイン領域の画定において用いられる。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置

【課題】周辺の回路構成を複雑にすることなく、繰り返しのデータの書き込みの際の劣化を低減することが可能な、不揮発性スイッチとして用いる半導体装置を提供する。

【解決手段】電源電圧が停止しても導通状態に関するデータの保持を、チャネル形成領域に酸化物半導体層を有する薄膜トランジスタに接続されたデータ保持部で行う構成とする。そしてデータ保持部は、ダーリントン接続された電界効果トランジスタ及びバイポーラトランジスタを有する電流増幅回路における、電界効果トランジスタのゲートに接続することでデータ保持部の電荷をリークすることなく、導通状態を制御する。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の表面に導入された不純物を、前記表面の浅い領域に高精度かつ高濃度で分布させ、不純物が半導体基板の深い領域に拡散することを防ぐことで、半導体装置の歩留まりおよび性能を向上させ、装置の微細化を容易にする。

【解決手段】N型MISトランジスタにおいて、半導体基板300に打ち込まれた炭素が、同じ領域に打ち込まれたホウ素を引き寄せる性質を利用し、ホウ素をN型の不純物として注入したハロー領域306に炭素を共注入して炭素注入層307を形成する。これにより、ホウ素が増速拡散することを防ぎ、ハロー領域306を高い精度で形成することを可能とすることで、微細化された半導体素子の短チャネル効果の発生を抑制する。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置

【課題】プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出

来る半導体装置を提供することを課題の一とする。

【解決手段】リセット動作及び初期化動作により所定の電位が記憶されたメモリ回路を有

する半導体装置において、トリガー信号の供給に応じて、メモリ回路の書き換えが行われ

る回路を設ける構成とする。そして、メモリ回路の書き換えにより、半導体装置に流れる

電流を負荷に流す構成とすることで、サイリスタとしての機能を実現しうる半導体装置と

する。

(もっと読む)

半導体装置の製造方法

【課題】 CMOS型半導体装置におけるデュアルゲート構造のゲート電極をエッチングにより形成する時に、局所的なゲート絶縁膜の「突き抜け」やゲート電極サイドエッチ等の欠陥が発生することを防止できる製造方法を提供する。

【解決手段】 ゲート絶縁膜5を介して半導体基板1上に形成されたシリコン膜等の、実質的に不純物を含まない半導体膜6を選択的にエッチングしてゲート電極7を形成する。隣接するゲート電極7間の領域をレジスト等の絶縁膜9で埋め込む。さらに例えば所定のゲート電極7が形成された領域を覆うマスク層10を形成し、絶縁膜9とマスク層10とをマスクとして、マスク層10で覆われないゲート電極7にイオン注入等の手段により所定導電型の不純物を導入する。同様の方法を用いてマスク層10で覆われていたゲート電極7に異なる導電型の不純物を導入する。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

半導体集積回路装置

【課題】同じ拡散層に形成されて対照的な動作を行うトランジスタは、拡散層に対して対照的に配置されるのが一般的である。この固定観念を捨てることで、半導体集積回路装置の設計に係る制約の一部を回避し、サイズダウンおよび製造コストの節約を可能とするレイアウトを用いた半導体集積回路装置を提供する。

【解決手段】本発明によれば、同じ拡散層に形成されて対照的な動作を行う2つのトランジスタを、あえて非対称的に配置することで、半導体集積回路装置のさらなるサイズダウンが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

61 - 80 / 1,087

[ Back to top ]