Fターム[5F048BA02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997)

Fターム[5F048BA02]の下位に属するFターム

3層以上 (202)

基板と直上の層が同型 (184)

基板と直上の層が異型 (194)

Fターム[5F048BA02]に分類される特許

21 - 40 / 417

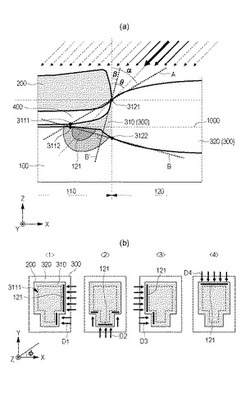

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低減し、かつ高耐圧で駆動することが可能な半導体装置を提供する。

【解決手段】当該高耐圧トランジスタは、第1の不純物層PEPと、第1の不純物層PEPの内部に形成される第2の不純物層HVNWと、第2の不純物層HVNWを挟むように、第1の不純物層PEPの内部に形成される1対の第3の不純物層OFBおよび第4の不純物層PWと、第3の不純物層OFBから、第2の不純物層HVNWの配置される方向へ、主表面に沿って突出するように、第1の不純物層PEPの最上面から第1の不純物層PEPの内部に形成される第5の不純物層OFB2と、第2の不純物層HVNWの最上面の上方に形成される導電層GEとを備える。第4の不純物層PWにおける不純物濃度は、第3および第5の不純物層OFB,OFB2における不純物濃度よりも高く、第5の不純物層OFB2における不純物濃度は、第3の不純物層OFBにおける不純物濃度よりも高い。

(もっと読む)

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

電界効果トランジスタ及びその製造方法、並びに半導体装置

【課題】横型二重拡散構造を有する電界効果トランジスタの高集積化を可能とする半導体装置を提供する。

【解決手段】半導体装置1Nは、ゲート電極17の幅方向両側のうちの一方の側で延在するP型ボディ領域20Pと、他方の側で延在するN型ボディ領域20Nと、その一方の側に形成されてP型ボディ領域20Pと接合するP型不純物拡散領域32Pと、その他方の側でP型不純物拡散領域32Pと対向する位置に形成されてN型ボディ領域20Nと接合するN型不純物拡散領域32Nと、その一方の側に形成されてP型ボディ領域30Nと接合するN型不純物拡散領域31Nと、その他方の側でN型不純物拡散領域31Nと対向する位置に形成されてN型ボディ領域20Nと接合するP型不純物拡散領域31Pとを備える。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体装置

【課題】半導体素子が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断できる半導体装置を提供すること。

【解決手段】半導体装置100を構成するパワー半導体素子を小さな半導体素子1に分割し、この小さな半導体素子1にそれぞれ1本のボンディングワイヤ17を接続する。小さな半導体素子1が短絡破壊したとき、破壊した小さな半導体素子1に接続するワイヤ17(ヒューズの役割をさせる)を溶断し、且つ、制御回路30からオフ信号を健全な半導体素子1に与える。このようにして、半導体装置100が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断することができる。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

半導体装置

【課題】不要な寄生素子の影響を排除できる低容量の過渡電圧保護素子を提供する。

【解決手段】半導体基板上に第1のエピタキシャル層210を形成し、第1のエピタキシャル層の表面近傍に埋め込み層220を形成し、埋め込み層上に第2のエピタキシャル層211を形成し、第2のエピタキシャル層内に第1のディープ拡散層250を形成し、第1のディープ拡散層内にツェナーダイオードを形成し、ツェナーダイオードから離れた位置に第1のPNダイオードを形成し、ツェナーダイオードは第1の分離層240により分離されており、第1のPNダイオードは第2の分離層241で分離されており、ツェナーダイオードと第1のPNダイオードが埋め込み層を経由して逆方向に直列接続されることにより、不要な寄生素子の影響を排除でき、かつ低容量の過渡電圧保護素子を実現する。

(もっと読む)

シンクロナス整流器或いは電圧クランプ用の3端子パワーMOSFETスイッチ

【課題】パワー変換器に於けるシンクロナス整流器として適するMOSFETスイッチを提供する。

【解決手段】互いに接続されソース及びボディが、ドレンよりはより正の側に高い電圧にバイアスされたN−チャネルパワーMOSFETを製造する。ゲートはスイッチ(1184)により制御され、ゲートを、ソース及び当該MOSFETのチャネルを完全にオンにするのに十分な電圧(VCP)のいずれか一方に選択的に接続する。ゲートがソースに接続されたとき、デバイスは、比較的低い電圧でオンし、従来のPN接合よりは低い導通抵抗を有する「擬似ショットキー」ダイオードとして機能する。ゲートが、前記した正の電圧に接続されたとき、MOSFETのチャネルは完全にオンとなる。このMOSFETスイッチは、電力損及び“break-before-make”時間に於ける蓄積電荷を低減する。

(もっと読む)

半導体装置

【課題】少数キャリアの過剰な蓄積に起因するリカバリ耐量の低下を抑制し、リカバリ損を効果的に低減し得る半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板101の表面(第1主面)側にエミッタ電極107及びゲート電極105が形成され、裏面(第2主面)側にコレクタ電極113が形成されたIGBT素子100と、半導体基板101の一方の主面側にP導電型のアノード領域が形成され、他方の主面側にN導電型のカソード領域が形成されたFWD素子20とを備えている。そして、FWD素子20の配置領域Xfにおける裏面(第2主面)側には、P導電型の吸収領域22が部分的に設けられており、IGBT素子100に隣接する側の方が、IGBT素子100から離れた側よりも、カソード領域21に対する吸収領域22の比率が大きくなっている。

(もっと読む)

半導体装置

【課題】出力トランジスタの形成領域から他の素子の形成領域への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体基板SUBと、1対の注入元素子DRと、アクティブバリア構造ABと、p型接地領域PGDとを備える。半導体基板SUBは主表面を有し、かつ内部にp型領域を有する。1対の注入元素子DRは、p型領域上であって主表面に形成される。アクティブバリア構造ABは、主表面において1対の注入元素子DRに挟まれる領域に配置される。p型接地領域PGDは、主表面において1対の注入元素子DRに挟まれる領域を避けて1対の注入元素子DRおよびアクティブバリア構造ABよりも主表面の端部側に形成され、かつp型領域に電気的に接続された、接地電位を印加可能な領域である。p型接地領域PGDは、1対の注入元素子DRに挟まれる領域と隣り合う領域において分断されている。

(もっと読む)

横型素子を有する半導体装置

【課題】高速スイッチング動作を行う場合でも、アバランシェブレークダウンを抑制でき、スイッチング損失低減や素子破壊を抑制することが可能な構成とする。

【解決手段】横型FWD7などの横型素子において、SRFP21の全抵抗Rの抵抗値を90kΩ〜90MΩ、好ましくは270kΩ〜27MΩ、より好ましくは900kΩ〜9MΩとすることにより、2ndピーク時のアノード電流IAなどの電流が大きくなることを抑制できる。これにより、高速スイッチング動作を行う場合でもアバランシェブレークダウンを抑制でき、横型FWD7のスイッチング損失低減や素子破壊を抑制することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

半導体装置

【課題】特性をさらに向上する半導体装置を提供する。

【解決手段】高電圧側電界効果トランジスタ20aの高電圧側ドレイン電極11aと、高電圧側ドレイン電極11aの一側方に間隔をおいて形成される高電圧側ゲート電極12aと、高電圧側ゲート電極12aの一側方に間隔をおいて形成され、高電圧側電界効果トランジスタ20aのソース電極であり、低電圧側電界効果トランジスタ21aのドレイン電極であるソース兼ドレイン電極13aと、ソース兼ドレイン電極13aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ゲート電極14aと、低電圧側ゲート電極14aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ソース電極15aとを有する。

(もっと読む)

半導体装置の製造方法

【課題】高性能・高信頼性の半導体装置を製造するための半導体装置の製造方法を提供する。

【解決手段】半導体基板上に保護膜を形成し、保護膜を介して不純物をイオン注入する。注入した不純物を活性化して不純物層を形成した後、保護膜を除去する。その後、不純物層の表面部の半導体基板を除去し、表面部を除去した半導体基板上に半導体層をエピタキシャル成長する。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2の不純物層及び第1のエピタキシャル半導体層よりも薄い第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上にゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

21 - 40 / 417

[ Back to top ]