Fターム[5F048BA02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997)

Fターム[5F048BA02]の下位に属するFターム

3層以上 (202)

基板と直上の層が同型 (184)

基板と直上の層が異型 (194)

Fターム[5F048BA02]に分類される特許

61 - 80 / 417

半導体装置及びその製造方法

【課題】側面に(110)面が形成されたGe若しくはSiGeのフィン構造を実現することができ、FinFET等の素子特性の向上に寄与する。

【解決手段】Ge若しくはSiGeのフィン構造部を有する半導体装置であって、Si基板10の表面部に、一方向に長いストライプ領域を挟むように埋め込み形成され且つ基板表面よりも高い位置まで形成された素子分離絶縁膜12と、ストライプ領域上に形成され、且つ最上面が前記素子分離絶縁膜の最上面よりも低い位置にあるSiGeバッファ層14と、バッファ層14上に形成され、該層14よりも一方向と直交する方向の幅が狭く基板面と垂直な(110)面を有するGeフィン構造16と、を備えた。

(もっと読む)

半導体装置

【課題】ショットキー電極を設けなくても閾値が低く、高耐圧化が可能な半導体装置を提供する。

【解決手段】N+型のカソード層1が、カソード電極100に接合して形成され低不純物濃度のN型のドリフト層2が、カソード層1に接合して形成され、複数のトレンチ4a、4bが、ドリフト層2の上面に所定の間隔を隔てて配列され、埋め込み電極5a、5bが、トレンチ4a、4bの内部に、絶縁膜6a、6bを介してそれぞれ形成され、トレンチ間領域7隣り合うトレンチ間に形成され、高不純物濃度のP+層31および高不純物濃度のN+層32を交互に配列してアノード電極200に接合させたユニバーサルコンタクト層3が、トレンチ間領域7に接合して形成される。トレンチ間領域7の熱平衡状態のポテンシャルが調整されて、ドリフト層2の熱平衡状態のポテンシャルとの差が、使用する半導体材料のバンドギャップに依存するビルトイン電圧よりも低い。

(もっと読む)

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

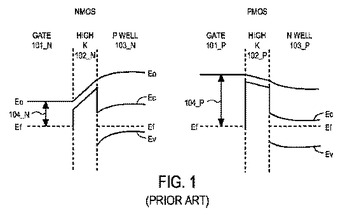

デュアル仕事関数ゲート構造

トランジスタを有する半導体チップが記載されている。前記トランジスタは、ゲート誘電体にわたって設けられたゲート電極を有する。前記ゲート電極は、前記ゲート誘電体上に設けられた第1ゲート材料、及び前記ゲート誘電体上に設けられた第2ゲート材料を有する。前記第1ゲート材料は前記第2ゲート材料とは異なる。前記第2ゲート材料はまた、前記ゲート電極のソース領域又はドレイン領域にも設けられている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ダイオード領域とIGBT領域の間に形成される分離構造を深くすることなく、境界部における逆電流を抑制することができる半導体装置を提供する。

【解決手段】半導体装置10は、ダイオード領域20とIGBT領域40を有する半導体基板12を備えている。半導体基板12には、ダイオードドリフト領域28とIGBTドリフト領域50の間に、分離構造70とライフタイム制御領域41が形成されている。ライフタイム制御領域41のキャリアライフタイムは、ダイオードドリフト領域28及びIGBTドリフト領域50のキャリアライフタイムより短い。ライフタイム制御領域41の上端部は分離構造70に接続している。

(もっと読む)

パワー・スイッチの構造および方法

【課題】低RDSonおよび低電流制限の両方を提供する一方で、ホット・スポットおよび熱暴走の効果を低減する回路を提供する。

【解決手段】本発明の一実施例において、パワー・スイッチング・デバイス(33)は、第1MOSFETデバイス(41)および第2MOSFETデバイス(42)を含む。第1ゲート電極(48,87)を含む分割ゲート構造(84)は、第1MOSFETデバイス(41)を制御する。第2ゲート電極(49,92)は、第2MOSFETデバイス(42)を制御する。電流制限デバイス(38)は、第1ゲート電極(48,97)に結合され、電流制限モード中に第1MOSFETデバイスをオンにする。比較器デバイス(36)は、第2ゲート電極(49,92)に結合され、パワー・スイッチング・デバイス(33)が電流制限モードでなくなったときに、第2MOSFETデバイス(42)をオンにする。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

HOT(hybridorientationtechnology)を選択的エピタキシーに関連して用いて移動度を改善する方法およびそれに関連する装置

半導体装置が、第1の基板(102、202)と、第1の基板の第1の部分の上に位置し、埋め込み層(104、204)によって第1の基板から分離される第2の基板とを含む。この半導体装置はまた、第1の基板の第2の部分の上に位置し、第2の基板から隔離されるエピタキシャル層(108、220)を含む。この半導体装置はさらに、少なくとも部分的に第2の基板内に形成される第1のトランジスタ(116)と、少なくとも部分的にエピタキシャル層内またはその上に形成される第2のトランジスタ(128)とを含む。第2の基板およびエピタキシャル層は、異なる電子および正孔移動度を有するバルク特性を有する。トランジスタの少なくとも1つは、少なくとも約5Vの1つまたは複数の信号を受け取るように構成される。第1の基板は第1の結晶面方位を有し、第2の基板は第2の結晶面方位を有し得る。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 固相エピタキシャル成長によって、所望の面方位を有する結晶を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、第1の面方位を有するシリコン基板11上の一部に、アモルファス層13を形成する工程と、そのアモルファス層13にマイクロ波を照射し、前記アモルファス層13を第1の面方位を有する結晶層とする工程とを有していることを特徴とする半導体装置の製造方法を提供することができる。

(もっと読む)

蓄積型FINFET、回路、及びその製造方法

【課題】FinFET、集積回路、およびFinFETの形成方法を提供する。

【解決手段】基板120、前記基板上にあり、ソース106とドレイン110との間のチャネル108を含み、前記ソース106、前記ドレイン110、および前記チャネル108は、第1型ドーパントを有し、前記チャネル108は、ゲルマニウム、シリコンゲルマニウム、またはIII−V族半導体の少なくとも1つを含むフィン構造、前記チャネル108上のゲート誘電体層114、および前記ゲート誘電体層114上のゲート116を含むFinFET。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

炭化珪素絶縁ゲート電界効果トランジスタを用いたインバータ回路および論理ゲート回路

【課題】動作速度を高速化できる SiC MISFETで構成された論理ゲート回路デバイスを得る。

【解決手段】nチャネルエンハンスメント型SiC MISFET(22)と、nチャネルデプリーション型SiC MISFET(22、22b)とでインバータ、NAND/NOR論理ゲート回路を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで性能向上が可能なBiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】n型の半導体基板1の表面から所定の深さに、コレクタ領域を構成するn型の不純物領域26を備える。当該不純物領域26の上方、かつ半導体基板1に形成されたシャロートレンチ分離14で挟まれた領域18にはp型のベース領域20を備える。ベース領域20には、n型の半導体膜からなるエミッタ電極が接触して設けられている。当該半導体装置は、不純物領域26がベース領域20下からシャロートレンチ分離14下まで延在し、当該シャロートレンチ分離14を貫通して不純物領域26に電気的に接続するコンタクトプラグ52を備える。

(もっと読む)

半導体装置の製造方法

【課題】CMP工程でその表面が研削され、平坦化された層間絶縁膜IL中にドライエッチングによりコンタクトホール20a等を形成する時、素子分離絶縁膜8a上に形成された最上層がシリサイド層12b、下層がポリシリコン層12aからなる配線層12の、該シリサイド層12bがオーバーエッチングにより消失することを防止する。

【解決手段】N+型埋め込み層2形成時に生じたシリコン段差に起因してN型エピタキシャル層4の表面にも段差が生じる。係る段差の高い部分に形成されたP型分離層5の上に素子分離絶縁膜8aを形成する。該素子分離絶縁膜8a上に上層がシリサイド層12b、下層がポリシリコン層12aからなる配線層12を形成するが、配線層12を形成する前に該素子分離絶縁膜8aの薄膜化を行い、配線層12最上層のシリサイド層12b表面とN+型ソース層15等の表面間の段差を、該素子分離絶縁膜8aの薄膜化する前に比べ小さくする。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体装置

【課題】半導体装置が形成された後においても、定常損失とスイッチング損失を調整することができる半導体装置を提供する。

【解決手段】第1導電型の第1半導体層、及び該第1半導体層における一方の主面側の表層に形成された少なくとも1つの第2導電型の第2半導体層を有する半導体基板と、第1半導体層における他方の主面に形成された第1電極と、第1半導体層における一方の主面に形成された第2電極と、を備え、第1電極と第2電極との間に電流が流れるダイオードを有する半導体装置であって、第1半導体層における一方の主面側に、第1半導体層に流入するキャリアの注入量を制御する制御信号を入力するための制御パッドと、該制御パッドと電気的に接続された制御電極と、該制御電極と第2電極、及び制御電極と半導体基板を絶縁する絶縁部材と、が形成されている。

(もっと読む)

半導体装置

【課題】隣接する保護装置を備える半導体装置において、クロストークノイズの低減を実現する。

【解決手段】本発明に係る半導体装置に備えられた隣接位置に配置される保護装置50A,50Bは、第1導電型半導体基板1と、第1導電型ウェル12と、保護対象の回路の端子に接続された第2導電型の第1の領域22、21cと、第1の電圧が印加される、第2導電型の第2の領域21b、21dと、第1導電型ウェル12を囲むように形成された第2導電型ガードリングウェル23と、ガードリングウェル23の深層部に接触し、第1の領域22、21cに接触せずに隣接して形成された第2導電型深層領域24と、第1導電型ウェル12よりも不純物濃度が高く、第2導電型深層領域24より下層に配置され、第1の領域22の下層から、少なくともその近傍領域の第2導電型深層領域24までに亘って形成された第1導電型深層領域14とを備える。

(もっと読む)

半導体装置、半導体装置の制御方法、半導体モジュール

【課題】MOSFETと、MOSFETと逆並列となるSBDとが同一半導体基板に形成された半導体装置において、還流ダイオードのリカバリ特性の改善と、MOSFETのアバランシェ耐量の確保との両立が可能な技術を提供する。

【解決手段】MOSFETのソース領域に接するソース電極と、ベース領域に制御電極と、SBDに接するSBD電極とを備える。MOSFETのオン時には、アバランシェ破壊の発生を抑制するように、制御電極とSBD電極の電位を制御する。還流時には、MOSFETの寄生ダイオードに電流が流れないように制御電極とSBD電極の電位を制御して、SBDに電流が流れるようにし、リカバリ特性を向上させる。

(もっと読む)

半導体装置及びその製造方法

【課題】ホール移動度を向上し、ジャンクションリークを低減する。

【解決手段】DSB(Direct Silicon Bonded)基板は、第1の基板および第2の基板を含み得る。ここで、第2の基板は、第1の基板に比べて、45度の結晶方位ねじれ角に回転され得る。閾値電圧(Vt)に基づいて調整された厚さを備えるDSB基板を含む半導体装置および半導体装置の製造方法が開示されている。言い換えると、より厚い基板または層が高閾値電圧(HVt)に対応し、より薄い基板または層が低閾値電圧(LVt)に対応し得る。この薄膜化により、LVt装置において、さらに移動度が向上する。

(もっと読む)

制御可能なサージ電流耐性を有するパワースイッチング素子

半導体スイッチング素子は、ワイドバンドギャップパワートランジスタと、前記パワートランジスタと並列に接続されたワイドバンドギャップサージ電流トランジスタと、前記サージ電流トランジスタを駆動するように構成された駆動トランジスタを含む。前記半導体スイッチング素子の、オン状態での出力電流のほぼすべては、前記パワートランジスタのドレイン−ソース電圧が第一の電圧範囲内にあるときには、前記パワートランジスタのチャネルを通って流れる。当該第一の電圧範囲は、例えば、通常動作中に期待されるドレイン−ソース電圧に対応し得る。その一方で、前記半導体スイッチング素子は、さらに、オン状態で、前記パワートランジスタのドレイン−ソース電圧が第二の(より高い)電圧範囲内にあるときには、出力電流が、前記サージ電流トランジスタ、および前記パワートランジスタのチャネルの両方を通って流れるように構成される。 (もっと読む)

61 - 80 / 417

[ Back to top ]