Fターム[5F048BA02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 多層基板(2層) (997)

Fターム[5F048BA02]の下位に属するFターム

3層以上 (202)

基板と直上の層が同型 (184)

基板と直上の層が異型 (194)

Fターム[5F048BA02]に分類される特許

101 - 120 / 417

半導体装置

【課題】 同一基板上に形成された半導体素子間に流れる寄生電流による半導体素子の誤動作を抑制する構造を有する半導体装置を提供することを目的とする。

【解決手段】

p型半導体基板1に電気的に接続されたn型のコレクタ引き出し層53を備えた小信号素子であるバイポーラトランジスタ50と、p型半導体基板1に電気的に接続されたn型拡散層67を備えたパワートランジスタ素子であるDMOSトランジスタ60と、p型半導体基板1に電気的に接続され、かつ、ダミー電極13に接続されたn型のダミーN島10と、p型半導体基板1に電気的に接続され、かつ、フィールド電極23に接続されたp型のフィールド部20と、ダミー電極13とフィールド電極23を接続し、ボンディングパット70に接続する配線30とを備える。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供する。

【解決手段】基層10内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層40内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域21Bと、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域44Bと、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域51Bとを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧で、基板への電流の漏れが抑制され、かつ、端子に負入力があった場合でも基板から端子への電流の抜けが抑制されたダイオードを基板上に有する半導体装置およびその製造方法を提供すること。

【解決手段】P型基板1と、P型基板1上に順次形成されたN型埋め込み層2、P型埋め込み層3、およびN型エピタキシャル層4と、P型埋め込み層3上に形成されN型エピタキシャル層4を囲むP型拡散層6と、ゲート領域を構成するP型拡散層8およびP型拡散層11と、ソース領域を構成するN型拡散層9、P型拡散層12およびN型拡散層13と、N型エピタキシャル層4の上方に形成されP型拡散層12およびN型拡散層13と短絡したゲート電極と、を備え、N型埋め込み層2はフローティング状態にある。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのしきい値のばらつきを抑制する。

【解決手段】半導体基板1に素子分離領域2を形成し、MISFETのしきい値調整用のチャネルドープイオン注入を行なってから、ゲート絶縁膜5a,5bおよびゲート電極GE1,GE2を形成する。それから、イオン注入によりエクステンション領域7a,7bおよびハロー領域8a,8bを形成し、更に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することにより拡散防止領域10a,10bを形成する。その後、ゲート電極GE1,GE2の側壁上にサイドウォールSWを形成してから、イオン注入により、ソース・ドレイン用のn+型半導体領域11aおよびp+型半導体領域11bを形成して、nチャネル型MISFETおよびpチャネル型MISFETが形成される。

(もっと読む)

半導体装置の製造方法

【課題】微細加工が求められる半導体装置であるBiCMOSの製造方法に関し、特に半導体基板上に形成されるエピタキシャル層の表面の平坦性を向上することを課題とする。

【解決手段】本発明のBiCMOSの製造方法は、P型シリコン基板1の主面をエッチングしてくぼみ部32を形成する第1工程と、くぼみ部32を被覆するシリコン酸化膜22をマスクにして当該P型シリコン基板1にN+型埋め込み層2を形成する第2工程と、N+型埋め込み層2を含むP型シリコン基板1の主面を熱酸化して、P型シリコン基板1上にシリコン酸化膜22を含むシリコン熱酸化膜25を形成する第3工程と、シリコン熱酸化膜25を除去した後、N+型埋め込み層2を含むP型シリコン基板1の主面上にN型エピタキシャル層を形成する第4工程と、を含む。

(もっと読む)

半導体装置

【課題】設計時の配置、又はプロセスばらつきによってパイプライン処理を行う各ステージ毎に処理速度が異なる。そこで、本発明の目的は、各段の処理機構が独立して動作でき、それらが同じ一定の時間内で処理が終了できるプロセッサの設計および製造を行うできる装置を提供することである。

【解決手段】複数段のステージ分割されたパイプライン処理を行う演算器において、各段が独立に動作することが求められている各段及びステージ毎に、独立に各段及びステージを構成しているMOSトランジスタのしきい値電圧を製造後において変化させる。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する複数の電気素子要素と、複数の電気素子要素を覆う、シリコンを含まない下層保護絶縁膜と、下層保護絶縁膜の上に配置され、シリコンを含む上層保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、複数の電気素子要素の少なくとも一つは、シリサイド化される金属を含有でき、下層保護絶縁膜は、電気素子要素に含有される金属と上層保護絶縁膜に含有されるシリコンとの接触を阻害できる。下層保護絶縁膜は、比誘電率が10以上の高誘電体層を有してよい。上層保護絶縁膜は、シリコンおよび窒素を含有することができる。

(もっと読む)

半導体装置の製造方法

【課題】Siおよびこれと同族元素であるGe,Cなどの組合せを用いて、低消費電力で高速なMOSFETを有する半導体装置の製造方法を提供する。

【解決手段】Si層1と、その上に形成されたMOSFETのゲート電極16と、Si層1に形成されたソース領域14及びドレイン領域15と、それらの間の領域に形成されるチャネル領域とを有する半導体装置の製造方法において、ソース領域14またはドレイン領域15が形成される領域のSi層1を選択的にエッチングし、形成された溝内にSiGeを選択成長させる。

(もっと読む)

半導体装置及びその製造方法

【課題】 素子分離絶縁膜の微細化、及びMOSトランジスタの性能向上を図る。

【解決手段】

第1のMOSトランジスタと第2のMOSトランジスタを有する半導体装置において、第1のMOSトランジスタ11が形成される半導体基板100の第1の領域10と、第1の領域10に隣接され、かつ第2のMOSトランジスタ21が形成される半導体基板100の第2の領域20と、第1領域10と第2領域20の間に形成された第1の素子分離絶縁膜30と、第1領域10に形成された複数層の半導体エピタキシャル層12とを有し、第1の素子分離絶縁膜30のアスペクト比が6.7以上である半導体装置。

(もっと読む)

半導体装置

【課題】半導体基板内に縦型のスイッチング素子群が設けられている半導体装置において、スイッチング素子領域内の局所的な温度上昇を抑制する。

【解決手段】半導体装置100の半導体基板内に、縦型のスイッチング素子群が設けられているスイッチング素子領域50を備えている。スイッチング素子領域50は、第1領域51と第2領域52を有している。第1領域51には、バイポーラ構造の第1スイッチング素子群が設けられている。第2領域52には、ユニポーラ構造の第2スイッチング素子群が設けられている。第2スイッチング素子群は、第1スイッチング素子群の間に設けられている。

(もっと読む)

半導体装置

【課題】MOSトランジスタのESD耐量を向上することが可能な半導体装置を提供する。

【解決手段】半導体装置100は、MOSトランジスタ1と、多結晶シリコンからなる多結晶シリコンダイオードが複数直列に接続されて構成された第1のダイオード回路116と、第1のダイオード回路の複数の多結晶シリコンダイオードの逆方向降伏電圧の総和よりも低い逆方向降伏電圧を有し、単結晶シリコンからなる第1の単結晶シリコンダイオード18と、多結晶シリコンからなる多結晶シリコンダイオードが複数直列に接続されて構成された第2のダイオード回路117と、第2のダイオード回路の複数直列に接続された多結晶シリコンダイオードの逆方向降伏電圧の総和よりも低い逆方向降伏電圧を有し、単結晶シリコンからなる第2の単結晶シリコンダイオード19を備える。

(もっと読む)

P型電界効果トランジスタ及びその製造方法

【解決手段】GaAsを用いることができる基板(1)の上方にn層(3)が配置され、前記n層上にp層(4)が配置される。前記p層は、ゲート電極(10)によって2つの別個の部分に分けられ、ソース及びドレインが形成されている。前記ゲート電極は、ゲート絶縁膜(6)によって半導体材料から絶縁されている。ソース/ドレインコンタクト(11)が、前記p層の前記2つの別個の部分に電気的に接続されている。 (もっと読む)

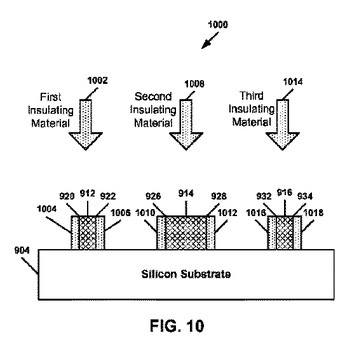

フィン電界効果トランジスタ(フィンFET)デバイスの製造方法

フィン電界効果トランジスタ(フィンFET)を用いた半導体の製造方法が開示される。特定の実施形態の方法は、第一の幅によって離隔された第一の側壁及び第二の側壁を有する第一のダミー構造体をシリコン基板上に堆積させるステップを含む。また、本方法は、第一のダミー構造体を堆積させるのと同時に第二のダミー構造体をシリコン基板上に堆積させるステップも含む。第二のダミー構造体は、第二の幅によって離隔された第三の側壁及び第四の側壁を有する。第二の幅は第一の幅よりも実質的に大きい。第一のダミー構造体を用いて略第一の幅によって離隔された第一の対のフィンを形成する。第二のダミー構造体を用いて略第二の幅によって離隔された第二の対のフィンを形成する。  (もっと読む)

(もっと読む)

半導体装置

【課題】優れた特性を有し、IC化に適した起動回路を提供する。

【解決手段】N型エピタキシャル層12に形成され、ドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成される。ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ドレイン領域121と、ゲートとして機能するP型分離領域13とドレイン領域121に印加される電圧により、P型素子分離領域13が逆バイアスされて空乏層が延びるチャネル領域を介して、JFETのソース引出層23が配置され、JFETが形成される。

(もっと読む)

半導体装置

【課題】回路の小型化を可能とする、トレンチ構造を有する半導体装置を提供すること。

【解決手段】第1n型半導体層11と、第2n型半導体層12と、p型半導体層13と、p型半導体層13を貫通して、第2n型半導体層12に達するトレンチ3と、n型半導体領域14と、ゲート絶縁部5と、このゲート絶縁部5により、第2n型半導体層12、p型半導体層13およびn型半導体領域14と絶縁されており、少なくとも一部がトレンチ3内部に形成されたゲート電極41と、n型半導体領域14と導通しているソース電極42と、を備えた半導体装置Aであって、ショットキー電極d1をさらに備え、ショットキー電極d1は、ソース電極42と導通しており、かつ、p型半導体層13、n型半導体領域14およびゲート電極41と絶縁されており、ショットキー電極d1と第2n型半導体層12とがトレンチ3内で接合されることにより、ダイオードを形成している。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置されるためトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、素子領域の端部のセルではソースパッド部からゲートパッド部を迂回するように電流経路が形成される領域があった。

【解決手段】電極構造を2層とし、ゲートパッド部の少なくとも一部に保護ダイオードとの非重畳領域を形成する。非重畳領域下方にセルおよび1層目のソース電極層を配置でき、ソース電極層内の抵抗の偏りを小さくできる。更に、ゲートパッド部から保護ダイオードまでの距離が、ソースパッド部から保護ダイオードまでの距離より小さくなる位置に保護ダイオードを配置する。これにより効率的にトランジスタ動作を行える素子領域を大きく確保でき、且つ配線部下方の第1ソース電極層抵抗を低減できる。

(もっと読む)

半導体装置

【課題】チップの占有面積を有効に活用する。

【解決手段】P型半導体基板11上にN型エピタキシャル層12が形成され、LDMOSとJFETに共通なドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成され、ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ボディ領域15とP型素子分離領域13との間にJFETのソースとなるN型領域が形成される。ドレインに正のドレイン電圧が印加されると、PN接合が逆バイアスされ、ボディ領域15と分離領域13と半導体基板11とから空乏層が延び、JFETのチャネルを制御する。

(もっと読む)

ポリエミッタ型バイポーラトランジスタ、BCD素子、ポリエミッタ型バイポーラトランジスタの製造方法及びBCD素子の製造方法

【課題】複合高電圧素子工程を用いたポリエミッタ型バイポーラトランジスタ及びその製造方法、BCD(複合高圧)素子及びその製造方法を提供する。

【解決手段】実施の形態に係るポリエミッタ型バイポーラトランジスタは、半導体基板100の上側の一部に形成された埋込層110と、上記半導体基板の上に形成されたエピ層120と、上記エピ層に形成され、上記埋込層と連結されるコレクタ領域130と、上記エピ層の上側の一部に形成されたベース領域140と、上記ベース領域の基板の表面に形成され、ポリシリコン材質からなるポリエミッタ領域170と、を含む。実施の形態に係るBCD素子は、ポリシリコン材質からなるポリエミッタ領域を含むポリエミッタ型バイポーラトランジスタを含み、上記バイポーラトランジスタと同一な単一ウエハ上に形成されたCMOSとDMOSのうちの1つ以上のMOSを含む。

(もっと読む)

半導体基材内に材料層を製造する方法

【課題】半導体基材内に深く伸びる極薄異材料層を製造する方法を提供する。

【解決手段】半導体基材内に異材料層が配置された半導体素子を製造するための方法であって、対向し合う2つの各側壁と底部とを有するトレンチを上記半導体基材内に作成する工程と、上記トレンチの上記2つの各側壁のうちの第1の側壁に異材料層を作成する工程と、上記トレンチの上記2つの各側壁のうちの第2の側壁および底部に半導体材料をエピタキシャルに堆積することによって上記トレンチを充填する工程とを含んでいる方法。

(もっと読む)

窪み付きゲート構造を有するメモリデバイス及びその製造方法

【課題】本発明は、IC(integrated circuit)の集積度が向上し、しかもショートチャネル効果を防止することができるMOS半導体デバイスを形成する方法を提供する。

【解決手段】DRAMアクセストランジスタのようなメモリデバイスであって、窪み付きゲート構造を有するメモリデバイスを形成する方法が開示されている。まず、絶縁用のフィールド酸化物領域(21)が半導体基板上に形成され、ついで、窒化シリコン層(18)にパターン形成が行われ、エッチングによりトランジスタトレンチ(22)が得られる。その後にデポジットされたポリシリコンであって、ゲート構造形成のためのポリシリコンを、隣接し隆起した窒化シリコン構造に対して研磨できるようにするため、このトランジスタトレンチに隣接するフィールド酸化物領域に窪みが設けられる。

(もっと読む)

101 - 120 / 417

[ Back to top ]