Fターム[5F048BB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 形状 (2,378) | ゲート長(幅)の異なる複数MOS (639)

Fターム[5F048BB03]に分類される特許

121 - 140 / 639

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

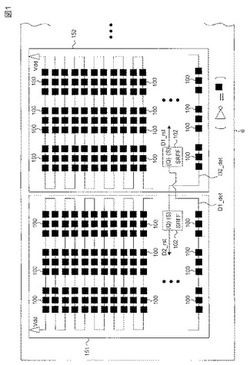

半導体集積回路及びデータ処理システム

【課題】意図的に誤動作を生じさせるための局所的な光照射を検出するための構成を小さなチップ占有面積で実現し、検出感度を高くする。

【解決手段】ロジック回路(6)が形成された領域に分散され初段の入力が一定論理値にされて直列的に接続された複数個の検出インバータ(100)を検出素子として採用し、単数又は複数のインバータに光が照射されて各々に出力が反転することによって直列的に接続された複数個の検出インバータの最終出力が判定され、これにより局所的な光照射を検出することができる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

ESD保護回路及び半導体装置

【課題】ESD保護回路に使用するMOSトランジスタのオフリーク電流を低減して、信号端子の端子リーク電流を低減する。

【解決手段】ESD保護回路100は、MOSトランジスタ10(又は20)を備える。MOSトランジスタ10(又は20)は、ドレイン端子とソース端子が信号端子2と電源VDD(又はGND)にそれぞれ接続され、ソース端子に印加されるVDD(又はGND)の電位よりも絶対値が大きく、ゲート端子とソース端子間の制御電圧が逆バイアスとなる電位VH(又はVL)がゲート端子に印加される。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチの数が1個のトレンチゲート構造のトランジスタをトレンチの数が2個以上のトレンチゲート構造のトランジスタとともに基板上に形成する際の特性の差異を低減する。

【解決手段】半導体装置100は、ゲート幅方向に断続的に深さが変化するように形成されたn個のトレンチ162を有するトランジスタであって、n=1の第1のトランジスタ200とn=2以上の第2のトランジスタ202と、各トランジスタが形成された領域の周囲に形成されて当該トランジスタが形成された領域を区分けする素子分離絶縁膜110と、を含む。ここで、第1のトランジスタ200のゲート幅方向における一つのトレンチ162と素子分離絶縁膜110との間の間隔cxが、第2のトランジスタ202のゲート幅方向におけるトレンチ162間の間隔axよりも狭い。

(もっと読む)

半導体装置およびその製造方法、pチャネルMOSトランジスタ

【課題】nチャネルMOSトランジスタにおいてhigh−Kゲート絶縁膜をhigh−K誘電体膜と酸化ランタン膜の積層により構成した半導体装置において、酸化ランタン膜のパターニングプロセスを不要とする半導体装置の製造方法を提供する。

【解決手段】界面酸化膜22上に形成されたhigh−K誘電体膜23上に酸化膜24を形成する工程と、前記high−K誘電体膜に窒化物層25を形成する工程と、前記窒化物層および前記酸化膜を第1の素子領域21Aから選択的に除去し、第1および第2の素子領域21Bにわたり酸化ランタン膜26を形成し、前記第1の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化ランタン膜を積層した第1の積層構造を、また前記第2の素子領域においては前記界面酸化膜と前記high−K誘電体膜と前記酸化膜と前記窒化物層と前記酸化ランタン膜を積層した第2の積層構造を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】ロジック系CMOSトランジスタおよびパワー系DMOSトランジスタのそれぞれが最適な構造を有する半導体装置を提供する。

【解決手段】第1半導体領域2の表面側に設けられた第1ソース領域3、ドレイン領域4と、第1ゲート13と、第1ゲートの両側面に形成された第1サイドウォール15と、第1LDD領域17とを有する第1のMOSトランジスタと、第2半導体領域22の表面側に設けられた第2ソース領域23、ドレイン領域24と、第2ゲート33と、第2ゲートの第2ドレイン側の側面に形成され、第1サイドウォールよりも広い第2サイドウォール41と、第2サイドウォール直下に形成されたドリフト領域43と、第2ゲートの第2ソース側の側面に形成され、第1サイドウォールよりも狭い第3サイドウォール35と、第3サイドウォール直下に形成された第2LDD領域37とを有する第2のMOSトランジスタを備えた半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動電流が大きくリーク電流の少ない低消費電力のMISトランジスタを有する半導体装置及びその製造方法を提供する。

【解決手段】チャネル領域を有する半導体基板と、チャネル領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、半導体基板内にチャネル領域を挟むように配置されたソース拡散層及びドレイン拡散層と、ソース拡散層側の半導体基板内に形成された第1のポケット不純物層と、ドレイン拡散層側の半導体基板内に形成された第2のポケット不純物層とを有し、第1のポケット不純物層は、ソース拡散層のエクステンション不純物層の濃度ピーク位置よりも深い位置に濃度ピークを有しており、第2のポケット不純物層は、ドレイン拡散層のエクステンション不純物層の濃度ピーク位置よりも浅い位置に濃度ピークを有している。

(もっと読む)

半導体装置

【課題】LCDドライバのチップサイズを縮小させる

【解決手段】シリコン基板上に構成されたLCDドライバDRV1を有する半導体装置であって、LCDドライバDRV1は、ソース出力回路領域RSに配置され、データ信号VDを生じる複数のソース出力セルCS1と、そのデータ信号VDを受けて外部に送信するための複数の出力パッドPD1とを有する。複数の出力パッドPD1はシリコン基板上の行方向に沿って並んで配置され、複数のソース出力セルCS1は行方向に沿って2行N列に並んで配置されている。特に、第1行第N列目に配置するソース出力セルCS1は、第(2N−1)番目の出力パッドPD1に電気的に接続され、第2行第N列目に配置するソース出力セルCS1は、第(2N)番目の出力パッドPD1に電気的に接続されている。

(もっと読む)

薄膜集積回路の作製方法

【課題】シリコンウェハからなるICチップは厚いため商品容器自体に搭載する場合、表

面に凹凸が生じ、デザイン性が低下してしまった。そこで非常に膜厚の薄い薄膜集積回路

、及び薄膜集積回路を有するICチップ等を提供する。

【解決手段】薄膜集積回路を有するICチップは、従来のシリコンウェハにより形成され

る集積回路と異なり、半導体膜を能動領域(例えば薄膜トランジスタであればチャネル形

成領域)として備えることを特徴とする。このようなICチップは非常に薄いため、カー

ドや容器等の商品へ搭載してもデザイン性を損ねることがない。

(もっと読む)

半導体装置

【課題】占有面積を増やすことなくロジック回路領域におけるトランジスタ特性の変動が抑制される半導体装置を提供する。

【解決手段】NMOS領域の素子形成領域4と、この素子形成領域4に隣り合う他の素子形成領域4との間隔(ゲート幅方向)が一定の間隔(距離2×LA)に設定されている。また、この素子形成領域4と、この素子形成領域4に隣り合う素子形成領域8との間隔(ゲート幅方向)も一定の間隔(距離2×LA)に設定されている。

(もっと読む)

半導体装置の製造方法

【課題】同一の半導体基板上にゲート絶縁膜の膜厚の異なる半導体素子領域を容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板に素子分離絶縁膜を形成することにより、第1の半導体素子領域と第2の半導体素子領域とを画定する工程と、前記第2の半導体素子領域と前記第2の半導体素子領域を囲う前記素子分離絶縁膜を覆い、前記第1の半導体素子領域と前記第1の半導体素子領域を囲う前記素子分離絶縁膜を露出させるマスクを形成する工程と、前記マスクを用いて、前記第1の半導体素子領域を囲う前記素子分離絶縁膜をエッチングする工程と、前記素子分離絶縁膜をエッチングする工程の後、前記マスクを用いて前記第1の半導体素子領域に対して異方性エッチングを行う工程と、前記マスクを除去する工程と、前記マスクを除去した後に熱酸化により第1の半導体素子領域と第2の半導体素子領域とにゲート酸化膜を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体集積回路装置

【課題】近年のCMOS型LSIの設計においてはリーク電力の削減が非常に大きな課題となっている。リーク電力を削減する手段としてはトランジスタの閾値電圧を複数使用し、速度の必要な場所には閾値電圧の低いトランジスタを、不要な場所には閾値電圧の高いトランジスタを使用する方法が広く用いられている。しかしながら先端プロセスほど閾値電圧制御だけではリーク電力が十分に抑制できず、様々なリーク電力削減手法が必要となってきている。

【解決手段】本願の一つの発明は、CMOSまたはCMIS型LSIにおいて、一部の論理ゲートを構成するPチャネルFETおよびNチャネルFETの両側のゲート電極形状を近接効果を利用して平面的に湾曲させることによって、実効的なゲート長を長くするものである。

(もっと読む)

半導体装置及びその製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを集積する場合に製造工程数の削減を実現できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、アクティブ領域11を横断しゲート電極10Aよりも長さが短いゲート電極10Bを形成する工程と、ゲート電極10A,10Bをマスクとして、アクティブ領域11に不純物を斜めイオン注入することにより、ゲート電極10Aのゲート長方向両側の領域に互いに連続しない不純物拡散領域20a,20bを形成するとともに、ゲート電極10Bのゲート長方向両側の一方の領域から他方の領域に亘って連続する不純物拡散領域20g,20hを形成する斜めイオン注入工程とを含む。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタと、酸化物半導体以外の半導体材料を用いて構成された論理回路と、を有し、前記トランジスタのソース電極またはドレイン電極の一方と、前記論理回路の少なくとも一の入力とは電気的に接続され、前記トランジスタを介して、前記論理回路に少なくとも一の入力信号が供給される半導体装置である。ここで、トランジスタのオフ電流は1×10−13A以下であるのが望ましい。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と高電圧トランジスタとの高濃度不純物拡散領域を同時にイオン注入で形成し、且つ高電圧トランジスタ側の方が浅くなるように形成する。

【解決手段】シリコン基板1にメモリセル領域にゲート電極MG、SGを形成し(図3(b))、周辺回路領域にゲート電極PG(図3(c))を形成する。周辺回路領域のゲート電極PGは、高電圧トランジスタについては厚い膜厚のゲート絶縁膜11が形成されている。ゲート絶縁膜11を残した状態でTEOS酸化膜9を成膜し、スペーサ加工をする。この時、スペーサ9aを形成すると共に、ゲート絶縁膜11を半分程度エッチングして11aとする。TEOS酸化膜10を形成後に高濃度不純物拡散領域1d、1eをイオン注入で深さd1、d2で形成する。高電圧トランジスタについてはゲート絶縁膜11aを介して行うので、浅く形成される。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

内燃機関点火装置用半導体装置

【課題】エネルギー耐量、負サージ耐量を確保しながら、できる限り低コストの内燃機関用点火装置用半導体装置を提供すること。

【解決手段】IGBTが前記コレクタ電極とゲート電極間にクランプダイオードを備え、IGBTのp+25とn型ベース層26の間に不純物濃度の異なる2層のn型バッファ層24、50を有するIGBTであって、前記2層のバッファ層の合計厚さが50μm以下であって、総不純物量を20×1013cm-2以下とする。

(もっと読む)

121 - 140 / 639

[ Back to top ]