Fターム[5F048BB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 形状 (2,378) | ゲート長(幅)の異なる複数MOS (639)

Fターム[5F048BB03]に分類される特許

81 - 100 / 639

半導体装置及びその製造方法

【課題】低電圧トランジスタ及び高電圧トランジスタの双方の要求を満たし、高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】ボロン又はリンを含む第1の不純物層と、第1の不純物層上に形成された第1のエピタキシャル層と、第1のエピタキシャル層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1のソース/ドレイン領域とを有する第1のトランジスタと、ボロン及び炭素又は砒素を含む第2の不純物層と、第2の不純物層上に形成された第2のエピタキシャル層と、第2のエピタキシャル層上に、第1のゲート絶縁膜よりも薄い第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1,第2のゲート電極の実効ゲート長が短くなることを防止する。

【解決手段】第1のMISトランジスタnTr1は、第1のゲート電極18aにおけるゲート幅方向の側面上に形成された第1のオフセットサイドウォール22aと、第1のゲート電極におけるゲート長方向の側面及びゲート幅方向の側面上に第1のオフセットサイドウォールを介して形成された第2のオフセットサイドウォール24aと、第1のエクステンション領域26aとを備えている。第2のMISトランジスタnTr2は、第2のゲート電極18bにおけるゲート長方向の側面及びゲート幅方向の側面上に形成された第3のオフセットサイドウォール22bと、第2のゲート電極におけるゲート長方向の側面及びゲート幅方向の側面上に第3のオフセットサイドウォールを介して形成された第4のオフセットサイドウォール24bと、第2のエクステンション領域23bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にhigh−k膜を使用したMIS構造の半導体装置において、互いに異なる仕事関数を有する複数の同一導電型トランジスタを設けることを可能にする。

【解決手段】同じ導電型の第1のMISトランジスタ及び第2のMISトランジスタが同じ半導体基板50上に設けられている。第1のMISトランジスタにおけるゲート絶縁膜52aの界面層2Aの厚さは、第2のMISトランジスタにおけるゲート絶縁膜52bの界面層2bの厚さよりも厚い。

(もっと読む)

半導体装置の製造方法、および電気機器

【課題】半導体装置の製造方法において、高電圧トランジスタのゲート耐圧を確保し得る程度の厚いゲート酸化膜の形成時に、この厚いゲート酸化膜が素子領域とトレンチ分離領域との境界で薄膜化するのを抑制することができ、しかも、サイズの小さい低電圧トランジスタの活性領域で、トレンチ分離溝の側壁部分での基板材料の酸化に起因した結晶欠陥が発生するのを防止する。

【解決手段】半導体基板101の表面に、半導体素子が形成されるべき素子領域を分離するようトレンチ分離領域100c、100f、100gを形成した後、該トレンチ分離領域を覆い、かつトレンチ分離領域からはみ出して該トレンチ分離領域に接する素子領域に一部重なるようシリコン窒化膜(酸化防止膜)109を形成し、該素子領域上に該酸化防止膜をマスクとして、該複数の半導体素子のうちの所定サイズの半導体素子で必要となる熱酸化膜の厚さより厚い熱酸化膜110を形成する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物の偏析に起因する、ドレイン領域と空乏層との間のリーク電流の発生を抑制することが可能な半導体素子を含む半導体装置を提供する。

【解決手段】本半導体装置は、主表面を有する半導体基板SUBと、主表面上に形成された、論理回路を構成するコアトランジスタと、入出力回路を構成するI/Oトランジスタとを備える。主表面からI/On型トランジスタのn型不純物領域NRの最下部までの距離は、主表面からコアn型トランジスタのn型不純物領域NRの最下部までの距離より長い。主表面からI/Op型トランジスタのp型不純物領域PRの最下部までの距離は、主表面からコアp型トランジスタのp型不純物領域の最下部までの距離より長い。主表面からI/On型トランジスタのn型不純物領域の最下部までの距離は、主表面からI/Op型トランジスタのp型不純物領域の最下部までの距離より長い。

(もっと読む)

半導体装置の製造方法

【課題】1つのチップ内に、高駆動性が求められるpMISFET及び高信頼性が求められるpMISFETの両方を形成してCMOSトランジスタの品質向上をはかる。

【解決手段】Siチャネルを有する第1のpMISFET領域121、Siチャネルを有する第2のpMISFET領域122、及びSiチャネルを有するnMISFET領域123を備えた半導体装置であって、第1のpMISFET領域121に、Siチャネルを挟んで該Siチャネルに第1の圧縮歪みを与える第1のSiGe層321が埋め込み形成され、第2のpMISFET領域122に、Siチャネルを挟んで該Siチャネルに第1の圧縮歪みとは大きさの異なる第2の圧縮歪みを与える第2のSiGe層322が埋め込み形成されている。

(もっと読む)

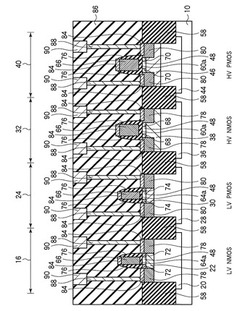

半導体装置の製造方法

【課題】半導体装置の製造方法において工程数の削減を図ること。

【解決手段】領域HVp、LVn、LLnに第1〜第3のゲート電極36a〜36cを形成する工程と、領域LVnを覆い、かつ、領域HVpと領域LLnを露出するマスクパターン40を形成する工程と、マスクパターン40をマスクにしたイオン注入でp型ソースドレインエクステンション41とp型ポケット領域42を形成する工程と、マスクパターン40をマスクにしたイオン注入でn型ソースドレインエクステンション45を形成する工程と、領域HVpと領域LLnを覆い、かつ、第2の領域LVnを露出するマスクパターン52を形成する工程と、マスクパターン52をマスクにしてインジウムをシリコン基板1にイオン注入し、p型ポケット領域54を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの耐圧を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極18cと、ゲート電極の一方の側の半導体基板に形成された第1導電型のドレイン領域54aと、ゲート電極の他方の側の半導体基板に形成された第1導電型のソース領域54bと、ドレイン領域からゲート電極の直下に達する第1導電型の第1の不純物領域56と、ソース領域と第1の不純物領域との間に形成された、第1導電型と反対の第2導電型の第2の不純物領域58とを有し、ゲート電極は、第1導電型の第1の部分48aと、第1の部分の一方の側に位置する第2導電型の第2の部分48bとを含み、ゲート電極の第2の部分内に、下端がゲート絶縁膜に接する絶縁層24が埋め込まれている。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】LSI中の高耐圧MOSFETを含む高耐圧回路は、純粋な内部回路と異なり、外部との関係で動作電圧が高い状態で固定されているため、通常のように、低電圧化による微細化が適用できない。このため、内部回路部の低電圧化に伴って、ますます、チップ内の占有面積を肥大化させる結果となっている。この問題について、本願発明者等が、各種の対策について評価したところによると、CMOSFET回路構成およびデバイス構成との適合性等の問題がネックとなっていることが明らかとなった。

【解決手段】本願発明は、各チャネル表面に波状起伏が設けられたNチャネル型およびPチャネル型MISFETを有する半導体集積回路装置において、Pチャネル型MISFETのチャネル表面に設けられた波状起伏に比べて、Nチャネル型MISFETのチャネル表面に設けられた波状起伏のピッチを狭くしたものである。

(もっと読む)

固体撮像装置及びその製造方法

【課題】周辺論理回路領域を微細化し、かつ画素特性の劣化を防止する固体撮像装置及びその製造方法を提供する。

【解決手段】本実施形態によれば、固体撮像装置の製造方法は、複数の単位画素領域を有する撮像領域と、撮像領域の周辺に設けられた周辺論理回路領域とを備える固体撮像装置の製造方法である。この方法は、半導体基板上に第1膜厚の電極膜及びブロック膜を形成する工程と、単位画素領域のトランジスタのゲート電極に対応した第1レジストパターンをマスクとして前記ブロック膜を除去し、前記電極膜を薄くする工程と、周辺論理回路領域のトランジスタのゲート電極に対応した第2レジストパターン及び前記ブロック膜をマスクとして前記電極膜を除去する工程と、を備える。

(もっと読む)

DCDCコンバータ、電源回路及び半導体装置

【課題】電力変換効率の向上を実現するDCDCコンバータの提供を目的の一とする。

【解決手段】出力電力を制御するためのスイッチング素子として機能するトランジスタが、通常のゲート電極に加えて、閾値電圧を制御するためのバックゲート電極を備える。そして、DCDCコンバータから出力される出力電力の大きさに従って、バックゲート電極に与える電位の高さを制御するための、バックゲート制御回路を備える。バックゲート制御回路により、バックゲート電極に与える電位を制御することで、出力電力が大きい場合にはオン抵抗が下がるように閾値電圧を調整し、出力電力が小さい場合にはオフ電流が下がるように閾値電圧を調整することができる。さらに、スイッチング素子として機能するトランジスタが、オフ電流の極めて小さい絶縁ゲート電界効果型トランジスタである。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第2導電型のソース領域、第2導電型のドレイン領域、及び、第1導電型のボディ領域と、第2ゲート絶縁膜と、第2ゲート電極と、を含む第2トランジスターと、を具備し、第1トランジスターの第2導電型のボディ領域は、第2トランジスターの第2導電型のソース領域及び第2導電型のドレイン領域の内の一方に接続されている。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

半導体装置及びその製造方法

【課題】動作電圧やしきい値電圧が相異なり、高誘電率ゲート絶縁膜/メタルゲート電極構造を有するP型MISFETを共通の基板上に混載可能にする。

【解決手段】半導体装置は、半導体基板100と、半導体基板100のうち第1のTr領域内に位置する領域に形成された第1の活性領域103aと、半導体基板100のうち第2のTr領域内に位置する領域に形成された第2の活性領域103bと、第1の活性領域103a上に形成された第1のP型MISFET150aと、第2の活性領域103b上に形成された第2のP型MISFET150bとを備えている。第1のP型MISFET150aは、ゲルマニウムを含有する半導体で構成された第1の半導体層104と、シリコンで構成された第2の半導体層105とを備えている。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】TXシャントトランジスタSH(TX)を構成するMISFETQN1〜MISFETQN5において、GND端子に近い側に接続されたMISFETQN5から送信端子TXに近い側に接続されたMISFETQN1になるに連れて、ゲート幅Wgが大きくなるように構成されている。

(もっと読む)

半導体装置及びそのレイアウト作成方法

【課題】半導体装置及びその製造方法において、ゲート電極部の幅及びゲート電極部からの突き出し長のばらつきを低減する。

【解決手段】半導体装置は、ゲート電極部及び突き出し部を有する実パターン431と、実パターン431に並んで配置されるダミーパターン433とを含む複数のラインパターンを備える。2つのダミーパターン433と、これらに挟まれ且つ実パターン432を含むラインパターンとにより、同一間隔を空けて並走するラインパターン並走部が構成される。ラインパターン並走部の各ラインパターンは、同一の幅を有すると共に、互いに実質的に面一なライン終端部414を有する。各ライン終端部414の延長線上に、同一の終端部間距離403を空けて、ライン終端部均一化ダミーパターン420が形成される。ライン終端部均一化ダミーパターン420は、ラインパターンと同一幅で且つ同一間隔に形成された複数のライン状のパターンを含む。

(もっと読む)

81 - 100 / 639

[ Back to top ]