Fターム[5F048BB03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 形状 (2,378) | ゲート長(幅)の異なる複数MOS (639)

Fターム[5F048BB03]に分類される特許

161 - 180 / 639

半導体装置

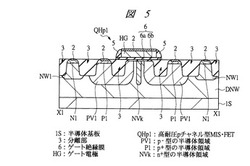

【課題】高耐圧の電界効果トランジスタを有する半導体装置のキンク現象を抑制または防止する。

【解決手段】高耐圧pMISQHp1のチャネル領域のゲート幅方向の両端の溝型の分離部3と半導体基板1Sとの境界領域に、高耐圧pMISQHp1のソースおよびドレイン用のp+型の半導体領域P1,P1とは逆の導電型のn+型の半導体領域NVkを、高耐圧pMISQHp1の電界緩和機能を持つp−型の半導体領域PV1,PV1(特にドレイン側)に接しないように、そのp−型の半導体領域PV1,PV1から離れた位置に配置した。このn+型の半導体領域NVkは、溝型の分離部3よりも深い位置まで延在されている。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置

【課題】チャネル形成領域が素子分離領域から受けるストレスを、チャネル幅方向において均一化させる。

【解決手段】素子分離領域2と、素子分離領域2によって囲まれる、素子形成領域3とを具備する。素子形成領域3の外周形状は、第1方向に沿って延びる第1辺を有する。素子形成領域3は、第1トランジスタ領域6−1と、2方向において第1辺と第1トランジスタ領域6−1との間にあたる位置に配置された、第2トランジスタ領域6−2と、第1方向における第2トランジスタ領域6−2の側方に配置された、ダミー領域7とを備える。第1トランジスタ領域6−1は、第1チャネル形成領域4−1を有する。第2トランジスタ領域6−2は、第2チャネル形成領域4−2を有する。第1チャネル形成領域4−1は、第2チャネル形成領域4−2と非対向である非対向領域14を有する。ダミー領域7は、第2方向において非対向領域14と対向する。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、素子間の耐圧を高めることを目的とする。

【解決手段】シリコン基板10に第1、第2素子分離絶縁膜13a、13bを形成する工程と、シリコン基板10に形成された第1絶縁膜21を介して、第1領域I、第2領域II、及び4領域IVに、第1導電型の第1不純物をシリコン基板の第1の深さD1にまで注入する工程と、シリコン基板10に形成され、且つ第1絶縁膜21よりも薄い第2絶縁膜30を介して、第3領域IIIに、第2導電型の第2不純物を、シリコン基板10の第2の深さD2にまで注入する工程と、第3領域IIIに、第2導電型の第3不純物を、第2の深さD2よりも浅い第3の深さD3にまで注入する工程と、第3領域に、第1トランジスタTRn(1)を形成する工程と、第4領域に、第2トランジスタTRp(low)を形成する工程とを有する半導体装置の製造方法による

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISトランジスタとPMISトランジスタの閾値電圧を同時に低減できる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板10に形成された第1の活性領域10a上に高誘電体を含む第1のゲート絶縁膜17aと、金属材料を含む第1のゲート電極18aとを形成し、基板10に形成された第2の活性領域10b上に高誘電体を含む第2のゲート絶縁膜17bと、金属材料を含む第2のゲート電極18bとを形成する工程と、第1のゲート絶縁膜17aの端部と第2のゲート絶縁膜17bの端部とに負の固定電荷を導入する工程と、第1のゲート絶縁膜17aの端部を除去する工程とを備えている。

(もっと読む)

半導体素子およびその製造方法

【課題】半導体素子の低オン抵抗化を実現し、全体の製造工程数を低減する半導体素子およびその製造方法を提供すること。

【解決手段】ソース・ドレイン領域を形成する際のイオン注入時に、低耐圧横型トレンチMOSFETでは、ドレイン形成用の開口部がトレンチ側壁から離れ、ソース形成用の開口部がトレンチ側壁に達し、トレンチ横型パワーMOSFETでは、ソース形成用の開口部がトレンチ側壁から離れ、ドレイン形成用の開口部がトレンチ側壁に達するパターンのマスクを用いる。このマスクを用いて、高ドーズ量および低加速電圧で行うイオン注入と、低ドーズ量および高加速電圧で行うイオン注入を連続して行うことによって、低耐圧横型トレンチMOSFETのLDD領域と、トレンチ横型パワーMOSFETのLDD領域とを同時に形成する。

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性を向上させる。特に、nチャネル型のMOSFETにおけるVthのローカルばらつきAvtを低減させる。

【解決手段】co−impla技術を用い、nチャネル型のMOSFETのエクステンション領域9aに窒素をシリコン基板1の主面に対して垂直もしくは垂直に近い角度(0〜3度)で打ち込むことにより、窒素が打ち込まれて形成された欠陥トラップ層もしくはアモルファス層がアニ−ル後のシリコン基板1表面近傍への不純物のパイルアップを軽減するため、チャネル表面近傍のドーパントの濃度が低減し、シリコン基板1表面近傍における不純物プロファイルの揺らぎ成分が軽減される。その結果、チャネル表面近傍の不純物揺らぎ起因のローカルばらつきを抑制することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に、酸化物半導体層より導電率の高いバッファ層を形成し、該バッファ層の上にソース電極層及びドレイン電極層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】10GHz程度以上のクロック周波数での動作が可能な高速半導体装置の提供。

【解決手段】n−MOSFET100n、p−MOSFET100pを有し、n−MOSFETのチャンネルを形成する第1の領域の表面が(100)面から±10°以内の面または(110)面から±10°以内の面のを有し、p−MOSFETのチャンネルを形成する第2の領域の表面が((110)面から±10°以内の面または(100)面から±10°以内の面のを有し、第1及び第2の領域の各々から各々の両端の前記ソース電極、ドレイン電極の各々までの抵抗を4Ω・μm以下とし、かつ第1の領域と第1のゲート絶縁層との界面及び第2の領域と第2のゲート絶縁層との界面を、各領域のソースからドレインに向かう方向での長さ2nmにおけるピーク・トゥ・バレイが0.3nm以下であるような平坦度とした半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】相異なる動作電圧の第1,第2,第3のMISトランジスタを有する半導体装置において、第1,第2,第3のチャネル拡散層の不純物プロファイルの変動を抑制する。

【解決手段】半導体装置は、第1,第2,第3の活性領域上に第1,第2,第3のゲート絶縁膜13A,13B,14Cを介して形成された第1,第2,第3のゲート電極を有する第1導電型の第1,第2,第3のMISトランジスタを備えている。第1のゲート絶縁膜13Aは、第1のシリコン酸化膜13aと第1の高誘電率絶縁膜15aとからなる。第2のゲート絶縁膜13Bは、第2のシリコン酸化膜13bと第2の高誘電率絶縁膜15bとからなる。第3のゲート絶縁膜14Cは、第3のシリコン酸化膜14cと第3の高誘電率絶縁膜15cとからなる。第2のシリコン酸化膜13bは、第1のシリコン酸化膜13aと同じ膜厚を有し、且つ、第3のシリコン酸化膜14cよりも厚い膜厚を有している。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲上に少なくとも一部に接して第1のゲート絶縁膜が存在し、第1のゲート絶縁膜に第1のゲート電極の一面が接し、該第1のゲート電極の他面に第2のゲート絶縁膜が接し、第2のゲート絶縁膜に少なくとも第2の半導体層が接して、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第2の半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第2の半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有することを特徴とするインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供する。

【解決手段】第1の島状半導体層137の周囲上に少なくとも一部に接して第1のゲート絶縁膜187が存在し、第1のゲート絶縁膜187に第1のゲート電極178の一面が接し、第1のゲート電極178の他面に第2のゲート絶縁膜187が接し、第2のゲート絶縁膜187に少なくとも第2の半導体層141が接して、第1の島状半導体層137の上部に配置された第1の第1導電型高濃度半導体層161と、第1の島状半導体層137の下部に配置された第2の第1導電型高濃度半導体層162と、第2の半導体層141の上部に配置された第1の第2導電型高濃度半導体層154と、第2の半導体層141の下部に配置された第2の第2導電型高濃度半導体層156と、を有するインバータを用いてSRAMを形成する。

(もっと読む)

制御可能なサージ電流耐性を有するパワースイッチング素子

半導体スイッチング素子は、ワイドバンドギャップパワートランジスタと、前記パワートランジスタと並列に接続されたワイドバンドギャップサージ電流トランジスタと、前記サージ電流トランジスタを駆動するように構成された駆動トランジスタを含む。前記半導体スイッチング素子の、オン状態での出力電流のほぼすべては、前記パワートランジスタのドレイン−ソース電圧が第一の電圧範囲内にあるときには、前記パワートランジスタのチャネルを通って流れる。当該第一の電圧範囲は、例えば、通常動作中に期待されるドレイン−ソース電圧に対応し得る。その一方で、前記半導体スイッチング素子は、さらに、オン状態で、前記パワートランジスタのドレイン−ソース電圧が第二の(より高い)電圧範囲内にあるときには、出力電流が、前記サージ電流トランジスタ、および前記パワートランジスタのチャネルの両方を通って流れるように構成される。 (もっと読む)

半導体装置

【課題】半導体装置において、静電気サージによる絶縁破壊を効果的に防止する。

【解決手段】外部からの入力信号を伝達する入力線と内部ノードN1との間に接続され、且つゲート電極が電源線14に接続されたNMOS16と、接地線15と前記内部ノードとの間に接続され、且つゲート電極が接地線15に接続されたNMOS17と、NMOS16のゲート電極と内部ノードN1との間に接続され、且つゲー卜電極が接地線15に接続されたNMOS22と、電源線14と接地線15との間にダイオード接続されたNMOS24とを有しており、NMOS22のゲート電極からソース電極の配線の接続領域までのN型不純物拡散層の距離は、NMOS24のゲート電極からソース電極の配線の接続領域までのN型不純物拡散層の距離よりも長い。

(もっと読む)

161 - 180 / 639

[ Back to top ]