Fターム[5F048BB04]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904)

Fターム[5F048BB04]の下位に属するFターム

多結晶Si (4,558)

シリサイド (1,994)

金属、合金、金属化合物(シリサイドを除く) (1,529)

異なるゲート電極材料を用いた複数MOS (668)

ゲート絶縁膜材料 (1,843)

Fターム[5F048BB04]に分類される特許

161 - 180 / 312

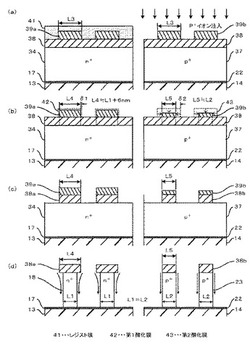

半導体装置の製造方法

【課題】p−MOSトランジスタとn−MOSトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板11の第1領域13、第2領域、14にn型、p型ゲート電極膜34、37を形成する工程と、ゲート電極膜34、37上に第1保護膜38および第2保護膜39を形成する工程と、第2保護膜39に、ゲート電極サイズL1、L2より大きいサイズL3のゲート電極パターンを形成する工程と、第2保護膜39bに選択的に燐イオンを注入し、熱酸化速度が第2保護膜39aより大きくなるようにする工程と、第2保護膜39a、39bを熱酸化し、生成した第1および第2酸化膜42、43を選択的にエッチングして、ゲート電極パターンをスリム化する工程と、スリム化された第2保護膜39a、39bを用いてサイズL1、L2のゲート電極18、23を形成する工程と、を具備する。

(もっと読む)

高性能CMOS技術のための低コストの歪みSOI基板

【課題】エピタキシャル成長及びその後のウェハ接合処理ステップを回避するSSOI構造の製造方法を提供する。

【解決手段】歪み半導体オン・インシュレータ(SSOI)構造体を製造する。SOI基板上に歪み半導体領域を生成するために、歪み記憶技術が用いられる。半導体領域が歪んでいるので、歪み半導体領域上に形成されたトランジスタは、より高いキャリア移動度を有する。(i)薄いアモルファス化層を生成するためのイオン注入と、(ii)アモルファス化層上への高応力膜の堆積と、(iii)アモルファス化層を再結晶させるための熱アニールと、(iV)高応力膜の除去とを含む。再結晶化プロセスの間、SOI基板は応力を受けたので、最終的な半導体層も、応力を受ける。応力の量及び応力の極性(引張又は圧縮)は、高応力膜のタイプ及び厚さによって制御することができる。

(もっと読む)

FINFETデバイスのフィンの上に完全にシリサイド化されたデュアル・ゲートを形成する方法

【課題】 FinFetデバイスのフィンの上に完全にシリサイド化されたデュアル・ゲートを形成する方法を提供すること。

【解決手段】 FinFetデバイスのフィンの上に完全にシリサイド化されたゲートを形成する方法が開示される。本開示は、ポリシリコン層及びポリシリコン・ゲルマニウム層から各々のフィンの上のゲート・スタックをパターン形成し、次に、フィンの一方の上のポリシリコン・ゲルマニウム層を除去する方法を提供する。本開示は、さらに、両方のフィンの上に金属層を形成することと、FinFetデバイスをアニールして、FinFetデバイスの各々のフィンの上に完全にシリサイド化されたゲートを形成することとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 同一半導体基板上にMOSトランジスタとショットキーバリアダイオードを備えてなる半導体装置であって、その装置規模を従来のものと比較して更に縮小させる。

【解決手段】 半導体基板2上に、第1導電型の第1ウェル3、第1導電型とは異なる第2導電型の第2ウェル4、及び第2導電型の第3ウェル5を備える。第2ウェル4上には、第1MOSトランジスタT1、第1ウェル3上には第2MOSトランジスタT2、第3ウェル5上には、第1ショットキーバリアダイオードD1を備える。各素子の電極には高融点金属シリサイド膜(51〜58)が形成される。

(もっと読む)

ゲート電極中のドーパンの相互拡散バリア構造及びその製造方法

【課題】ゲート電極中のドーパンの相互拡散バリア構造及びその製造方法を提供する。

【解決手段】半導体デバイスにおいてゲートのNFET側からゲートのPFET側への拡散を低減する又は防止さえする構造、同様にその製造方法が開示される。拡散バリアは、NFETとPFETとの間のN/P境界のところの共有ゲート中に形成される。拡散バリアは、1又は複数の種類のイオン、例えば、酸素、窒素、フッ素、シリコン、ゲルマニウム、又はキセノン・イオン(しかし、これらに限定されない)でドープされる。本明細書中で開示されるような拡散バリアを使用することによって、CMOS技術半導体デバイス・ノードにおけるNFET側からPFET側への共通ゲートを通してのイオンの拡散は、大いに低減されることができる又は完全に防止することさえもできる。これは、さらにNFET/PFET対の相対的により高い性能をもたらすことができる。

(もっと読む)

端面センサデバイスの製造方法

【課題】形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な端面センサデバイス及びその製造方法を提供すること。

【解決手段】線状体の端面に、対象からの情報を受容して他の情報として出力する受容部が形成されていることを特徴とする端面センサデバイス。線状体2001は、中止部に中心電極2007を有し、その外周は絶縁膜2008で覆われている。上記線状体2001を用意し、その端面にn型半導体層2004を形成する。次いで、n型半導体層2004上にp型半導体層2003を形成する。これにより、線状体2001の端面にpn接合の受容部(光センサ)が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 nMISFETとpMISFETで素子方向を傾けることなく、各素子の移動度向上をはかる。

【解決手段】 絶縁体上の半導体層にnチャネルMISトランジスタとpチャネルMISトランジスタを形成した半導体装置であって、nチャネルMISトランジスタのチャネルがチャネル長方向に1軸引っ張り歪みを有するSi層10で形成され、pチャネルMISトランジスタのチャネルがチャネル長方向に1軸圧縮歪みを有するSiGe20又はGe層で形成され、各トランジスタの電流方向が共に<110>方向である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】微細化されたゲートを有するCMOSトランジスタにおいて、MOSトランジスタのチャネル不純物濃度を低く維持し、かつ短チャネル効果を抑制する半導体装置及びその製造方法を提供する。

【解決手段】第1のゲート絶縁膜を介して形成され、対向する1対の側壁面上に1対の第1の側壁絶縁膜をそれぞれ担持する第1のゲート電極を有するNMOSトランジスタと、第2のゲート絶縁膜を介して形成され、対向する1対の側壁面上に1対の第2の側壁絶縁膜をそれぞれ担持する第2のゲート電極を有する、前記NMOSトランジスタとともに1対で用いられるPMOSトランジスタと、を備え、前記第2の側壁絶縁膜と前記シリコン基板との距離が、前記第1の側壁絶縁膜と前記シリコン基板との距離よりも大きくなるように構成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】ニッケルシリサイドの耐熱性を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】ゲート領域2、ソース領域4及びドレイン領域5が形成された半導体基板1上にニッケル(またはニッケル合金)6を形成し(図1(A))、第1アニール工程でダイニッケルシリサイド7を形成し(図1(B))、プラズマ処理工程では水素イオンを含有するプラズマにより、水素イオンをダイニッケルシリサイド7またはダイニッケルシリサイド7の下部のゲート領域2、ソース領域4及びドレイン領域5に注入し、第2アニール工程でダイニッケルシリサイド7をニッケルシリサイド8に相変態させる(図1(C))。

(もっと読む)

主電極を含むドープされた金属を含む半導体装置

【課題】良好な半導体装置およびそのような半導体装置を作製するための良好な方法を提供する。

【解決手段】半導体装置は、主電極(4)と主電極(4)に接触した誘電体(3)を含み、主電極(4)は、所定の仕事関数を有する材料と、主電極(4)の材料の仕事関数を予め決められた値に向かって変調する仕事関数変調元素(6)とを含み、更に、主電極(4)は、仕事関数変調元素(6)が誘電体(3)に向かっておよび/または誘電体(3)中に拡散するのを防止する拡散防止ドーパント元素(5)を含む。

(もっと読む)

半導体装置の製造方法

【課題】素子構造部にダメージを与えずに側壁スペーサ膜等を除去し、高集積化された高性能な半導体装置を製造することができる半導体装置の製造方法を提供する。

【解決手段】被処理基体上にGeCOHまたはGeCHからなる第1の薄膜を形成すると、この第1の薄膜の一部を除去する工程と、第1の薄膜の除去された部位を介して被処理基体に所定の処理を施す処理工程と、第1の薄膜を除去する工程とを備えたことを特徴とする。GeCOHまたはGeCHからなる側壁スペーサ膜30を用い、ソース、ドレイン領域形成処理を行った後、これを除去する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】PMOSトランジスタおよびNMOSトランジスタのような導電型が異なる素子において、素子のレイアウト依存性なく面内均一にキャリア移動度の向上を図ることが可能で、これにより電流駆動能力を向上させた高性能な半導体装置を提供することを目的とする。

【解決手段】同一の半導体基板の表面側に、PMOSトランジスタ30pとNMOSトランジスタ30nとが形成された半導体装置において、PMOSトランジスタ30pは、半導体基板に貼り合せ形成された半導体基板の表面層とは異なる面方位(110)Siからなる貼り合せ半導体層7に形成されている。一方、NMOSトランジスタ30nは、半導体基板の表面層を構成する面方位(100)Si−Ge層上にエピタキシャル成長させた面方位(100)Siからなる歪半導体層11に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】不純物注入領域を高濃度に活性化させるとともに、ゲートリーク電流を低減させ得る半導体装置の製造方法を提供する。

【解決手段】浅いソース・ドレインエクステンションを活性化させる際に、nMOSにおいてスパイクRTA(第1のアニール)とこれより昇降温速度の大きい超高速昇降温アニール(第2のアニール)を併用し、pMOSにおいては超高速昇降温アニール(第2のアニール)のみを適用する。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】金属ゲート電極のエッチング条件が、閾値電極を構成する材料が異なっても同一となる金属ゲート電極MOSFETを提供すること。

【解決手段】ゲート酸化膜に接して形成された第1の金属層と第1の金属層の上に形成された第1の低抵抗層とからなる第1のゲート電極を有するnチャネルMOSFETとゲート酸化膜に接して形成された第2の金属層と第2の金属層の上に形成された第2の低抵抗層とからなる第2のゲート電極を有するpチャネルMOSFETとを有する半導体集積回路において、第1の金属層と第2の金属層が異なった仕事関数を有する金属によって構成され、第1の低抵抗層と第2の低抵抗層とが同一の材料からなる多結晶で構成され、第1の金属層と第1の低抵抗層の間に第1の中間層を有し、且つ第2の金属層と第2の低抵抗層の間に第2の中間層を有し、第1の中間層および第2の中間層が組成、粒径、結晶構造、及び配向方向が同一の導電性多結晶膜からなる。

(もっと読む)

インバータ

【課題】製造工程が単純であり、且つ特性が向上したD−インバータ構造を提供する。

【解決手段】本発明は、プラスチック基板に有機半導体を用いてインバータ回路を作製する際、しきい電圧を位置別に制御するため、エンハンスメントタイプ特性を示すボトムゲート有機半導体トランジスタをドライバトランジスタに使用し、空乏タイプ特性を示すトップゲート有機半導体トランジスタを負荷トランジスタに使用する構造及び製造方法を提案する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明では、酸素欠損を低減させ、信頼性を改善した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】第1の発明の半導体装置は、基板と、基板に形成された半導体領域と、半導体領域上に形成され、1種以上の第1金属元素の酸化物で形成された絶縁膜と、絶縁膜上に形成され、酸化物の生成自由エネルギーについて第1金属元素よりも大でありかつ金属状態である第2金属元素、および第1金属元素の酸化物で形成された遷移層と、遷移層上に形成された電極と、電極をゲート長方向に挟む半導体領域に形成されたソース・ドレイン領域とを備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】極めて簡易にn型トランジスタの素子特性を向上させることのできるポリゲートストレス技術を適用してn型トランジスタの素子特性の特性を改善を実現するも、p型トランジスタの特性劣化を確実に防止し、しかも徒に工程数や製造コストの増加をもたらすことのない信頼性の高いCMOSトランジスタを実現する。

【解決手段】第1のポケット領域となるp型不純物のイオン注入により形成されるアモルファス領域が、多結晶シリコン膜13aの下方においてソース側とドレイン側とで離間するような不純物種及び注入条件を用いる。一方、第2のポケット領域となるn型不純物のイオン注入により形成されるアモルファス領域が、多結晶シリコン膜13bの下方においてソース側とドレイン側とで繋がるような不純物種及び注入条件を用いる。そして、ポリゲートストレス技術を実行する。

(もっと読む)

半導体装置

【課題】ランタンアルミニウム酸化物を絶縁膜として用いた半導体装置において、この絶縁膜に積層する電極として必要な特性を満たすと共に、各種半導体装置製造過程を経てもその絶縁膜特性を劣化させることのないゲート電極を見出し、微細化に対応可能なスタック構造を有する半導体装置を提供する。

【解決手段】本発明の一実施形態に係るCMOS回路は、nMISは、ランタンアルミニウム酸化物を用いたゲート絶縁膜19、LaxAl1−x(但し0.21≦x≦0.33)で表されるランタンアルミニウム合金を用いたゲート電極21、及びソース及びドレイン領域35とを具備し、pMISは、ランタンアルミニウム酸化物を用いたゲート絶縁膜19、LaxAl1−xNyHz(但し0.21≦x≦0.33、0.15≦y≦0.5、0≦z≦0.1)で表されるランタンアルミニウム合金を用いたゲート電極21を具備する。

(もっと読む)

半導体装置

【課題】高耐圧でありながらオン抵抗が低く、ターンオフ時間が短く、安定動作が可能な半導体装置を提供する。

【解決手段】この半導体装置1は、ソース、ドレインおよびゲート電極をそれぞれ含むとともに、互いにドレイン領域が接続されるとともに、互いにゲート電極同士が接続されたNMOSFET11およびPMOSFET12を含むインバータ14と、コレクタ(C)、ベース(B)およびエミッタ(E)を含むとともに、インバータ14の出力がベース(B)に入力されるpnp型のバイポーラトランジスタ13とを備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】エミッタ層にまでシリサイド化反応が進入するのを抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置(バイポーラトランジスタ100)は、拡散層7と、拡散層7の表面上に形成され、金属と半導体との金属半導体化合物からなるコバルトシリサイド膜9aと、拡散層7とコバルトシリサイド膜9aとの間に形成され、コバルトシリサイド膜9aから拡散される金属の透過を抑制する反応抑制層8とを備える。

(もっと読む)

161 - 180 / 312

[ Back to top ]